你有没有想过,在AI数据中心里,海量数据如洪水般涌动时,一个小小的过孔竟能成为信号传输的“瓶颈杀手”?它不只是个孔,而是决定光模块能否稳定跑满224Gbps甚至更高速度的隐形英雄。今天,我们就来拆解高速光模块PCB过孔设计的痛点与优化秘籍,帮助你避开常见陷阱,提升模块性能。

光模块PCB上的过孔,本质上是多层板间信号跳转的通道。在800G及1.6T时代,PAM4编码下单波速率高达200Gbps,过孔的寄生效应被无限放大。传统通孔会留下长长的“via stub”(残桩),像天线一样引发谐振,导致信号反射和插入损耗飙升。测试显示,一个未优化的via stub在112G SerDes下,可造成超过2dB的额外损耗,直接拉低眼图开口。

更棘手的是热管理。光模块功率密度暴增,DSP和光引擎发热严重,如果过孔设计不当,热量无法有效导走,容易导致温度梯度过大,影响激光器波长稳定性。数据显示,1.6T模块在高负载下,局部温度超80°C时,误码率可上升10倍。

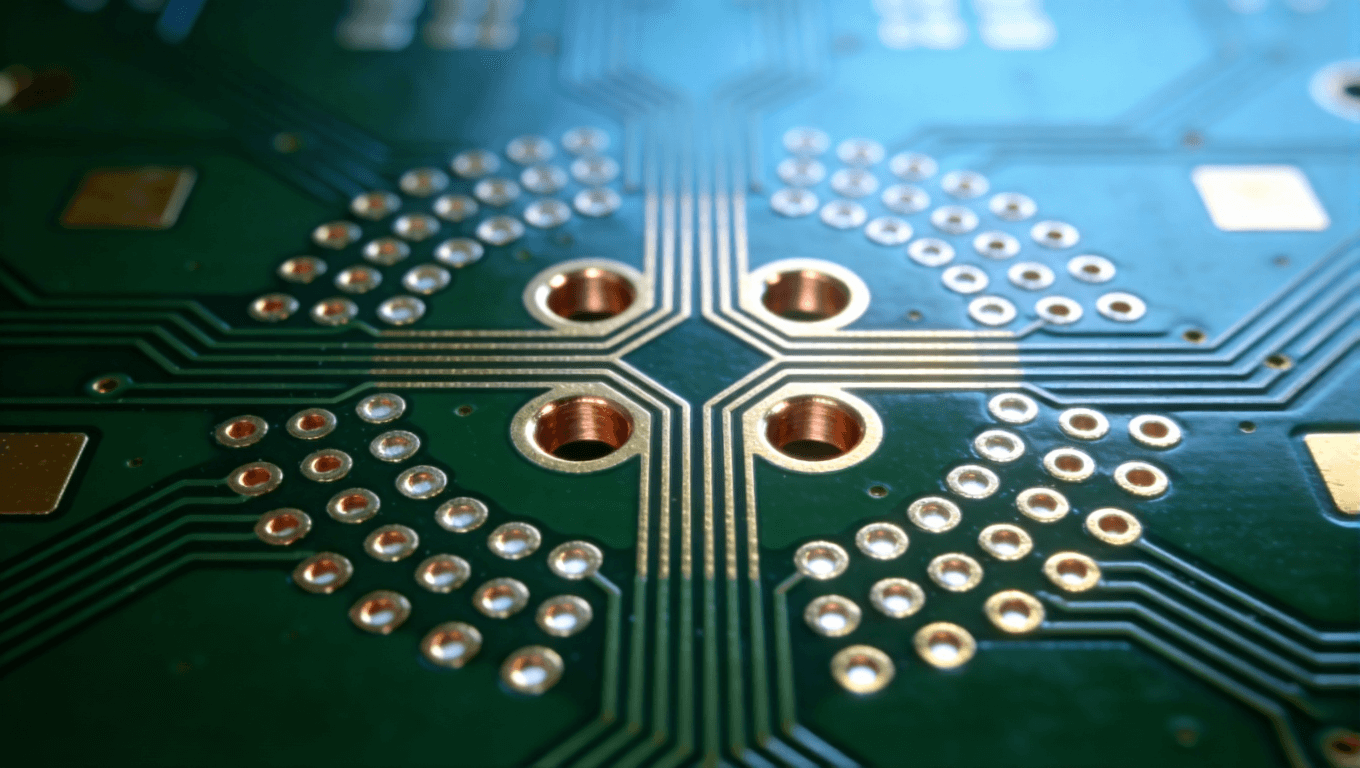

制造层面,过孔密集区还易引发钻孔偏差或孔壁粗糙,放大高频皮肤效应。激光钻孔虽精准,但对材料敏感,稍有不慎就良率下滑。这些痛点,让许多设计师在从800G向1.6T升级时卡壳。

先看反射问题:通孔残桩过长是元凶。行业测试表明,当stub长度超过0.5mm时,在56GHz频段会产生明显谐振峰,插入损耗直线上升。许多早期800G设计就是因为忽略back drilling(背钻),导致信号完整性不达标。

串扰也是大敌。高密度布局下,差分过孔间距若小于0.3mm,邻近通道串扰可达-30dB以下,远低于协议要求。加之参考平面被过孔阵列打碎,返回路径不连续,进一步恶化EMI。

热过孔设计更需谨慎。盲目密集布置虽能导热,但会占用布线空间,还可能造成短路风险。实际案例中,有些模块因热过孔与信号过孔混排,导致局部短路,批量返工。

最后,成本与工艺平衡难把握。激光盲孔先进但贵,机械通孔便宜却性能差。2025年数据显示,1.6T光模块PCB中,过孔相关工艺占总成本15%以上,优化不当直接推高单价。

优化从3D电磁仿真起步。用HFSS或CST建模过孔结构,重点评估stub长度、反焊盘尺寸和间距。实战经验:将via stub控制在0.2mm以内,通过back drilling移除多余部分,可将谐振抑制到-40dB以下。

盲孔与埋孔是首选。激光钻盲孔直径0.1-0.15mm,结合HDI叠层,缩短信号路径20%。对于差分信号,采用对称过孔对,间距匹配走线(0.15-0.2mm),并环绕接地过孔形成屏蔽笼,串扰降至-45dB。

热管理技巧:芯片下方布置热过孔阵列,孔径0.3mm,间距0.8-1mm,镀铜后连通底层铜皮。结合埋铜块或铜膏填充,进一步提升导热率。模拟显示,这种设计可降低junction温度15-20°C。

材料升级不可少。转向Megtron 7或M7低损耗板材(Df<0.002),减少介质损耗。叠层对称设计,避免翘曲;薄芯板(<0.1mm)配合多阶盲孔,确保阻抗精准100Ω。

制造端,DFM协同关键。早期引入PCB厂专家,预留背钻裕度(深度公差±0.05mm),并用树脂塞孔+镀铜盖帽,实现via-in-pad,提升密度。

某数据中心项目中,初始1.6T PCB用传统通孔,测试眼图BER高达10^-6,损耗超标。团队切换盲孔+背钻方案,反焊盘优化至孔径1.8倍,添加接地环绕。结果:插入损耗降1.5dB,眼图开口提升30%,功耗减8%。

另一800G案例,热过孔不当导致DSP过热。改用网格热阵列+铜块埋入,温度均匀分布,模块寿命延长50%。这些突破,不仅通过验证,还帮助客户抢占AI市场先机。

随着CPO(共封装光学)普及,过孔需支持光电共存,集成波导与微过孔。AI驱动下,3.2T模块将推过孔直径至0.08mm,结合AI仿真自动优化参数。

可持续趋势下,低损材料与绿色钻孔工艺将主流。未来,过孔可能嵌入传感器,自适应调整阻抗。