凌晨三点,某通信设备厂商的实验室里,硬件工程师李工盯着示波器皱起了眉——新设计的5G基站射频板上,高频信号总是出现异常反射,误码率超标30%。排查了三天,问题最终锁定在PCB(印刷电路板)的阻抗不匹配上。“如果早用阻抗控制板,可能一周前就解决了。”他对着同事苦笑。 这样的场景,在高速电子设计领域并不罕见。当芯片算力突破100Gbps,当5G毫米波、PCIe 5.0等高速接口成为标配,一块普通的PCB早已无法满足需求——阻抗控制板,这个曾被视为“高端定制”的技术,正从幕后走向台前,成为高速电路的“信号保镖”。

什么是阻抗控制板? 通俗来说,它是一种通过设计手段,将PCB上传输线的特性阻抗稳定控制在目标值(如50Ω、75Ω)的特殊电路板。这听起来像给电路加了一道“保险”——确保信号在传输时,能量不会因阻抗突变而反射、损耗或串扰。 但要真正理解它的价值,得先回到电子信号的底层逻辑。电信号在PCB走线中传输时,本质上是在导体周围介质中激发的电磁场。这条“电磁场通道”的阻抗(即特性阻抗Z0),由走线宽度、介质厚度、介电常数(εr)等参数共同决定,公式可简化为: Z0 = √(L/C)(L为单位长度电感,C为单位长度电容) 普通PCB的走线阻抗可能随工艺波动(如蚀刻偏差、层压厚度不均)变化10%-20%,但在10Gbps以上的高速场景中,哪怕1Ω的阻抗偏差,都可能导致信号眼图闭合、数据丢包。阻抗控制板的核心使命,就是通过精准设计,将这种波动压缩到±5%甚至±1%以内。 举个例子:一块支持PCIe 5.0(32Gbps)的服务器主板,若其高速差分线阻抗偏差超过±7%,信号在经过10英寸走线后,眼高会衰减40%,直接导致链路误码率超过10^-12的通信标准。此时,阻抗控制板就是那条“误差不超过0.5Ω的安全通道”。

阻抗控制板的设计,远非“设定一个阻抗值”那么简单。它需要贯穿材料选择、结构布局、工艺控制的全流程,核心要解决三个问题:

设计第一步,是根据信号速率、芯片接口要求(如USB4、DDR5)确定目标阻抗。以最常见的50Ω单端线为例,工程师需要用HFSS、Ansys SIwave等工具,建立传输线模型,输入介质介电常数(如FR4的εr≈4.5,高速材料Megtron 7的εr≈3.6)、走线宽度(W)、介质厚度(H)、铜箔厚度(T)等参数,反推是否符合Z0要求。 但实际中,材料参数可能因温湿度变化(如FR4的εr随温度升高上升0.1-0.3),走线可能因层压偏移导致H偏差——这些动态因素,让“理论计算”必须与“实测校准”结合。某头部PCB厂商的经验是:先通过仿真给出初始值,再制作样板测试,根据实测阻抗调整线宽或介质厚度,最终将偏差控制在±3%以内。

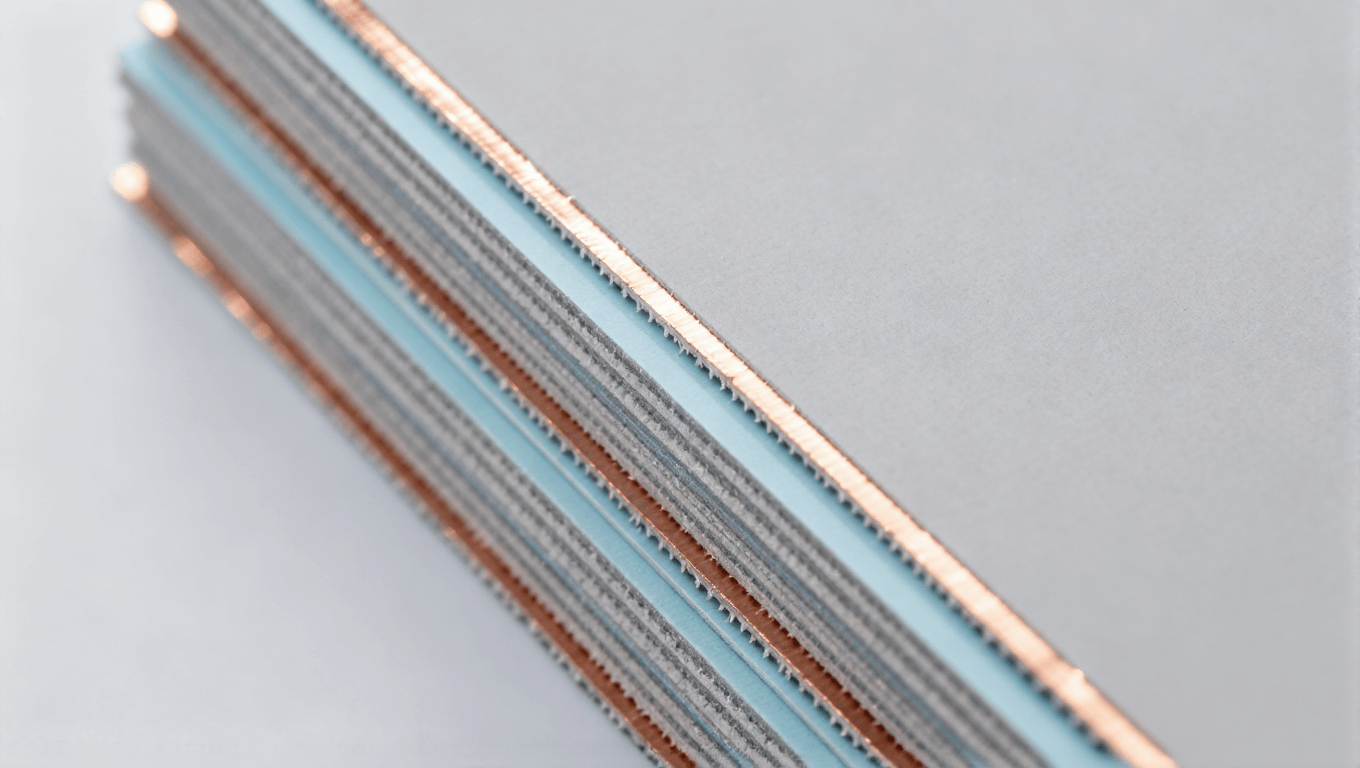

高速电路对阻抗的需求,倒逼材料革命。传统FR4(玻璃纤维环氧树脂)的介电常数波动大、高频损耗高(Df≈0.02),已无法满足10Gbps以上场景。取而代之的是高速材料,如:

罗杰斯(Rogers)系列:如RO4350B(εr=3.66,Df=0.004),介电常数公差±0.05,稳定性极强;

MPI(改性聚酰亚胺):低吸水率、低损耗,适用于5G毫米波天线;

碳氢树脂(Hydrocarbon):高频下Df<0.002,用于卫星通信高频板。

但高性能材料也意味着更高成本。如何在阻抗精度与成本间找到平衡?某通信设备厂商的策略是:核心信号(如射频链路)使用罗杰斯材料,非关键信号(如电源层)用改良FR4,既保证性能又降低整体成本。

即使设计完美,制造环节的偏差也可能毁掉一切。阻抗控制板的工艺难点集中在:

线宽精度:目标线宽10mil(0.254mm),实际蚀刻偏差需<±0.5mil,否则阻抗偏差可达±2Ω;

层压一致性:多层板的介质层厚度(H)偏差需<±5%,否则上下层阻抗会相互干扰;

表面处理:沉金、OSP(有机可焊性保护)等工艺会改变铜面粗糙度,进而影响高频阻抗(粗糙度每增加1μm,5GHz阻抗偏差约0.5Ω)。

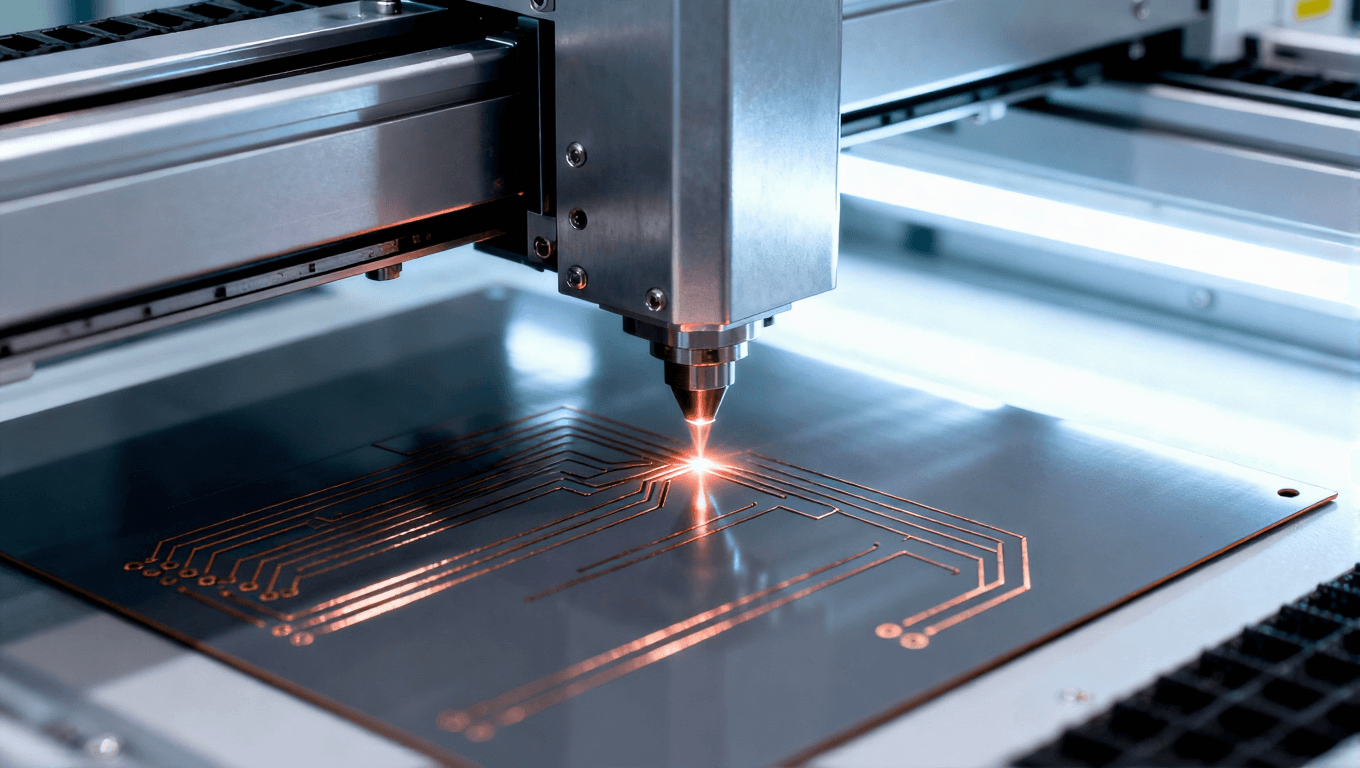

国内高端PCB厂的解决方案是:引入激光直接成像(LDI)替代传统曝光,线宽精度提升至±0.3mil;采用真空层压机,介质厚度偏差控制在±3%;表面处理前增加等离子清洗,减少铜面氧化导致的粗糙度波动。

阻抗控制板的普及,本质是电子系统对“速度”与“可靠性”的双重追求。以下三个场景,最能体现其不可替代性:

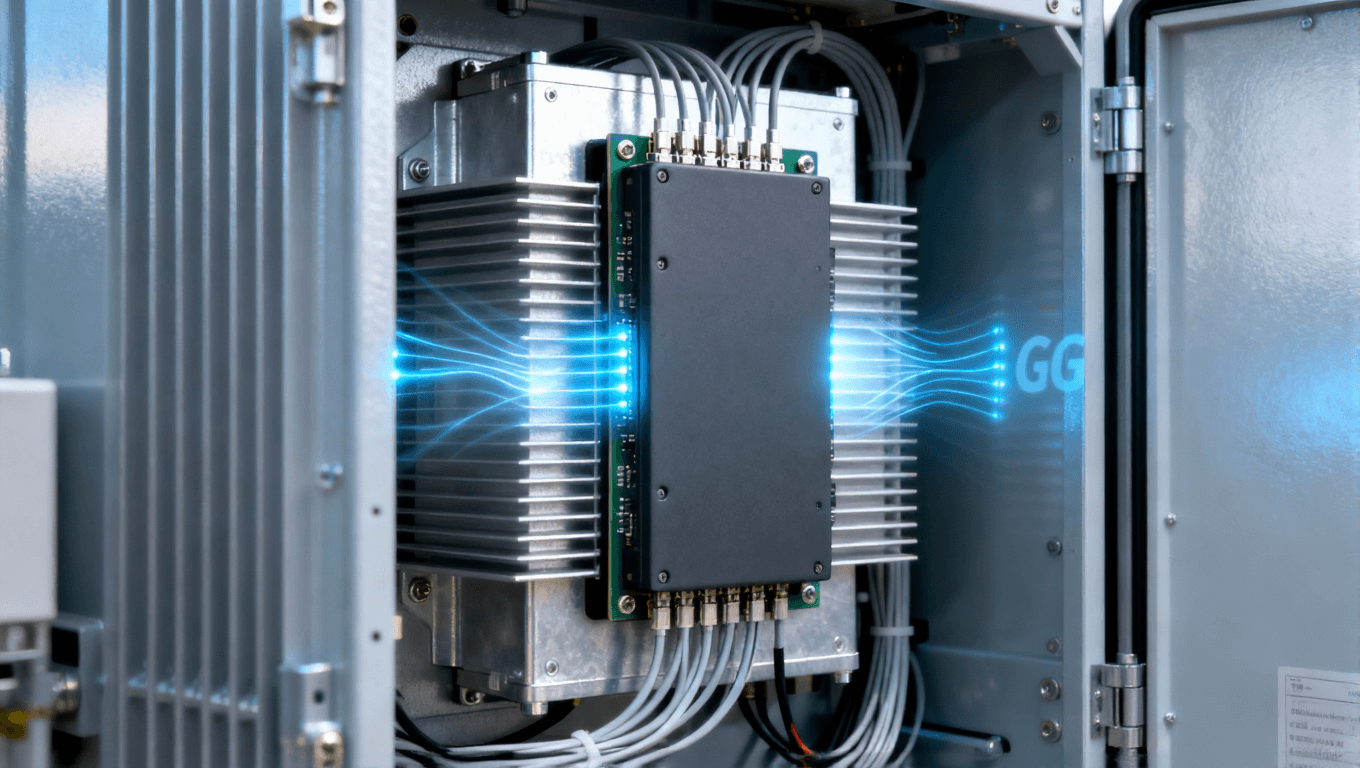

5G基站的AAU(有源天线单元)中,射频前端到基带处理器的信号速率高达25Gbps-100Gbps。毫米波(28GHz/39GHz)信号对阻抗极其敏感——0.1mm的走线偏移,可能导致3dB以上的信号衰减。某5G设备商测试显示:使用阻抗控制板(偏差±2Ω)的AAU,覆盖范围比普通板提升15%,误码率降低至10^-12以下。

服务器主板的CPU到GPU链路,已从PCIe 4.0(16Gbps)升级到PCIe 5.0(32Gbps),未来还将支持CXL(Compute Express Link)实现内存池化。这些高速接口要求差分线阻抗严格匹配100Ω(±5%),否则链路的插入损耗会增加,导致带宽利用率下降。某头部服务器厂商验证:阻抗控制板的链路损耗比普通板低20%,可支持更长的PCB走线(从15英寸延长至20英寸)。

自动驾驶的激光雷达、4D毫米波雷达,需要处理10Gbps-40Gbps的点云数据。汽车级PCB不仅要耐温(-40℃~125℃)、抗震动,还要保证阻抗稳定——高温下材料膨胀导致的线宽变化,可能让阻抗偏差超出雷达接收端的容限。某车载雷达厂商的测试表明:阻抗控制板的雷达探测距离比普通板远30米,目标识别率提升25%。

关于阻抗控制板,行业内存在一些误解:

误区1:只有高频板才需要阻抗控制 实际上,只要信号速率超过5Gbps(如DDR4-3200的内存总线),就需要考虑阻抗匹配。某消费电子厂商曾因忽略DDR4的阻抗控制,导致手机内存频繁报错。

误区2:阻抗值越高越好 阻抗值(如50Ω、75Ω、100Ω)由芯片接口标准决定(如USB3.0差分线要求90Ω)。盲目提高阻抗值,反而可能导致反射加剧。

误区3:仿真过就没问题 仿真只是预测,制造环节的工艺波动必须通过首件测试(FAI)验证。某厂商曾因层压厚度偏差未检测,导致批量板阻抗超差,损失百万订单。

从5G基站到自动驾驶,从数据中心到消费电子,高速信号的“奔跑”从未如此依赖一块PCB的阻抗控制。它不是简单的“特殊工艺”,而是电子系统可靠性的基石——就像人体血管需要稳定的血压,电子信号也需要稳定的阻抗来保障“血液循环”。 对于电子工程师而言,理解阻抗控制板,不仅是掌握一项技术,更是读懂高速时代的“信号语言”。而对于企业来说,能否做好阻抗控制板,将直接影响其在5G、AI、汽车电子等赛道的竞争力。