在5G通信、毫米波雷达等高频应用中,射频前端作为信号收发的核心枢纽,其PCB布局直接决定系统的整体性能。实践表明,不合理的布局会导致信号衰减增加超过30%,甚至引发自激振荡,严重影响系统稳定性。射频电路独特的分布参数特性(如趋肤效应、耦合效应)要求布局设计在信号完整性、电磁兼容性(EMC)与热管理三者之间达到平衡,这与低频数字电路布局有着本质的区别。

布局设计面临两大核心挑战:

频率提升:5G/6G技术推动工作频率向毫米波频段(30GHz+)延伸,导致信号波长缩短至毫米级,布局精度要求提升至±5μm。

干扰问题:射频模块与数字电路的密集集成增加了系统间的干扰,导致信号完整性问题更加严重。

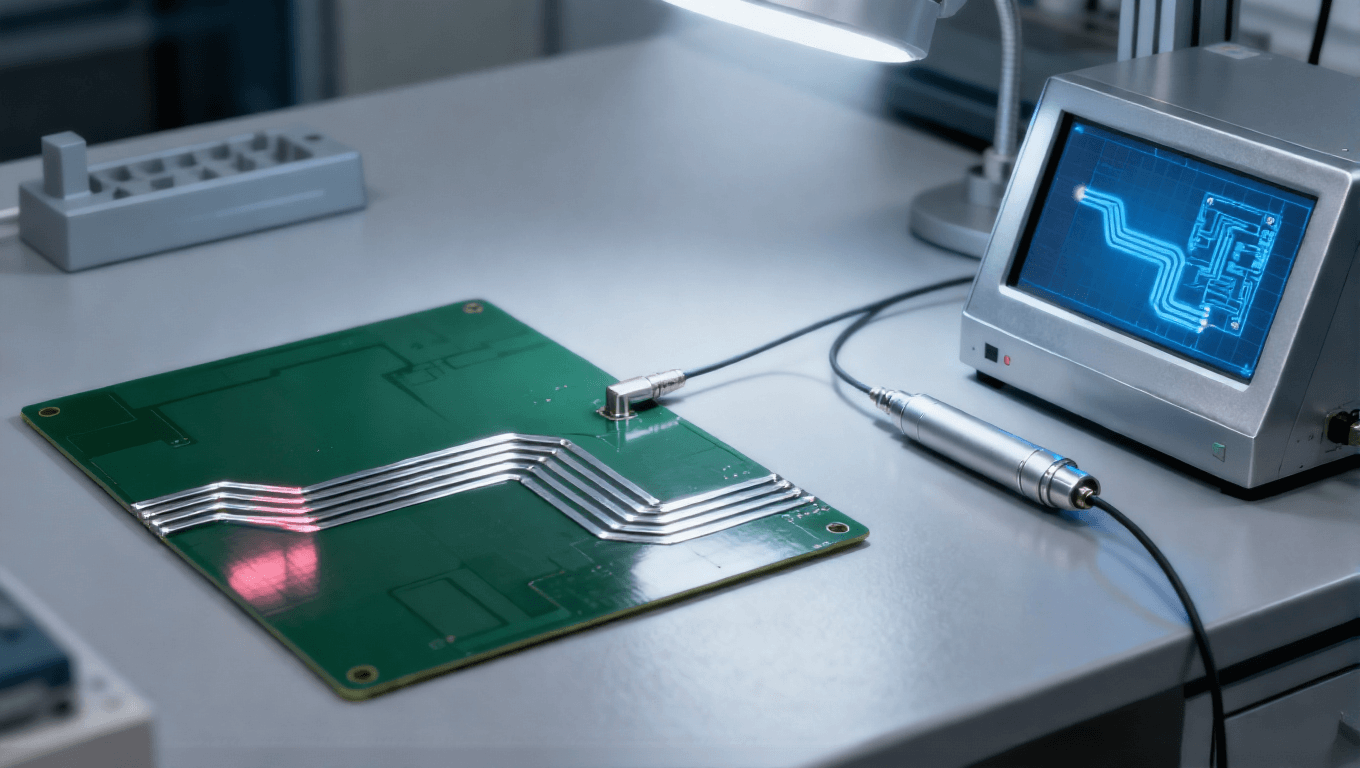

1. 拓扑结构设计:射频链路优先采用 “一字形” 布局,按输入→放大→滤波→输出的顺序排列元器件,间距严格遵循原理图要求(如 π 型匹配网络元件间距需<3mm)。受空间限制时可采用 “L 形” 布局,但需避免 “U 形” 布局;若必须采用,需通过隔腔屏蔽将输入输出端隔离,间距≥15mm。

2. 传输线控制:信号线长度需≤信号波长的 1/16(如 28GHz 信号最长走线仅 0.67mm),拐角采用 45° 斜切或圆弧处理,减少阻抗突变(直角拐角等效电容增加 20%)。

1. 功能分区布局:将电路划分为射频前端(PA/LNA)、本振(LO)、数字控制三大区域,高功率模块(如 PA)与敏感模块(如 LNA)间距需>信号波长的 1/2(2.4GHz 场景下≥62mm)。

2. 介质隔离措施:敏感信号(如 VCO 输出)与干扰源之间设置接地隔离带,宽度≥3 倍线宽;多层板中利用内层地平面实现垂直隔离,避免同层交叉布线。

1. 接地系统设计:射频区域采用多点接地方式,铺铜间隙控制在 20-40mil,接地过孔间距≤信号波长的 1/20(10GHz 场景下≈1.5mm),且呈交错排列。腔壳与 PCB 接触处需开窗处理,通过两排交错接地孔实现低阻抗连接。

2. 电源去耦策略:高频去耦电容(100pF~1nF)需紧邻 IC 电源引脚,接地端直接通过过孔连接地平面,避免引线电感引入噪声。电源平面采用长条状设计,与射频信号线平行排布,交叉处采用垂直十字结构。

1. 层叠结构设计:推荐 4 层及以上设计方案:顶层(射频信号)、中间层(地 / 电源)、底层(辅助信号)。毫米波场景下采用 6 层结构,增加屏蔽地层减少辐射损耗。层间布线方向垂直交叉(顶层水平、底层垂直),降低信号耦合。

2. 基板材料选型:优先选用低损耗基材,如 Rogers RO4003C(介电常数 3.55,损耗正切 0.0027)或 Taconic RF-35,替代高频损耗较大的 FR-4。5GHz 以上场景选用 0.508mm 厚基板,毫米波场景采用超平铜箔(Rz<2μm),降低趋肤效应损耗 30%。

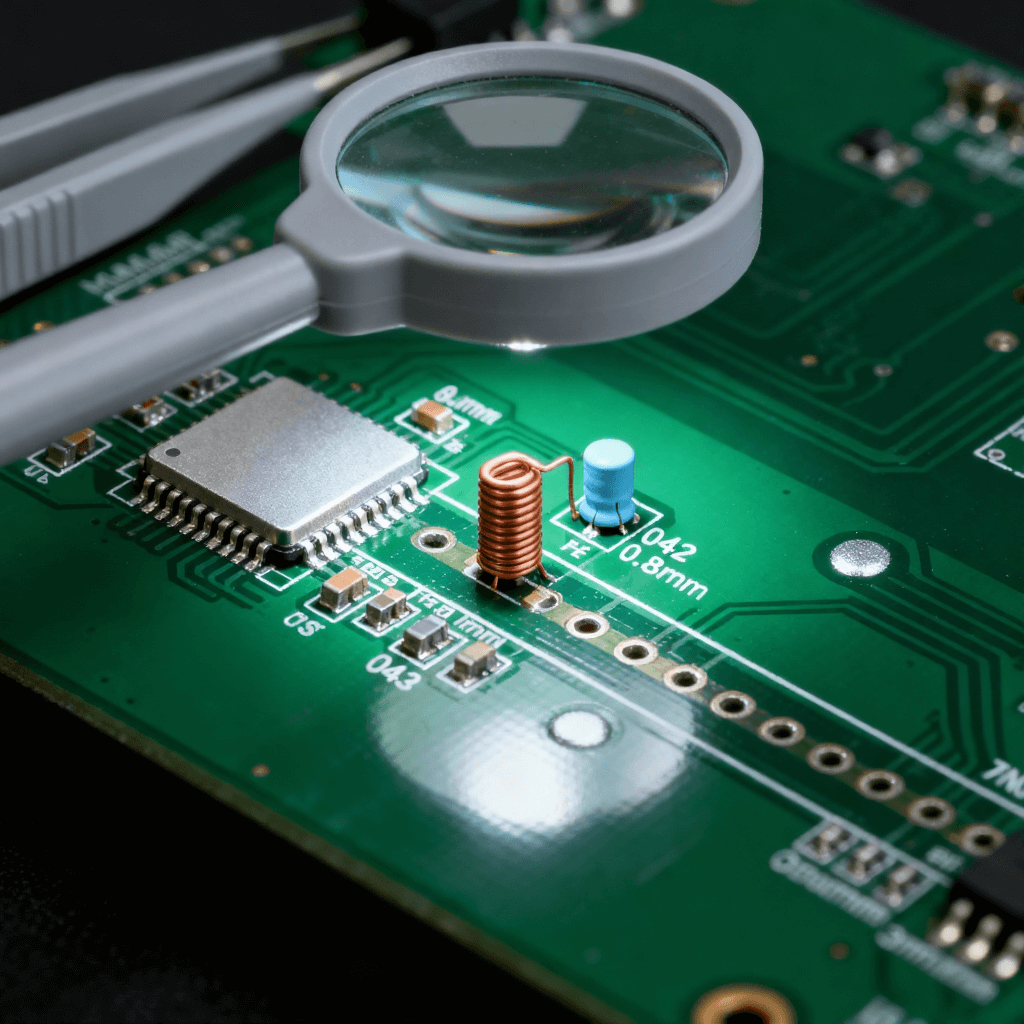

1. 有源器件布局:射频芯片外围电路严格参照 datasheet 要求,匹配元件(电感、电容)贴近引脚放置,引线长度<1mm。功率器件(如 PA)下方设置铜柱散热,热阻可从 40℃/W 降至 8℃/W。

2. 无源器件优化:偏置电路的馈电电感与射频通道垂直放置,减少互感干扰;天线馈点周围预留 3mm 净空区,避免寄生电容影响辐射效率。

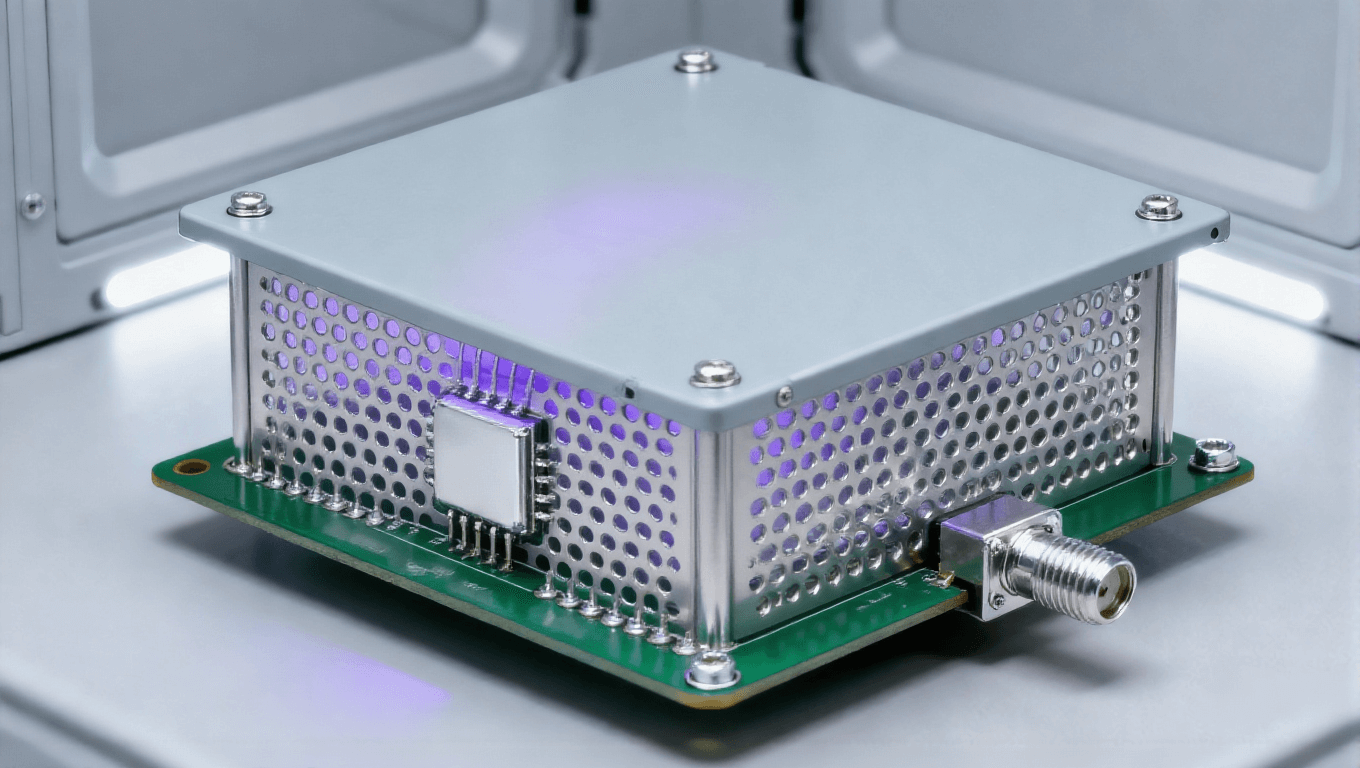

1. 电磁屏蔽措施:敏感区域采用 “过孔墙 + 金属罩” 构成法拉第笼,过孔间距≤λ/20,隔离度可达 70dB@10GHz 以上。射频信号线采用包地处理,地铜皮上均匀打孔,孔间距<λ/20。

2. 机械防护设计:腔壳四个角及隔腔交叉处必须设置螺钉孔,SMA 连接器旁需额外加设螺钉,防止插拔时 PCB 变形。

1. 前期仿真:利用 ANSYS HFSS 进行三维电磁仿真,优化传输线阻抗与过孔布局,减少设计迭代次数 60%。通过 AI 算法自动生成匹配网络,设计效率提升 40% 以上。

2. 后期验证:制作样板后测试 S 参数(插入损耗、回波损耗)与 EMC 指标,重点核查 1-40GHz 频段的干扰情况,确保辐射泄漏<-50dBm。

问题类型 | 产生原因 | 解决措施 |

信号反射严重 | 阻抗突变(线宽变化、直角拐角) | 采用渐变线宽过渡,拐角改为 45° 斜切;通过仿真校准传输线参数 |

模块间干扰 | 高功率信号耦合至敏感电路 | 增加接地隔腔,拉大 PA 与 LNA 间距至 λ/2 以上;采用分层屏蔽设计 |

接地噪声过大 | 地平面分割、过孔间距过大 | 采用完整地平面,接地过孔间距≤λ/20;关键接地焊盘就近打 3-4 个过孔 |

散热不良 | 功率器件集中且无散热设计 | 器件分散布局,下方设置密集散热过孔;采用铝基板或埋置铜块 |

谐振现象 | 腔体尺寸与信号波长共振 | 边缘添加接地过孔阵列破坏谐振模式;优化腔壳结构避免整数倍波长尺寸 |

AI 驱动的布局工具实现参数化设计:输入工作频率、阻抗要求后,自动生成传输线尺寸、过孔间距与屏蔽方案,Gerber 文件精度可达 5μm。EM 仿真与布局设计实时联动,使毫米波频段设计周期从 3 个月缩短至 2 周。

低温共烧陶瓷(LTCC)技术将滤波器、巴伦等元件集成至 PCB 内部,尺寸缩小至传统方案的 1/10。硅基光刻工艺实现 100GHz 波导结构,精度达 0.1μm,为 6G 太赫兹通信奠定基础。

环保基材(如无铅 ENEPIG 表面处理)替代传统喷锡工艺,平整度提升 10 倍的同时降低污染。异构集成技术使射频前端与基带芯片共封装,布局密度提升 5 倍以上。

1. 射频链路是否采用 “一字形 / L 形” 布局,输入输出端隔离是否达标?

2. 传输线阻抗是否符合 50Ω 要求,拐角是否做 45°/ 圆弧处理?

3. 接地过孔间距是否≤λ/20,地平面是否存在分割?

4. 去耦电容是否紧邻 IC 引脚,接地路径是否最短?

5. 高功率模块与敏感电路间距是否>λ/2,是否采取屏蔽措施?

6. 散热过孔与螺钉孔布局是否满足机械与热管理需求?

7. 是否通过仿真与实测验证信号完整性及 EMC 性能?