摘要:

便携式移动设备是当今半导体集成电路行业的主要发展动力。其对封装的挑战,除电性能的提高外,还强调了小型化和薄型化。层叠封装(PoP)新的趋势,包括芯片尺寸增大、倒装技术应用、超薄化等,进一步增加了控制封装翘曲的难度。超薄封装的翘曲大小及方向与芯片尺寸、基板和塑封层厚度,以及材料特性密切相关。传统的通用封装方案已不再适用,需要根据芯片设计及应用,对封装设计、材料等因素加以优化,才能满足翘曲控制要求。另外,基板变薄后,来自不同供应商的基板可能出现不同的封装翘曲反应,需要加强对基板设计公差及供应链的管控。

1 简介

当今半导体集成电路(IC)的新增长点,已从传统的机算机及通讯产业转向便携式移动设备如智能手机、平板电脑及新一代可穿戴设备。集成电路封装技术也随之出现了新的趋势,以应对移动设备产品的特殊要求,如增加功能灵活性、提高电性能、薄化体积、降低成本和快速面世等。

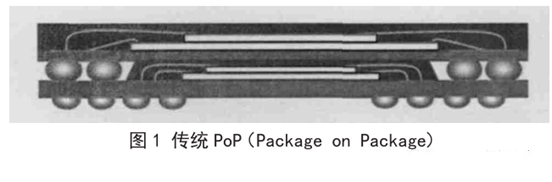

层叠封装(PoP,Package-on-Package,见图 1)就是针对移动设备的 IC 封装而发展起来的可用于系统集成的非常受欢迎的三维叠加技术之一。PoP 由上下两层封装叠加而成,底层封装与上层封装之间以及底层封装与母板(M otherboard)之间通过焊球阵列实现互连。通常,系统公司分别购买底层封装元件和上层封装元件,并在系统板组装过程中将它们焊接在一起。层叠封装的底层封装一般是基带元件,或应用处理器等,而上层封装可以是存储器等。

同传统的三维芯片叠加技术相比,PoP 结构尺寸虽稍大,但系统公司可以拥有更多元件供应商,并且由于 PoP 底层和上层的元件都已经通过封装测试,良率有保障,因此 PoP 的系统集成既有供应链上的灵活性,也有成本控制的优势。事实证明,PoP 为系统集成提供了低成本的解决方案。

为了进一步利用 PoP 技术的优势,系统公司可以同芯片供应商与封装公司合作,对 PoP 底层或上层元件进一步集成,以满足其产品需要。例如,基带芯片和应用处理器芯片可以集成在 PoP 的底层封装里。

随着集成度及电性能要求的进一步提高,以及超薄化的需求,PoP 封装技术也不断发展创新,开始进入新的一代。本文将介绍分析这一领域的最新发展趋势。

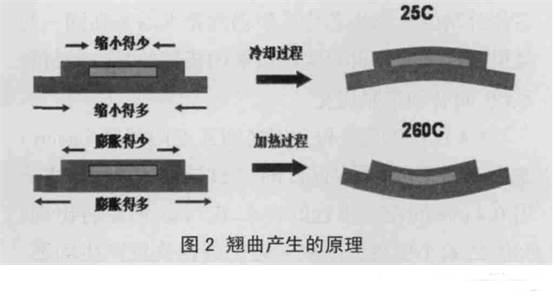

封装技术的进一步超薄化使得封装翘曲成为一大问题。封装中使用了各种不同的材料,如芯片、基板、塑封等,这些材料具有不同的热膨胀系数(CTE,CoefficientofTherm alExpansion)。当整个封装经历温度变化时,例如从封装过程时的高温降到室温,由于各种材料的热膨胀系数不同,伸缩不一致,从而导致封装产生翘曲,图 2 简易地说明了这一原理。当封装变薄后,钢性显著降低,更容易变形,使得翘曲显著加大。

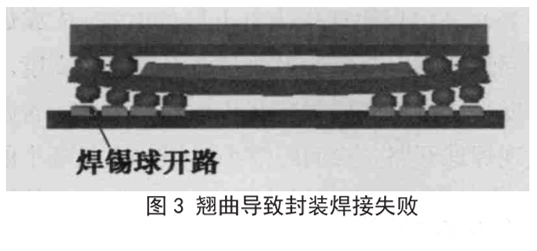

过大的翘曲会使得 PoP封装在表面焊接(SMT)组装过程中,底层封装与母板之间,或者底层和上层封装之间的焊锡球无法连接,出现开路,见图 3。

翘曲已成为影响 PoP 组装良率的关键因素。超薄化的趋势使得翘曲问题更加突出,成为一个阻碍未来 PoP 薄化发展的瓶颈。因此,各种新的技术和材料不断出现,用以降低封装的翘曲。在这篇文章中,我们将介绍翘曲控制方面的发展趋势。文章更进一步从一组超薄 PoP 试验样品,以及其它一些实际产品数据中,分析探讨超薄后可能出现的翘曲大小,以及超薄封装所带来的相应的设计、材料、生产过程中可能出现的问题和挑战。

2 层叠封装(PoP)的发展趋势

新一代层叠封装的发展趋势可以概括为:

(1)IC 集成度进一步提高,芯片尺寸不断加大,芯片尺寸与封装尺寸比例不断提高,使得封装翘曲也随之增加。

(2)对封装的电性能要求进一步提高,倒装芯片技术(flip chip)应用普及,已代替了传统的焊线(wire bond) 技术。更先进的则采用铜柱技术(CopperPillar),以进一步缩小焊点间距。

(3)同一芯片针对不同应用及客户要求采用不同封装尺寸。这使得封装材料也应随之而改变,优化。另一方面,有时客户为了提高 IC 制造良率和产出率,或者应用的灵活性,会把一颗大集成度的系统芯片分割成几颗小芯片,但仍然要求封装在同一封装里。这些都使得封装难以采用传统的统一的材料系统,而必须定制优化。

(4) PoP 底层和上层之间互连的间距(pitch)缩小。传统 PoP 采用 0.5 m m 或以上间距,现在多采用 0.4 m m 间距。不远的将来,0.3 m m 间距将出现。间距的缩小使得上下层互连的焊锡高度产生问题。传统 PoP 采用焊锡球作为上下层的互连,依靠焊锡球在回流液态下自身的表面张力形成焊球高度。这一高度必须大于底层封装芯片和塑封厚度,否则就会出现焊球开路。在间距缩小、焊球直径减小的情况下,这一高度要求难以达到,必须开发新的技术。

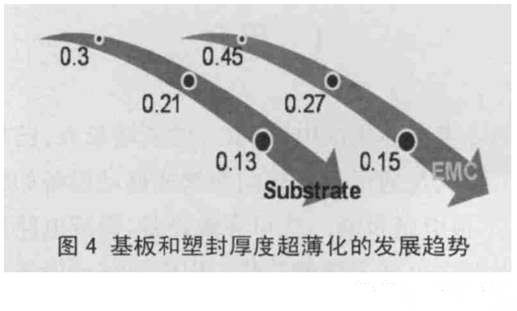

(5)在超薄化趋势下,PoP 封装的各层材料厚度要求越来越薄。图 4 显示了基板(substrate)和塑封(EM C)厚度的薄化趋势。基板厚度已从常见的0.3 m m 薄化到 0.2 m m 左右,甚至 0.13 m m 。而塑封厚度则从 0.28 m m 降至 0.2 m m 和 0.15 m m 。至于芯片本身,厚度也已达 0.1 m m 以下,0.05 m m 芯片也将出现。封装薄化带来的最大问题就是封装翘曲显著增加。许多新的 POP 技术的开发及新材料的应用也是针对降低封装翘曲。

顺应上述趋势,POP 在封装技术和材料使用上也出现新的发展。

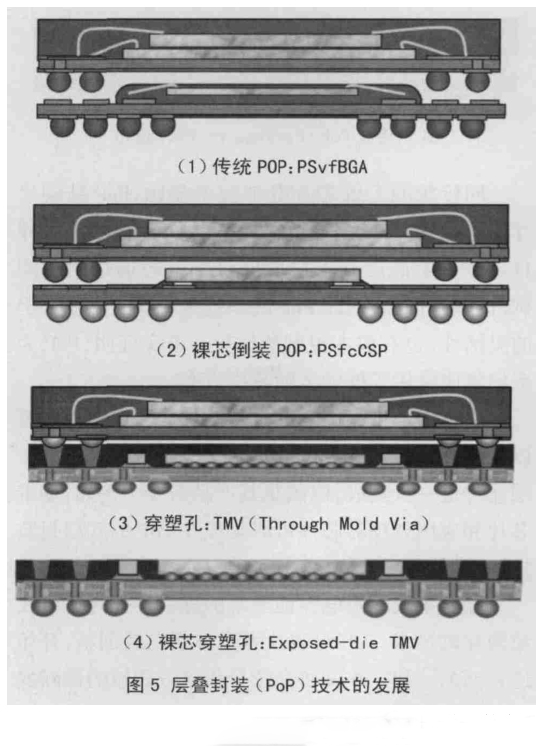

在封装技术上,相继出现了裸芯倒装的底层封装(PSfcCSP)和穿塑孔技术(TM V,Through-M old-Via),见图 5。裸芯倒装的翘曲一般会较大。穿塑孔技术弥补了这一缺点。穿塑孔技术是在传统的塑封基础上,在上下层封装互连焊接点处打孔穿透塑封,再通过焊锡球柱形成上下层连接。穿塑孔技术具有一些显著优点。首先,它可以通过塑封材料降低封装翘曲,可以使用更高的芯片 /封装尺寸比,这就使得更大芯片的封装成为可能。其次,上下层封装互连的焊锡球因为有塑封的支撑和间隔可以使用更细的互连间距。

为进一步薄化 TM V 塑封层,现在又出现了裸芯的 TM V(Exposed-die TM V),即把塑封层高度设计成与芯片平齐,使芯片顶部裸露。这样整个封装的高度可以进一步降低,但翘曲相对也会增加一些。

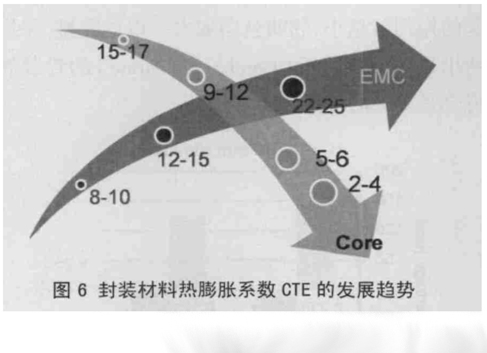

为降低封装翘曲,各种新的材料也不断出现,主要表现在材料特性的改善上。图 6 显示了基板核(Core)以及塑封(EM C)的热膨胀系数(CTE)的发展趋势。在基板方面,热膨胀系数低的基板核有利于降低大芯片封装翘曲,因此新的基板核材料的热膨胀系数在不断降低。原来标准的基板核热膨胀系数一般在 15-17 ppm 左右,然后出现了 CTE 在9-12 ppm 之间的低 CTE 基板核,现在 CTE 在 5-7ppm 间的超低基板核也已相当普及,最新一代的已接近 2-4 ppm 。与此同时,塑封材料的 CTE 特性则不断升高,各种高 CTE 的塑封材料也层出不穷,常温下的 CTE 值已从原有的 10 ppm 左右升至 20-30ppm 之间。这些新材料的研发极大地帮助改善了因薄化而产生的翘曲问题。

为降低封装翘曲,各种新的材料也不断出现,主要表现在材料特性的改善上。图 6 显示了基板核(Core)以及塑封(EM C)的热膨胀系数(CTE)的发展趋势。在基板方面,热膨胀系数低的基板核有利于降低大芯片封装翘曲,因此新的基板核材料的热膨胀系数在不断降低。原来标准的基板核热膨胀系数一般在 15-17 ppm 左右,然后出现了 CTE 在9-12 ppm 之间的低 CTE 基板核,现在 CTE 在 5-7ppm 间的超低基板核也已相当普及,最新一代的已接近 2-4 ppm 。与此同时,塑封材料的 CTE 特性则不断升高,各种高 CTE 的塑封材料也层出不穷,常温下的 CTE 值已从原有的 10 ppm 左右升至 20-30ppm 之间。这些新材料的研发极大地帮助改善了因薄化而产生的翘曲问题。

3 超薄穿塑孔 TMV 试验样品

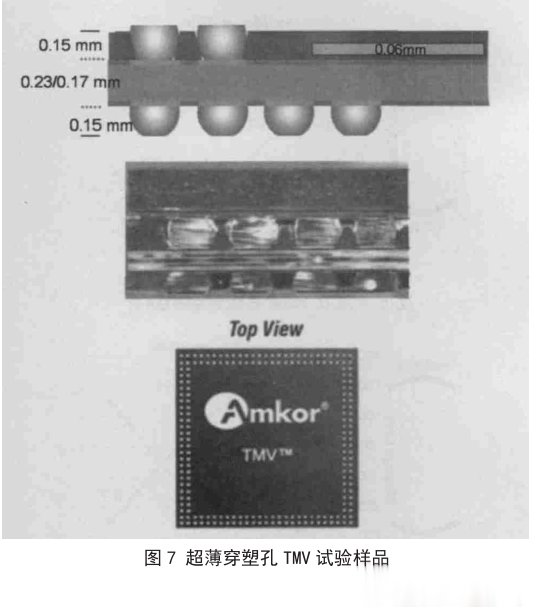

为了探索封装超薄化后可能出现的翘曲情况,以及超薄所带来的相应的设计、材料、生产过程中可能出现的问题和挑战,我们设计并实际组装了一组超薄 TM V 试验样品,见图 7。

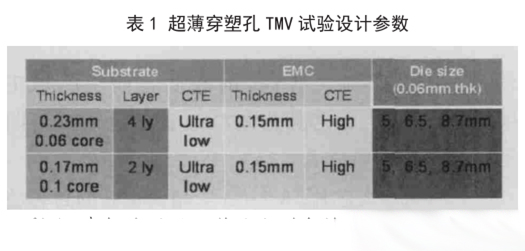

表 1 中所列为试验设计参数。芯片厚度为60μm ,相应的塑封层厚度采用 0.15 m m 厚。分别使用了两种基板设计:一种为 4 层板共计 0.23 m m 厚,另一种为 2 层板共计 0.17 m m 厚。整个封装大小尺寸为 12 m m 。为了研究不同芯片大小尺寸对翘曲的影响,我们使用了三种从小到大的芯片尺寸,分别为5 m m ,6.5 m m ,8.7 m m 。在材料使用上,采用了一种超低 CTE 的基板和一种高 CTE 的塑封组合。

4 不同芯片尺寸下的封装翘曲

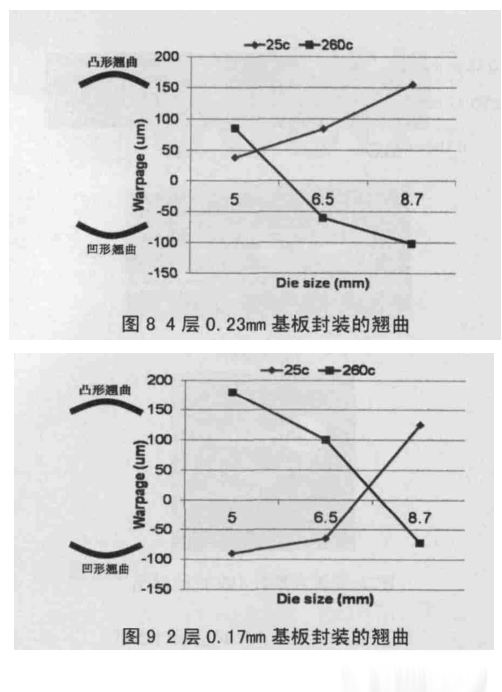

图 8 和图 9 分别显示了使用 4 层 0.23 m m 基板和 2 层 0.17 m m 基板封装不同尺寸芯片时的翘曲数值。这些翘曲数值是通过莫尔条纹投影仪(shadowm oiré)测量的平均值。根据业界惯例,正值翘曲表示翘曲为凸形,而负值翘曲表示翘曲为凹形,如图中所示。

从图中数据我们可以得出一些很重要的结论:

(1)封装超薄化后,翘曲对芯片大小非常敏感。不同尺寸的芯片封装后翘曲相差非常大,甚至翘曲的方向都会改变,例如图 8 中在回流温度 260℃时的翘曲,当芯片为 5 m m 时翘曲方向是凸形正90μm(正值),而芯片为 8.7 m m 时翘曲变成了凹形负 100μm(负值)。

(2)对于大芯片(8.7 m m),超薄化后的封装翘曲非常大,超过了一般要求的翘曲水平(100μm 以下)。所以,大芯片超薄封装的翘曲极具挑战性。另一方面,也不是说芯片越小翘曲就会越小,如设计或材料选择搭配不当,小芯片封装会比大芯片封装的翘曲更大。例如图 9 中所示,5 m m 芯片比 6.5 m m 及8.7 m m 芯片的翘曲都大。原因是不同大小的芯片翘曲方向有可能不同。

(3) 通常所说的采用低 CTE 的基板和高 CTE的塑封组合有利于降低翘曲,是针对封装大芯片时当翘曲方向在室温下是凸形而高温下是凹形时才成立。而当使用小芯片时,翘曲方向有可能反过来,此时上述观点将不再成立,而必须使用高 CTE 的基板配低 CTE 的塑封组合,才能降低翘曲。

(4)图中数据显示,同一套材料组合及设计很难适用于各种不同大小的芯片。

(5)综上所述,新一代超薄封装将会使翘曲大小和方向出现各种可能,而且相当敏感,难以只凭经验预估。所以,必须定制优化,并在设计时使用相关的计算机有限元翘曲模型模拟仿真,以帮助预估最后封装的翘曲及改善的方案例如各层厚度和材料的选择搭配。

5 基板薄化对翘曲的影响

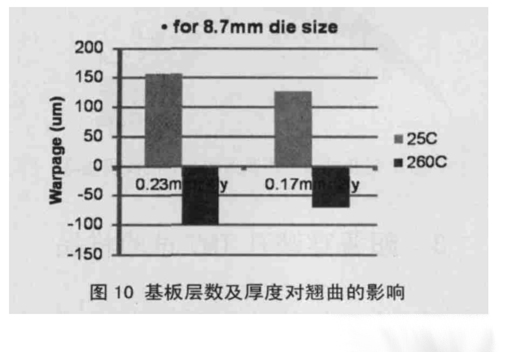

在基板设计时,可选择采用不同的层数和厚度。除了对基板电性能的考虑之外,这些因素对封装的翘曲也有影响。图 10 显示了使用 4 层板和 2 层板的封装在翘曲上的差别。对大芯片封装而言,使用 4层基板的封装翘曲比 2 层基板的会更大。这是因为4 层基板含更多的金属层和绝缘层,这些材料具有相当高的 CTE,从而使得 4 层基板的整个基板有效CTE 值要比 2 层基板的大,翘曲也就相应增大。相对而言,基板层数越多,或者基板核越薄,基板核所起的作用就越小,翘曲就会加大。以此类推,采用最新出现的无核基板(CorelessSubstrate)的封装翘曲将会是更大的挑战。

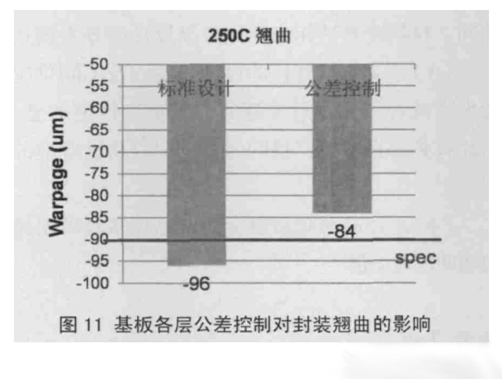

基板变薄后带来的另一个问题是基板设计公差的影响增大。传统基板使用很厚的核,核在整个基板的机械性能上起主导作用,所以设计公差的影响并不明显。但当基板变薄后,核的主导作用变弱,各层厚度的设计公差所带来的成品基板差异就不能再忽略了。图 11 显示了一例基板设计时公差控制的影响。第一组数据采用标准设计共差,结果封装的翘曲在回流高温时为 96μm ,超过客户指标(90μm)。

第二组数据为改进版,对基板各层厚度的公差做了进一步控制,尤其是金属层(信号层)。结果这一组的翘曲得到改善,降低了 12μm ,达到了客户指标要求。这说明当基板变薄后必须加强对公差的控制,同时,当封装产品开发已进入最后阶段,其它各种参数都已定型的情况下,也还有可能通过对基板各层的厚度公差进行优化控制,以进一步改善翘曲,达到客户指标。

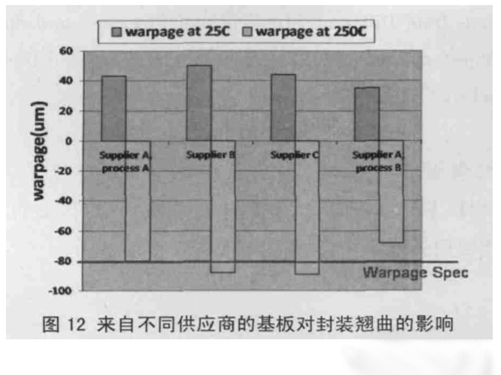

基于类似的原因,我们发现,基板变薄后,不同基板厂商生产流程控制差异所造成的成品基板差异也变得更加明显,必须加以更严格的控制。尤其是在现代的商业模式下,同一基板总是从几家不同供应商进货。图 12 显示了一例同一设计但来自不同供应商的基板对最后封装翘曲的影响。数据表明,使用三个供应商的基板进行封装的翘曲都不同,相差达 20μm 。其中供应商 B 和 C 的基板封装的翘曲最后都超标。而即使是同一供应商 A,不同的生产流程控制也会造成翘曲差异。

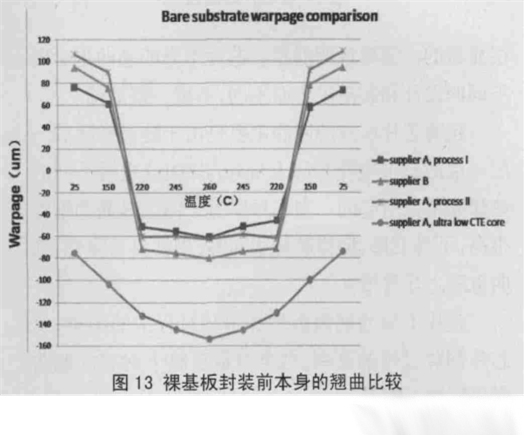

为进一步研究造成基板差异的根源,我们也测量了这些基板在封装之前裸基板每个单元本身的翘曲。图 13 显示的是来自不同供应商的裸基板在封装之前其自身的翘曲比较。可以看出,基板薄化后,不再像传统的厚基板那样平整,裸基板本身就会产生很大的翘曲(可达 100-200μm),而且翘曲随不同的供应商,不同的生产流程控制而不同。另一个发现是,裸基板本身的翘曲可随不同的基板核材料而呈现完全不同的状态。

裸基板本身的翘曲除了会影响最后封装的翘曲之外,还会影响封装过程的可制造性(m anufactura-bility)。例如在芯片倒装过程中,如果裸基板的翘曲过大,会使芯片倒装无法实施。

封装薄化之后,基板对设计公差及供应商生产流程的差异都变得更加敏感。因此,必须采用更严格的公差控制和供应链的控制,才能更好地控制最后封装的翘曲。

6 超薄裸芯片的翘曲

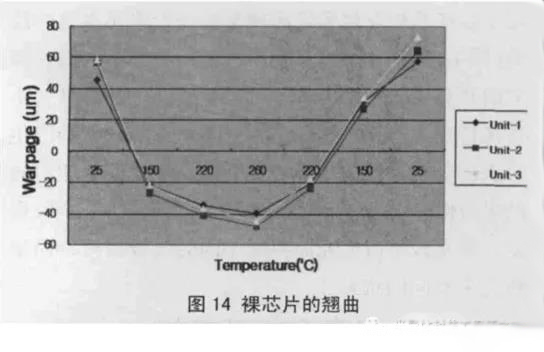

芯片本身也在不断薄化,从 100μm 降至80μm ,60μm ,甚至 50μm 以下,而芯片本身的翘曲问题也开始出现。图 14 显示的是一颗厚度为50μm ,大小为 8 m m ×8 m m 的裸芯片在不同温度下的翘曲。图中数据表明 50μm 厚的芯片本身的翘曲可以由室温下的正 50μm (凸形) 变为高温260℃下的负 40μm (凹形),这种程度的翘曲还是很显著的。需要说明的是,芯片本身的翘曲也会因不同的设计和制造过程而不同,不能一概而论。

超薄芯片本身的翘曲主要是由于硅晶和随后一层一层的低 k 电路(low k layer,BEOL)之间不同的热膨胀系数引起的。当芯片厚时,由于硅晶的钢性很高,不易变形,但当芯片很薄时,钢性显著降低,翘曲也随之显著增大。

芯片本身的翘曲会增加组装过程中的困难,及芯片倒装过程的良率,也会对最后整个封装的翘曲产生影响。

7 总结

本文论述了新一代叠层封装(PoP)的发展趋势。主要表现在芯片 /封装比增大,倒装芯片及铜柱技术的应用,上下封装层互连间距缩小,以及封装超薄化。为此新的 PoP 技术例如穿塑孔 TM V 等因应而生,新一代超低 CTE 基板和超高 CTE 塑封材料等也开发迅猛,以降低因超薄化引起的封装翘曲。

文章进一步讨论了封装翘曲这个已成为阻碍新一代PoP 发展的瓶颈问题和面临的挑战。基于收集的生产实验数据,可以得出如下结论:

(1)超薄化后的封装翘曲对芯片尺寸大小相当敏感。

(2)封装的各层厚度设计以及封装材料的选取必须根据不同应用,不同芯片的大小进行定制优化,采用不同的组合才能控制好翘曲。很难再使用传统的同一材料配置适用于不同产品设计的开发模式。

(3)超薄化后基板的设计公差以及不同供应商的生产流程差异对封装翘曲的影响变得更加显著,因此有必要采取更严格的公差控制以及供应链的控制。

(4)芯片超薄化后也会使裸芯片本身出现显著的翘曲问题。