随着电子产品微小型化、多功能化和信号传输高频高速数字化,要求PCB 迅速走向高密度化、高性能化和高可靠性发展。为了适应这个要求,不仅 PCB 迅速走向 HDI BUM板、嵌入(集成)元件 PCB 等,而且 IC 封装基板已经迅速由无机基板(陶瓷基板)走向有机基板(PCB 板)。有机 IC 封装基板是在 HDI/BUM板的基础上继续‘深化(高密度化)’而发展起来的,或者说 IC 封装基板是具更高密度化的HDI/BUM板。

1.1 有机封装基板的提出封装基板是用于把多个一级(可用二级)封装IC 组件再封(组)装形成更大密度与容量的一种基板。由于这类基板的封装密度很高,因此,其尺寸都不大,大多数为≤50*70mm2。

过去主要是采用陶瓷基板,现在迅速走向高密度PCB封装基板。

(1)陶瓷封装基板。

陶瓷封装基板的应用已有几十年的历史了,基优点是CTE 较小,导热率较高。但是,随着高密度化、特别是信号传输高频高速数字化的发展,陶瓷封装基板遇到了严厉的挑战。

① 介电常数 εr 大( 6∽8)。

信号传输速度 V 是由来介电常数 εr 决定的,如下式可得知。

V=k ·C/(εr)1/2

其中: k——为常数; C——光速。这就是说,采用较小的介电常数εr,就可以得到较高的信号传输速度。还有特性阻抗值等问题。

②密度低。 L/S ≥O.1mm,加上厚度厚、孔径大,不能满足IC 高集成度的要求。

③电阻大。大多采用钼形成的导线,其电阻率(烧结后)比铜大三倍多或更大,发热量大和影响电气性能。

④基板尺寸不能大,影响密度和容量提高。由于陶瓷基板的脆性大,不仅尺寸不能大,而且生产、组装和应用等都要格外小心。

⑤薄型化困难。厚度较厚,大多数为1mm以上。

⑥成本高。

(2)有机( PCB)基板。

有机( PCB)基板,刚好与陶瓷封装基板相反。

①介电常数 ε r 小(可选择性大,大多用3∽ 4 的材料)。

②高密度化好。 L/S 可达到 20∽50μm,介质层薄,孔径小。

③电阻小。发热低,电气性能好。

④基板尺寸可扩大。大多数为≤70*100mm2。

⑤可薄型化,目前,双面/ 四层板,可达到100∽300μm。

⑥成本低。

在 1991 年,由日本野洲研究所开发的用于树脂密封的倒芯片安装和倒芯片键合(连接)的 PCB 和 HDI/BUM 板,这些有机封装基板和HDI/BUM 板等比陶瓷基板有更优越的的有利因素和条件,使它作为IC 的裸芯片封装用基板是非常合适的,特别是用于倒芯片(FC)的金属丝的封装上,既解决了封装的CTE 匹配问题,又解决了高密度芯片的安装的可行性问题。

关于 PCB 基板的 CTE 较大和导热差方面,可以通过改进和选择CCL 基材得到较好的解决。

1.2 IC 封装基板的类型

1.2.1 IC封装基板主要的两个问题。

( 1)搭载裸芯片的封装基板与所要封装元(组)件的CTE(热膨胀系数)匹配(兼容)。

( 2)搭载裸芯片的封装基板的高密度化,要满足裸芯片的高集成度要求。

1.2.2 封装基板的三种类型。

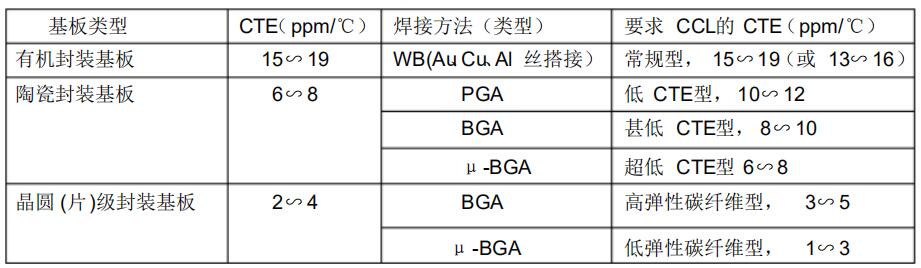

到目前为止,用于裸芯片的封装基板有三种类型,如表1 和图 1 所示。

从本质上来说, PCB 是为元(组)件提供电气互连和机械(物理)支撑的。在今天的电子封装市场上,主要存在着三种类型的的封装:

( 1)有机基板的封装, 其 CTE 为 13∽19ppm/℃,采用金属丝键合 (WB),然后,再 BGA/μBGA焊接到 PCB板上;

( 2)陶瓷基板封装, 其 CTE 为 6∽8ppm/℃,由于陶瓷基板的缺点, 逐步采用 6∽8ppm/℃有机封装基板;

( 3)与晶圆片匹配的有机封装。既理想的尺寸与速度(即芯片级)匹配的封装,如采用

特别低的 CTE封装基板与晶圆 (片)级封装( WLP,wafer level package)、直接芯片安装 ( DDA ,direct die attach)匹配的安装 ,其 CTE 接近 2∽4ppm/℃(参见表 1)。

很显然,常规的PCB是不具备这些高级封装(低CTE场合)能力的,因此, PCB工业必须发展低 CTE材料,以满足这些高级封装基板材料的技术和产品。

表1 三种封装基板的CTE及对CCL的CTE要求

注:陶瓷封装基板对CCL要求是指‘裸芯片’已封装在陶瓷基板,然后再安装到 PCB基板上而言。

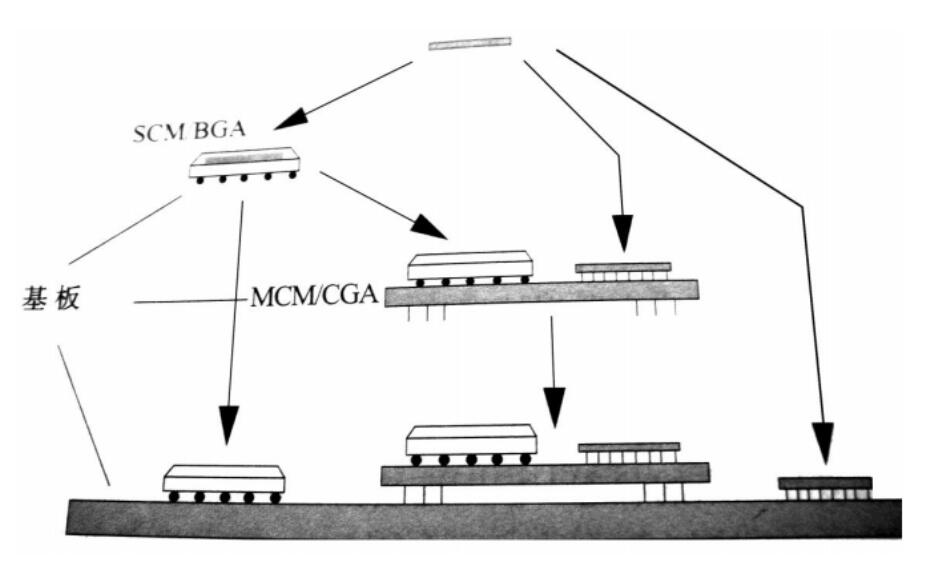

目前,按元(组)件封装到 封装基板 上的 CTE大小,可把封装基板分为三种类型(如图4 所示)。

图1 三级基板的示意图

1.2.3 基板封装与元(组)件的 CTE 要求。

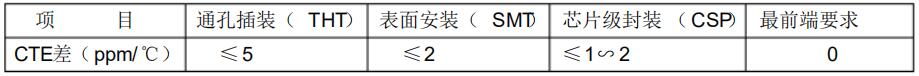

封装基板与封装元(组)件之间的 CTE匹配(兼容)问题。两者的CTE不匹配或相差甚大(如过去要求≤5ppm/℃,现在要求更高)时,焊接封装后产生的内应力便威胁着电子产品使用的可靠性和寿命。因此,封装基板 与所封装元(组)件之间的CTE匹配(兼容)问题,正随着安装高密度化和焊接点面积的缩小而要求两者的CTE 相差越来越小,即Δ ≤5ppm/℃→ Δ ≤3ppm/℃→ Δ≤2ppm/℃→ Δ ≤1ppm/℃→ Δ =0。如表 2 所示。

表2 封装基板与所安装的元件间CTE差的要求是随着安装技术发展而不同

注: CTE差( ppm/℃)是指 封装基板 与所封装元(组)件之间的 CTE(差别)匹配度。

陶瓷基板封装是把芯片( die,系指裸芯片)安装到陶瓷基板上,然后,它可以安装到PCB基板上。首先,把硅芯片(silicon die )安装到陶瓷基板(CTE 为 6∽8ppm/℃)上,但是还不能安置到 PCB基板上,因为

PCB的 CTE大小为 16∽19ppm/℃,两者的 CTE不匹配、差别太大。为了解决这个问题:

①大多采用圆柱形插装(column instead of balls)来解决陶瓷基板与PCB基板之间的可靠性连接问题。因为,圆柱形引脚是高而细长的固体圆柱形针(pins ),它可以随着不同膨胀而摆动, 从而是有理由提供可靠的焊接点的。但是, 目前常规的 BGA焊接已经成为主流,要在每个连接区域除去球形(BGA)连接而改成柱形连接,那是很费时和昂贵成本为代价的,显然这不是根本的出路。

②最好而根本的办法,应该是把PCB基板的 CTE=16∽19ppm/℃下降到 8∽10ppm/℃或 6∽8ppm/℃的 CTE。这样,就可以不必再采用陶瓷基板了。但是,随着 IC 组件的高集成度化、特别是信号传输的高频化和高速数字化的快速发展,由于陶瓷基板的(相对)介电常数大(εr=6.6 ),介电损耗也大,因此陶瓷封装基板的应用也受到了限制,特别是在10G以上频率的信号传输与计算,因此,其应用的领域越来越小。

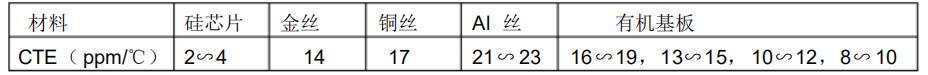

有机基板封装是把裸芯片( die,系指裸芯片)安装到很高密度的有机基板上,然后,它再安装到常规密度的大尺寸PCB基板上。 即把硅芯片 (silicon die )以金属丝安装 (如 TSOP,thin small-outline package等)有机基板( CTE 为 13∽19ppm/℃)上,然后再以 BGA安装到常规密度的大尺寸 PCB基板上,或直接应用到超小型的电子产品中,如表 3 所示。

从表 3 可看出:

( 1)典型的芯片的热膨胀系数 CTE 为 2∽4ppm/℃,这就很难可以直接封装在PCB上,因为 PCB的 CTE大小为 16∽19ppm/℃(有的文献数据为13∽15ppm/℃、 13∽17ppm/℃等,这是由基材所用类型决定着),很难能够与芯片的CTE与之相匹配;

( 2)采用金属丝(金的CTE 为 14ppm/℃、铜丝的 CTE为 17 ppm/ ℃、 Al 丝的 CTE为 21∽23ppm/℃)连(焊)接封装在不同CTE大小的有机基板(如目前大多数的IC 封装基板)上,然后,再以TSOP(thin small-outline package)的金属引脚或BGA形式再在 PCB基板上进行安装,因此,有机封装基板与PCB 基板之间不存在着严重的CTE 不匹配问题。尽管, 采用金属丝键合(连接)的有机基板封装技术,比起陶瓷基板的封装已具有很多的优点,目前正在高速发展中。但是,比起倒芯片/FCOB/DDA封装技术,仍然存在着封装面积大,连接路线长 会降低信号传输速度的,对于很高速的信号传输是不理想的,一旦有机封装

基板的 CTE减少到 2∽4ppm/℃或 3∽5ppm/℃时,才会把目前的有机封装基板减少下来。

倒芯片类型的元(组)件是具有很低的CTE,大多处在 2∽ 4ppm/℃之间。很显然,把很低的倒芯片类型的元(组)件安装到高膨胀系数的PCB 基板上是一个巨大的挑战,特别是高密度的细小焊盘的焊接,那是关系到焊接点的可靠性问题。很小的倒芯片在传统的PCB上的安装可行方法之一是借助于焊接部位不填充方法(underfill),但是,它限制了PCB返工(修)的可能性。因此,要把倒芯片可靠地安装到PCB板上,必须要求 PCB具有很低的CTE ,目前正在开发碳纤维的CCL基板材料。

①低-弹性模量碳纤维。用得多的是PAN碳纤维。低-弹性模量碳纤维具有接近于-0. 4ppm/℃,当与树脂结合起来形成的复合材料,其CTE可达到4.5∽6.5ppm/℃。这样的CTE等级已经可与传统的IC芯片的CTE(5∽7ppm/℃)严密匹配了。

②高-弹性模量碳纤维。正如大家了解的高-弹性模量碳纤维PITCH,其 CTE 也接近 -0. 4 ppm/℃,但当高 -- 弹性模量PITCH 纤维与树脂形成复合材料时,其CTE 为 1.0 ∽3.0ppm/ ℃。可以应用于那些要求很低

CTE(2∽4ppm/℃)的 IC 芯片相匹配的场合。

总之, IC 封装基板主要体现在:

(一) 基板材料的 CTE更小或匹配, 即此类 IC 基板的 CTE要明显的减小,并接近(兼容)芯片引脚的CTE,才能保证可靠性;

(二)直接用于裸芯片(KGD)的封装,因此要求IC 基板更高密度化;

(三)封装基板的厚度薄,尺寸很小,大多数小于 70*70mm;(四) 大多选用薄型的低CTE基材,如 PI 材料、超薄玻纤布和碳纤维的CCL材料。

有机封装基板的工艺技术路线,主要有两种:

(一)传统高密度的制造方法;

(二)高密度的 HDI/BUM方法。

2.1 有机封装基板的主要技术指标

有机封装基板的主要技术指标如下:

( 1)成品外形尺寸。大多数为70*100mm

( 2)基板层数,目前为2∽4。

( 3)基板厚度, 0.1 ∽0.3mm。

( 4)导线宽度 L/ 间距 S。L/S≤50μm(20∽50μm)。半加成法 L/S≥40μm。全加成法 L/S≤40μm(如 5μm)。

( 5)孔径 Φ为 50∽80μm。

2.2 CCL 材料

根据封装基板的组装要求和条件来选择,因此要充分了解上、 下游的技术指标性能与要求。如,采用 Cu 或 Au丝连接(键合)的封装基板,应该采用对温度(包括高温焊接的耐热)尺寸稳定性,关键是翘曲度问题,或CTE匹配问题。

( 1)CTE小、 Tg高的材料。如 BT 材料、 PI 材料、改性 / 高 Tg 环氧材料等。

( 2)薄型基材。即薄型玻纤布所形成的CCL。如 0.1 ∽0.3mm。

2.3 微小孔的形成

( 1)钻 / 蚀孔。主要有机械钻孔和激光蚀孔。

①机械钻孔。采用高速钻机,转速为20∽ 30 万转 / 分,可达到 Φ50∽80μm

② 激光蚀孔。

(一)红外( UV)激光蚀孔,光波长( 9.6 μm/10.6μm)孔的厚 / 径比受到限制(应≤ 0.5 ,否则,问题多) ,现在已经可提供LG—PP 材料。 RCC材料有缺点,介质厚度难保证(特别是均匀性) 。

(二)紫外( UV)激光,可不开‘窗口’ ,提高位置度,光波短(大多采用 0.365μm),孔径可更小。功率较低,生产率较低。目前已经提高到6∽8 瓦,这个问题已得到解决。

( 2)孔化 / 电镀。

采用常规孔金属化工艺和电镀铜填孔技术是可以完成的

2.4 图形转移技术

( 1)L/S 微小化。减少侧蚀和提高精细度:

①图形电镀(含填孔镀) ,解决均匀性电镀,然后蚀刻。

②铜箔减薄(≤ 6μm),然后图形电镀(含填孔镀)/ 或全板镀,蚀刻形成。

③ 在介质是完成孔金属化和电镀(含填孔),然后蚀刻。

( 2)曝光掩膜

①常规菲林。不适宜,不能满足尺寸精细堵要求。

②玻璃底片。不适宜操作。

③铬片。适宜。

( 1)蚀刻抗蚀剂。

①干膜。厚度应选≤ 25μm( 80∽120mj/cm2)。

②采用激光直接成像用干膜(8∽12mj/cm2)。

( 4)激光直接刻像。注意保证介质层厚度。

2.5 表面涂(镀)覆一般情况下,表面涂(镀)覆层大多数采用化学镀镍/ 浸金,现在也可是采用化学镀银。当然,采用化学(或电镀)镍/ 金/ 钯,更好。

①化学镀镍 / 浸金。金层要厚,并属软金,其厚度应≥0.15 μm 或更厚,因为金丝是键合(焊接)在金层上的。如果采用铜丝键合(焊接)是可以用薄金的。

②化学镀银。银是可以与金、铜丝键合(焊接),但银的厚度要厚些,应≥ 0.30 μm。而化学镀银是不能与Al 丝键合(焊接)的。