CPO(共封装光学)技术将光引擎与交换芯片的距离缩短至毫米级,在降低30-50%功耗的同时,也给承载光电信号交互的PCB带来了颠覆性设计挑战。不同于传统可插拔光模块PCB,CPO光模块PCB需同时承载高频电信号传输、集中式热源散热与光电混合集成三大核心任务,其设计精度直接决定1.6T及以上速率光模块的稳定性与量产可行性。以下从设计全流程出发,解析CPO光模块PCB的核心要求与优化路径。

CPO光模块的高频特性(支持224G SerDes,频率超50GHz)与功率密度(超10W/cm²),对PCB基材提出了“低损耗、高耐热、强导热”的三重要求,传统FR-4基材已完全无法满足需求,低损耗高频基材成为标配。

介电性能是基材选型的核心指标。CPO光模块PCB需优先选用介电常数(Dk)稳定在3.0-3.5之间的基材,且Dk值随频率、温度的变化率需控制在5%以内,避免信号传输延迟抖动超过5ps。同时,损耗因子(Df)需低于0.004,才能将10GHz以上高频场景下的插入损耗控制在0.3dB/in以下,确保信号完整性。目前主流选型包括Rogers RO4000/3000系列、Megtron6等,这类基材在1.6T CPO模块中渗透率已超80%。

热导率与耐热性需适配CPO的集中热源特性。基材热导率需达到1.2W/(m·K)以上,相较于普通FR-4(0.3W/(m·K))散热效率提升3倍,可有效缓解光引擎与芯片集中散热带来的温度压力。此外,基材玻璃化转变温度(Tg)需高于200°C,确保在高温回流焊(260℃以上)与长期工作(70℃以内)中不会发生变形,避免层间剥离风险。

铜箔与辅料选型需协同增效。信号线路优先采用压延铜箔(Ra≤0.3μm),减少趋肤效应带来的损耗;散热区域则选用1oz-3oz厚电解铜箔,通过大面积铜皮加速热量传导。阻焊剂需选用耐高温、低吸水型(吸水率≤0.1%),如太阳油墨PSR-4000,高功率模块还需搭配热导率≥1.5W/(m·K)的导热胶,进一步优化散热路径。

CPO模块中电气迹线缩短至毫米级,虽降低了部分损耗,但也对信号精度提出了更严苛要求。阻抗控制是核心前提,单端阻抗需稳定在50Ω±3%,差分阻抗控制在100Ω±5%,偏差过大会导致眼图闭合,误码率升至10⁻⁶以上。设计中需通过差分对布线实现,严格控制线路长度差在5mil以内,避免时延差引发同步问题。

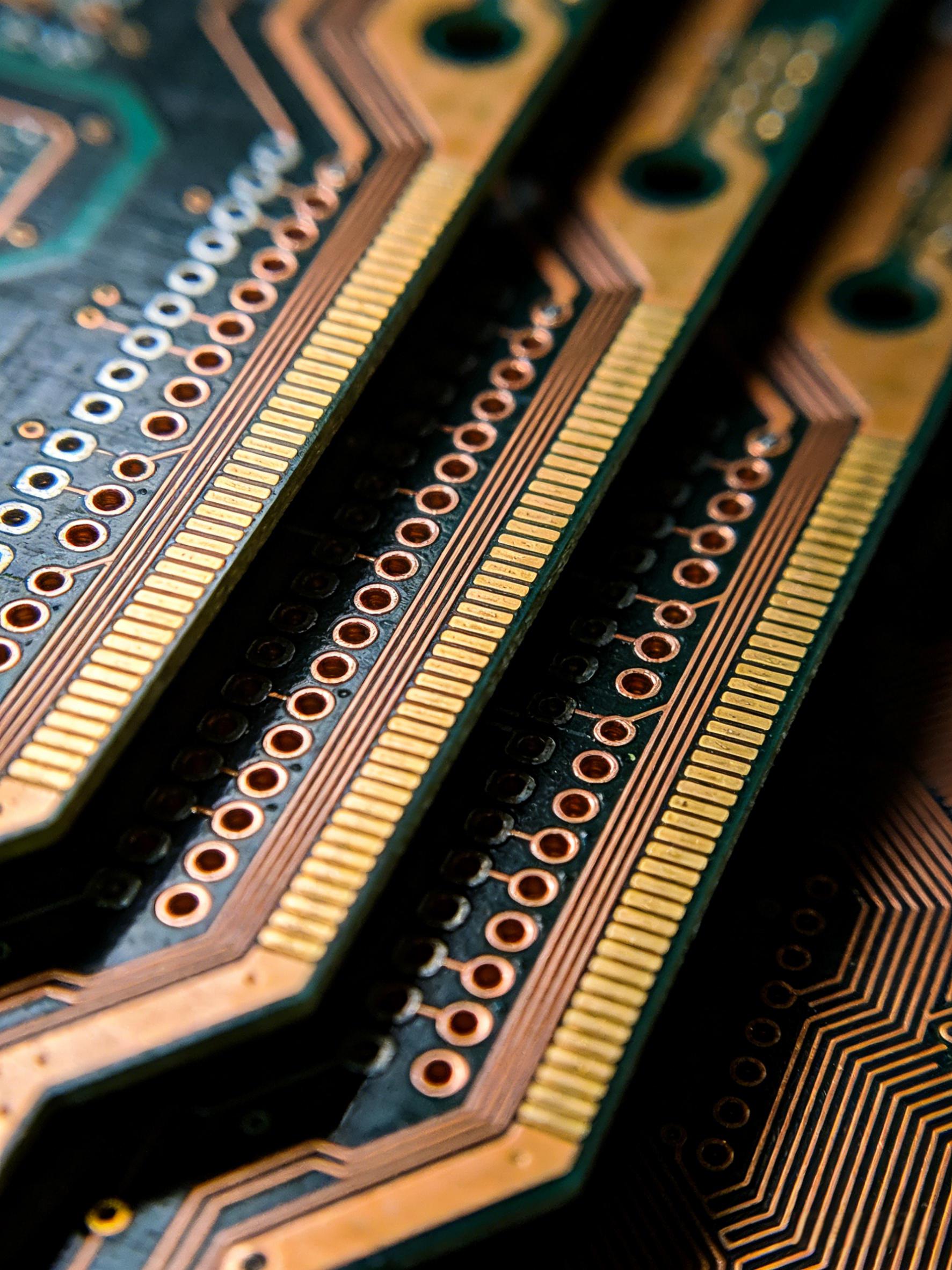

过孔与层叠设计直接影响信号损耗。应尽量减少过孔数量,高频信号线路优先布置在表层,跨层时采用盲埋孔(直径<0.1mm)替代通孔,降低寄生电感与电容带来的反射干扰。层叠结构需采用16-20层HDI设计,核心层选用低Dk基材,上下层搭配接地平面形成微带线结构,减少信号辐射损耗,同时通过“电源层-地层”相邻布局,利用电容效应降低电源阻抗。

电磁兼容性(EMC)设计不可忽视。高频信号区域需设计金属屏蔽罩(铜或铝材质),与地平面可靠连接形成法拉第笼,隔绝外部干扰。高频线路与电源线路、模拟信号线路的间距需大于3倍线宽,必要时布置隔离线,避免串扰影响;电源输入端需添加共模电感、X电容等EMC滤波器,滤除高频噪声。

CPO模块功率密度高,光引擎与芯片集中发热易导致激光器寿命缩短40%,热管理设计需实现热阻<1.5°C/W的目标。散热过孔阵列是核心方案,在芯片下方散热区密集布置孔径0.2mm-0.4mm的过孔,内壁镀铜后与底层散热铜皮连通,形成垂直散热通道,可使热阻下降32%以上。

铜皮与嵌入工艺可强化散热能力。在芯片对应PCB区域设计大面积铜皮散热区,通过直接接触加速热量传导;高端1.6T CPO模块可采用铜币嵌入工艺,进一步提升局部热导率,搭配定制散热盖与独立散热片,在45°C环境温度下可将光引擎温度控制在70°C以内。

布局优化辅助散热。将发热量大的光引擎、驱动芯片与敏感元器件分区布置,避免热量集中;电源线路采用宽铜箔(为信号线路2-3倍),缩短供电路径,减少线路发热的同时提升散热效率。

CPO技术的核心是光电共封装,PCB布局需预留光引擎与ASIC芯片的协同空间,支持双面LGA接口设计——底部900μm间距LGA连接主板,顶部400μm间距LGA连接光引擎,通过弹性压缩机构确保信号完整性。光引擎区域需预留光波导接口,适配硅光子技术,提升传输效率的同时降低对电信号的依赖。

兼容性设计需兼顾当前与未来需求。布局时需考虑光引擎的可拆卸性,便于后期维护;预留扩展空间,支持从8×800G向12.8Tbps容量升级。同时,需规避湿度环境下的CAF(导电阳极丝)现象,优化层间间距与材料搭配,降低测试失败率。

CPO光模块PCB设计复杂度高,需通过仿真工具提前预判问题。信号完整性(SI)与电源完整性(PI)仿真需采用HyperLynx、IBIS-AMI联合仿真模型,覆盖ASIC SerDes、PCB、LGA插座及光引擎的全链路,模拟28GHz频段下的通道损耗(控制在5-9dB),确保最坏情况误码率满足以太网标准并预留余量。

制造过程中的测试需全面覆盖关键指标。阻抗测试采用TDR(时域反射仪),批次抽测插入损耗≤0.4dB/in,阻抗偏差≤5%;热性能测试依据IPC-9701标准,验证热循环下的稳定性;洁净度测试需确保离子污染<1.0μg/cm²,避免影响长期可靠性。此外,还需进行端到端链路测试,通过PRBS31Q模式验证误码率(控制在2E-10至2E-8之间),确保与第三方模块的互操作性。

随着AI算力集群推动光模块向1.6T、3.2T速率迭代,CPO光模块PCB设计需向超低损耗与一体化集成升级。基材方面,损耗因子(Df)将降至0.002以下,进一步降低高频损耗;工艺上,微盲孔精度将提升至2/2mil线宽线距,良率控制成为核心竞争力。

可持续性与成本平衡成为重要考量。无铅无卤工艺将全面普及,符合最新环保标准;通过优化设计方案(如HDI+升级FR-4适配中端场景),可在保障性能的同时降低高频基材带来的成本压力。未来,PCB将从单纯载体转向光电混合平台,与热管、屏蔽结构一体化设计,实现性能与集成度的双重突破。

综上,CPO光模块PCB设计的核心在于平衡高频信号传输、集中热管理与光电集成需求,通过精准的材料选型、全链路设计优化与严格的仿真测试,可突破速率升级带来的技术瓶颈。