引言:射频电路板的“临界点”挑战

射频电路板设计常被工程师视为“黑色艺术”,因其在千兆赫兹频段下,传统电路理论的有效性变得模糊。一根走线的弯曲、一个过孔的位置,甚至介质材料的微小差异,都可能引发信号反射、辐射或耦合干扰。这种不确定性源于高频电路中电磁波行为的主导性——电流不再均匀分布于导体内部,而是趋近表面;电场与磁场的相互作用使得阻抗控制、隔离和散热等问题交织成多维度的工程难题。

随着5G基站、毫米波雷达和物联网设备的普及,射频电路的工作频率从Sub-6GHz向毫米波波段延伸,对PCB设计的精度要求呈现指数级提升。例如,在28GHz频段下,波长仅约10.7毫米,走线长度甚至需要控制在亚毫米级别以避免相位误差。这一趋势迫使射频设计从依赖经验的“手艺”转向基于电磁仿真和工艺协同的精密学科。

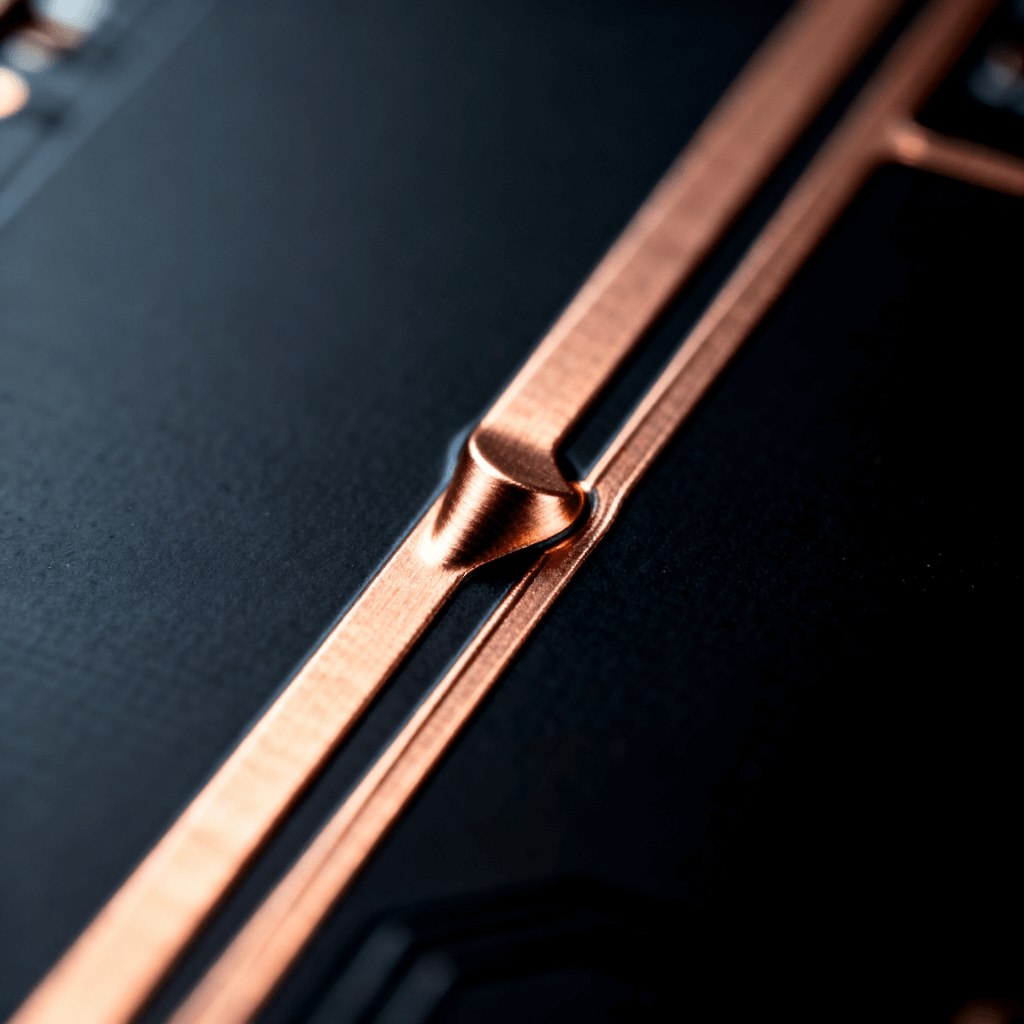

射频信号对阻抗突变极为敏感。若微带线特性阻抗偏离50Ω标准,信号能量会部分反射回源端,导致插入损耗和纹波失真。例如,一个直角走线在10GHz频率下可能引入相当于线宽20%的额外电容,破坏阻抗连续性。解决方案包括:

- 渐变线过渡:当射频线宽远大于IC引脚宽度时,采用锥形渐变结构替代阶跃变化,减少谐振风险;

- 圆弧转角优化:用圆弧曲线替代45°斜角,可将回波损耗降低3-5dB;

- 3W原则:射频线与相邻地平面边缘距离需大于3倍线宽,避免边缘场耦合。

高功率放大器(HPA)与低噪声放大器(LNA)的隔离是射频布局的基石。若两者距离过近,发射通道的谐波可能直接淹没接收端的微弱信号。实体分区可通过以下方式实现:

- 垂直隔离:将高功率电路与敏感电路分置PCB两面,利用接地层作为屏蔽;

- 时序分时:在频分双工(FDD)系统中,通过控制器切换收发状态,避免同时工作。

电气分区则需关注电源去耦与接地策略。例如,为射频芯片供电时,应采用星型拓扑结构,每个电源引脚独立连接至主滤波节点,避免共阻抗耦合。去耦电容的布局需遵循“近端优先”原则:最小容值电容(如10pF)最靠近芯片引脚,用于滤除高频噪声;较大容值电容(如0.1μF)置于外侧,抑制中低频干扰。

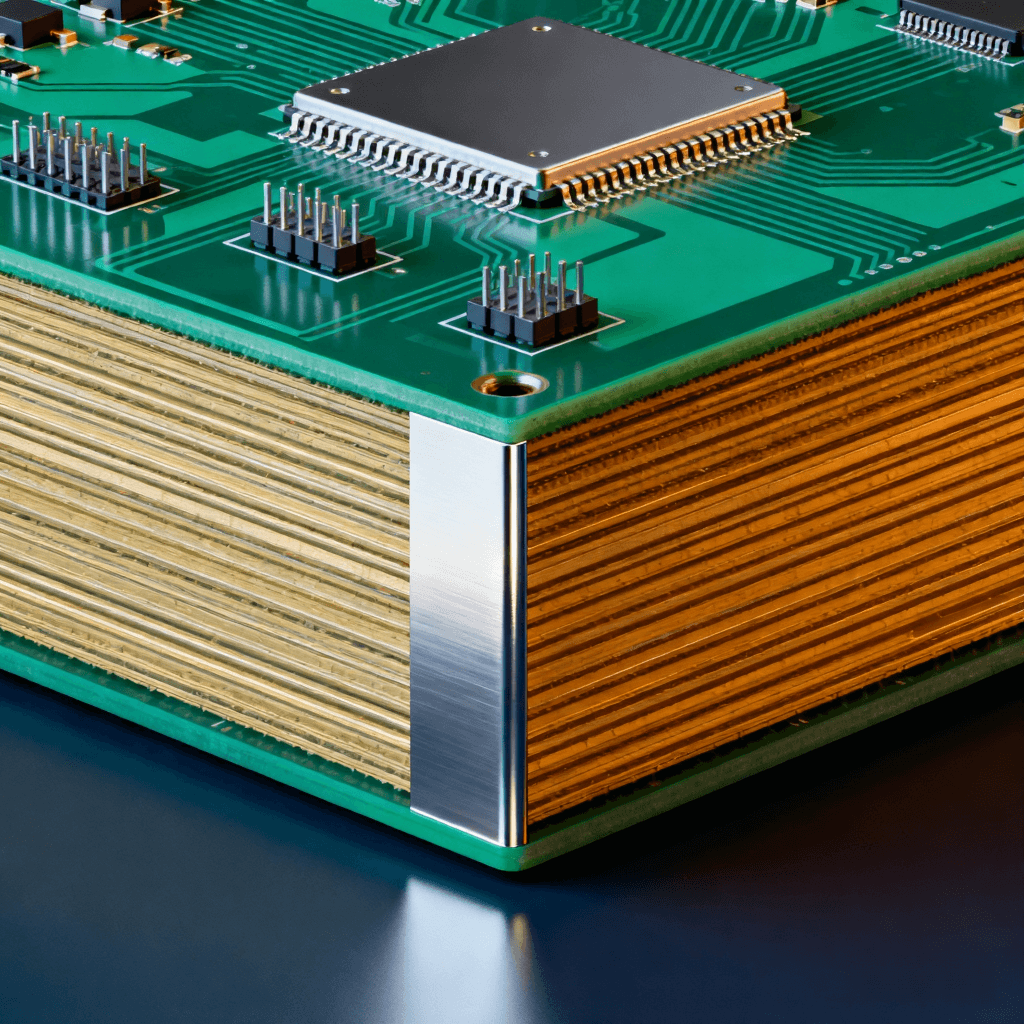

普通FR4材料在1GHz以上频段损耗显著增强,介电常数(Dk)随频率波动可达±10%。而Rogers 4350B或Taconic RF-35等特种板材具备更稳定的Dk(±0.05)和低于0.003的损耗因子(Df),但成本约为FR4的5-8倍。选型时需权衡:

- 介电常数稳定性:影响相位一致性,尤其对相控阵天线至关重要;

- 热膨胀系数(CTE):与铜箔匹配性差会导致高频下分层失效。

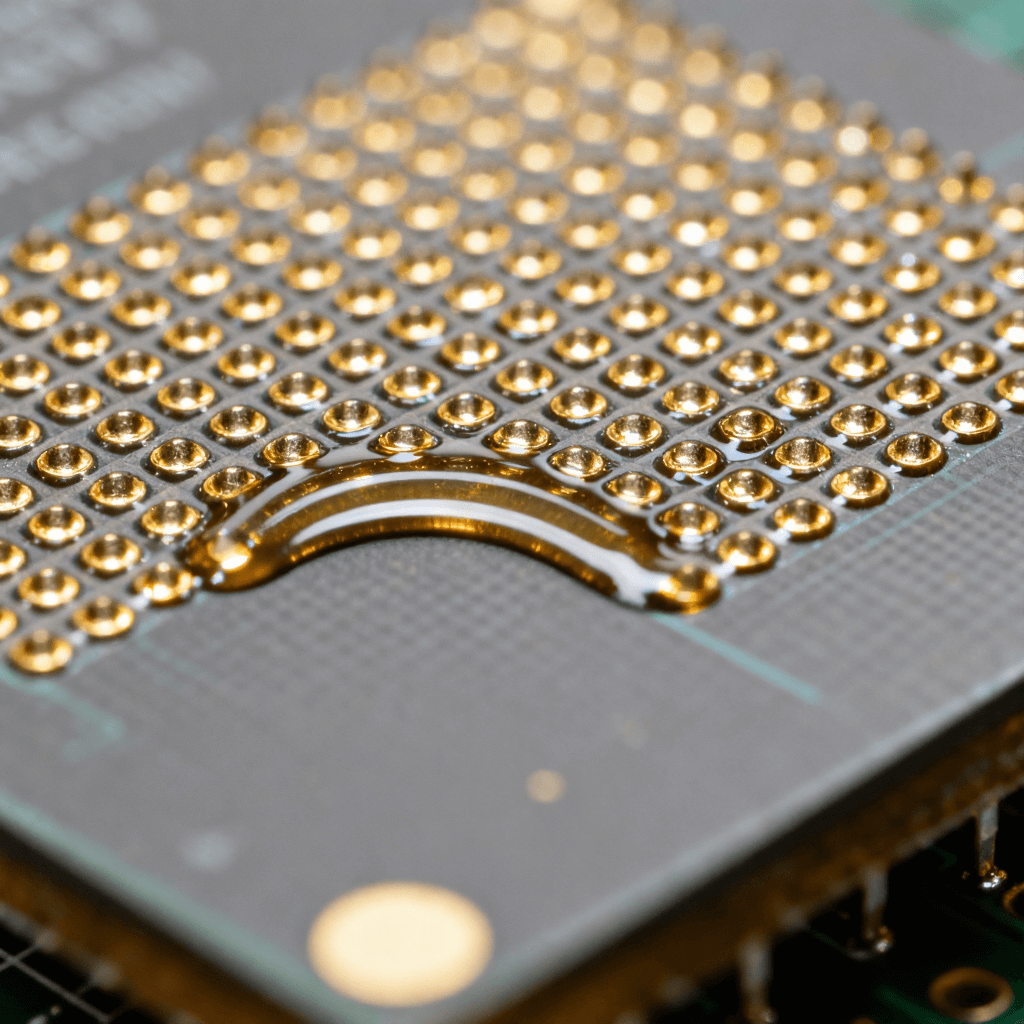

过孔在射频电路中既是连接工具也是潜在天线。通孔的寄生电感(约1nH/mm)可能引发串联谐振,盲孔和埋孔则通过减少焊盘面积降低寄生电容。例如,QFN封装器件底部接地焊盘需设置至少8个过孔(孔径0.1mm),形成低阻抗接地路径。

焊接工艺同样关键:射频器件焊盘上的锡膏过量会形成悬臂梁结构,在毫米波频段等效为集总电感。先进封装采用激光盲孔+电镀填孔技术,使过孔电感降低至传统工艺的1/3。

现代射频设计依赖电磁(EM)与电路协同仿真。以滤波器设计为例,通过ADS软件建立PCB封装、线宽、板材参数的联合模型,可预测S参数变化趋势。某案例显示,将板厚从20mil(Ro4003C)减至10mil(Rogers4350B),插损改善0.8dB,但群延迟波动增加12%。

上海交大团队研发的射频EDA软件,通过广义传输矩阵算法将跨尺度仿真(纳米至厘米)效率提升10倍,并解决电磁-热-应力多物理场耦合问题。该技术已应用于三维系统级封装(SiP),使电路最大温升降低30%。

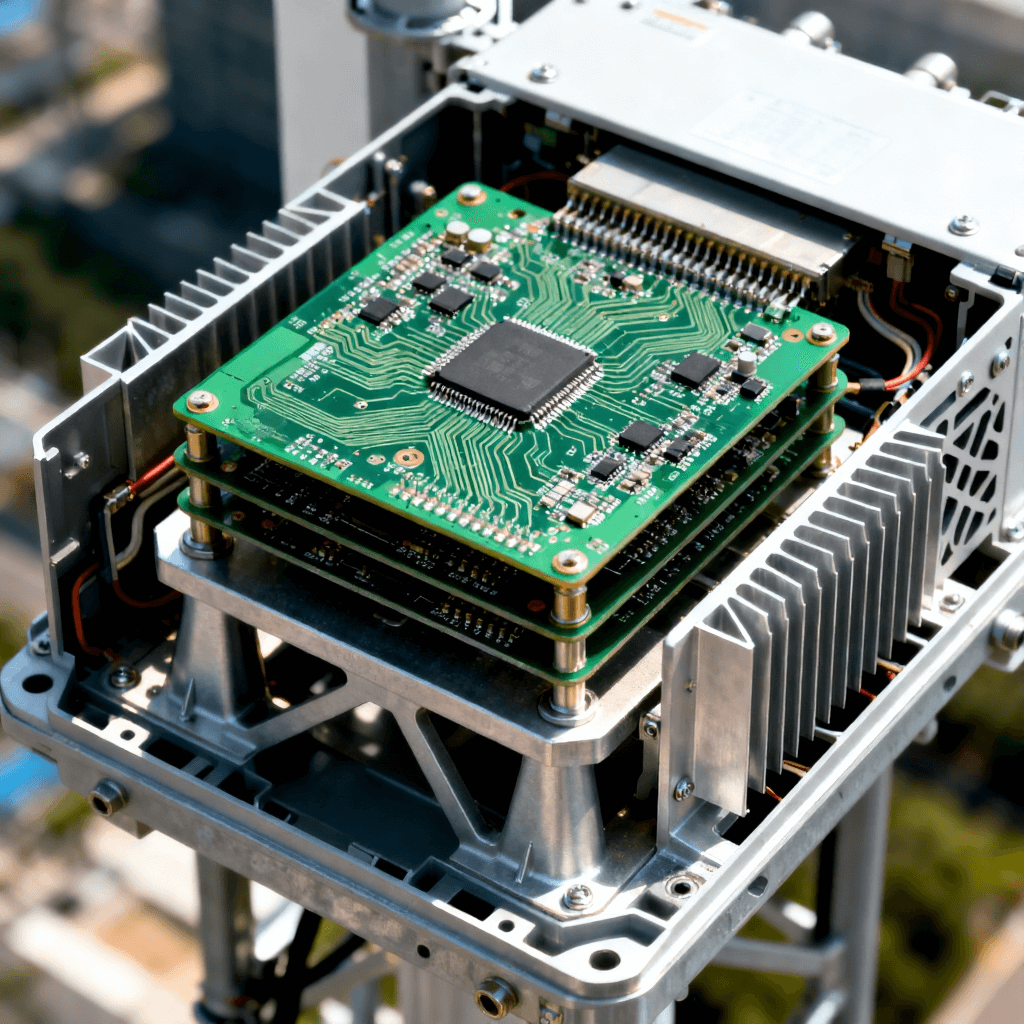

基站AAU板:需兼顾高频损耗(<0.5dB/inch)与散热,常采用混压结构(上层Rogers4350B+下层FR4);

车载雷达板:要求耐高温(-40℃~125℃)和机械振动,陶瓷填充PTFE板材成为首选。

为防止逆向工程,高端射频板常采用埋盲孔(成本增加20%)、定制无源元件(采购周期延长45天)或动态密钥认证芯片。但需权衡安全性与可维护性——封胶处理虽能增加抄板难度,却也导致维修率上升15%。

射频电路设计正经历从“黑箱艺术”到可量化科学的转型。未来,随着硅基射频前端与封装天线的集成,PCB将逐渐演变为“亚表面功能结构”:走线不仅是信号通道,更是波导、滤波器或辐射元的复合体。工程师需跳出传统Layout思维,将电磁仿真、材料特性与工艺容差纳入统一设计框架,才能在频率红海的竞争中占据先机。

而对于中国企业而言,突破高端射频板材、仿真软件等“卡脖子”环节,需产学研协同攻关——正如国产EDA工具在降低仿真内存占用、提升多物理场精度上的实践,唯有掌握底层原理,方能真正驾驭高频电路的电磁奥秘。