当芯片制程迈入 3nm 时代,IC 封装基板设计成为解决信号完整性、热管理和空间压缩的关键战场。通过高密度布线(线宽≤8μm)、异构集成和先进散热结构,现代基板在指甲盖面积内承载万亿次数据交换,支撑 AI 算力爆发式增长。

微凸点技术正重构芯片 - 基板互连范式。随着 Chiplet 架构普及,传统焊球(Bump)间距从 150μm 缩至 40μm,微凸点通过铜柱 + 锡银合金实现 10μm 级精准对接,阻抗降低 30%,热循环寿命提升 5 倍。

痛点:112Gbps 高速信号的趋肤效应损耗>15dB/cm

创新方案:

梯度介电层:

graph LR A[顶层LCP εr=2.9] --> B[中层ABF εr=3.3] B --> C[底层陶瓷 εr=5.8] |

电磁屏蔽通道:钽氮薄膜接地层(厚度 2μm)隔离串扰

性能提升:56GHz 下插入损耗<0.3dB/mm

结构 | 传统设计 | 优化方案 | 改善幅度 |

芯片贴装区 | 全铜热沉 | 碳化硅微柱阵列 | 热阻↓45% |

布线层 | 直线走线 | 分形蛇形走线 | CTE 匹配↑3X |

焊点 | SAC305 焊球 | 铜核焊球 + 纳米银烧结 | 抗疲劳↑8X |

TSV 硅转接板:

通孔直径 5μm / 深径比 20:1

铜填充空洞率<0.1%

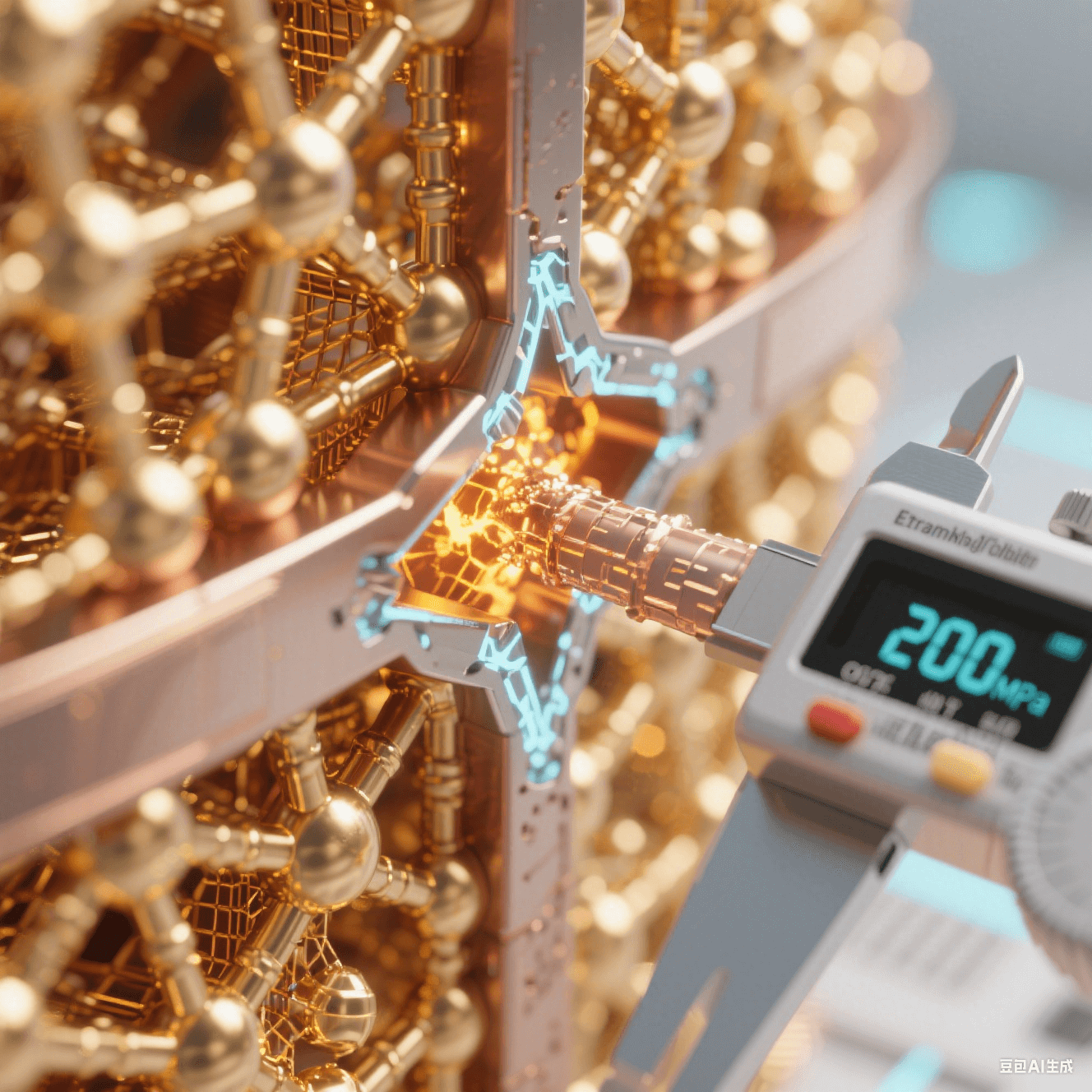

混合键合(Hybrid Bonding):

铜 - 铜直接键合(间距≤10μm)

界面强度>200MPa

优势:成本 $0.15/cm²,支持 18 层堆叠

局限:热膨胀系数 16ppm/℃(芯片 2.6ppm/℃)

适用:手机 APU、中端 GPU

突破:氮化铝基板(热导 180W/mK)+ 金导线

场景:激光雷达核心板(耐温 - 55~200℃)

精密参数:

线宽 / 间距 = 0.8μm/0.8μm

RDL 层厚 3μm±0.1μm

旗舰应用:NVIDIA H100 GPU(CoWoS 封装)

性能亮点:

高频损耗<0.002dB/GHz

平整度 ±0.5μm(优于硅基 ±2μm)

未来方向:苹果 Vision Pro 微显示屏驱动

实时决策:

if 电流密度 > 5e6 A/cm²: 启用差分对蛇形布线 elif 温度梯度 > 80℃/mm: 插入热通孔阵列 |

仿真类型 | 核心指标 | 工具案例 |

电磁场 | S 参数 / 阻抗连续性 | Ansys HFSS |

热应力 | 翘曲预测 / 焊点疲劳 | Simcenter STAR-CCM+ |

电化学迁移 | 离子扩散速率 | COMSOL Multiphysics |

微孔设计:盲孔直径>深度的 0.8 倍

铜厚控制:信号层 18±2μm,电源层 70±5μm

阻焊开窗:比焊盘大 15μm(防焊料桥接)

硅光芯片与 CMOS 基板混合集成

波导耦合损耗<0.1dB(当前>1dB)

埋入式 GaN 开关器件:

开关频率>10MHz

功率密度 500W/cm³

超导布线(NbTiN 材料):

77K 温度下电阻<10⁻⁸Ω

支持量子比特长程纠缠

IC 封装基板设计已从被动连接件进化为主动系统集成平台。当 3D 异构集成突破物理极限,微凸点技术与硅光融合将催生新一代算力引擎,为 AI、量子计算铺就高速通路。