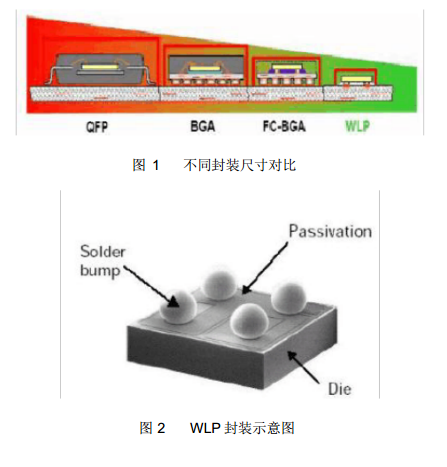

当设计一个系统级电路时, PCB 生产制作的费用是永远躲不过的,但是我们可以使用小IC封装 (例如: WLP),来压缩 PCB面积,从而节约成本。WLP 封装比之前的封装都要小,因为它们没有焊线( bond wire — 硅片到基板的连接线),而是直接建立在硅片上的,如图 1、图 2 所示。这种封装技术即节省了开发周期又节省了封装成本。然而,为了最小化 PCB 成本,在 Layout 时需要进行更多的考虑。本教程就介绍了 WLP 的 Layout 技术,遵循本文档技术要领进行 PCB 设计,可以降低风险,使系统更加稳定。

SMD 和 NSMD 焊盘

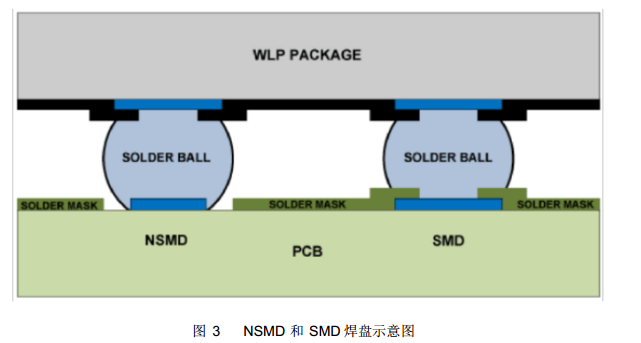

在布局布线之前,我们首先应该创建 WLP 的 PCB 封装, WLP 图纸提供了大量的尺寸信息(例如:封装尺寸、误差、 PIN 间距等),另外,还有一个重要的事项,在创建IC 的焊盘( Pad)时,我们有 SMD( Solder Mask Defined )和 NSMD( Non-SolderMask Defined )两种形式选择。 SMD 和 NSMD 如图 3 所示。

SMD:这种焊盘设计是绿油覆盖焊盘的形式,其优点是在焊接时可以防止器件焊盘被抬高(小编注:因为焊球平整度不一致,高的会架空矮的,而 SMD 是一个下凹的结构,这部分可以容纳高出的部分,如图 4);其缺点是减小了 PCB焊盘和 IC 引脚的接触面积,减小了相邻焊盘的间隔空间,限制了走线宽度和过孔的使用。

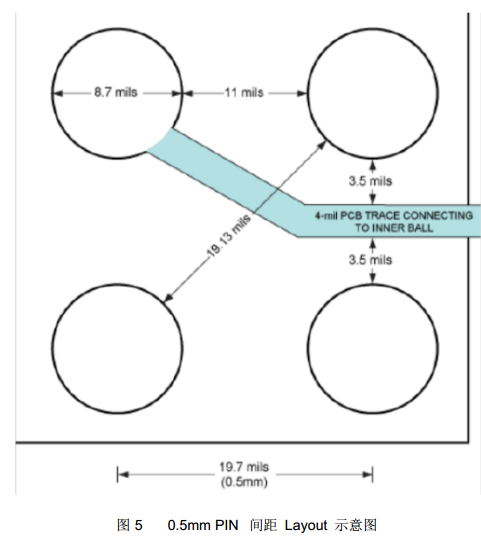

NSMD:这种设计是绿油不覆盖焊盘,并且跟焊盘有一定距离。其优点是增加了 PCB焊盘与 IC 引脚接触面积,增大了焊盘与焊盘的间距(相对 SMD 来说),允许走更宽的线和更灵活的使用过孔;其缺点在焊接时器件焊盘容易被抬高(由焊球高度不一致性造成的)。综合考虑,我们更推荐 NSMD 设计方式,这种方式有较好的焊锡连接性,使得焊盘、引脚、焊锡更好的封固在一起。在 WLPs 的 PCB 设计中,我们应该更理性更合理的去权衡 SMD 和 NSMD 的利弊,使我们的设计更加稳定。注意这两种设计方式可以同时出现在同一个 WLP 封装中。PIN 间距Maxim 提供 0.4mm 或 0.5mm 间距的 WLP 封装芯片。 PIN 间距就是芯片上的两个引脚的之间的距离,这个间距是相邻两引脚的中心距,大的 PIN 间距更方便的进行 PCB 布线。0.5mm PIN 间距(中心距):比起 0.4mm PIN 间距, 0.5mm 提供了更大的使用空间0.5mm19.7mil即相邻引脚中心距为 19.7mil ,减去 IC 引脚 8.7mil ,我们有11mil 的布线空间。如果走线到引脚(或者焊盘)间距(边到边)设置为 3.5mil ,那么PCB 布线最宽可以走 4mil 。 4mil 走线 /1oz 铜厚最大可以通过220mA 电流; 4mil 走线/2oz 铜厚,最大可以通过 380mA 电流。 0.5mm PIN 间距 WLP 封装的 Layout 设计,如图 4 所示,它展示了走线的空间分布和尺寸大小。

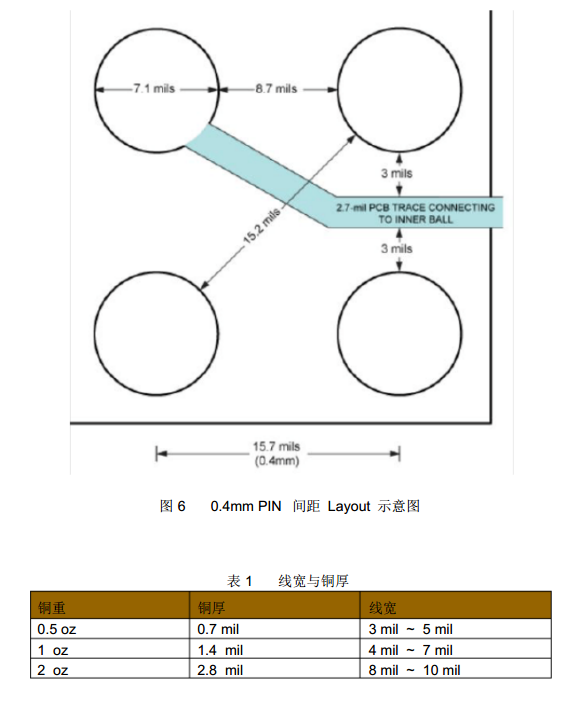

0.4mm PIN 间距(中心距):比起 0.5mm PIN 间距, 0.4mm 在设计中略显棘手。0.4mm 转换成英制为 15.7mil 。它有更小的布线空间,这也意味着在设计中有更多的限制,同时也缺乏更多的灵活性。 0.4mmPIN 间距 IC 的典型引脚尺寸为 7mil ,留给我们只有 15.7 –7 = 8.7mil 的布线空间,当走线到引脚(或焊盘)的边到边间距设置在3mil 时,剩下只有 2.7mil (最大)的布线宽度,如图 6 所示。 2.7mil 走线 /1oz 铜厚,最大可以通过 160mA 电流。用更厚的铜皮时存在一个问题,因为 2oz 铜厚等于 2.8mil ,大于走线宽度( 2.7mil ),这在制板工艺上是不允许的,因为在蚀刻 /电镀处理是可能导致走线宽度小于 2.7mil 。表 1 提供了一个线宽和铜厚的尺寸参照表。

其他方案

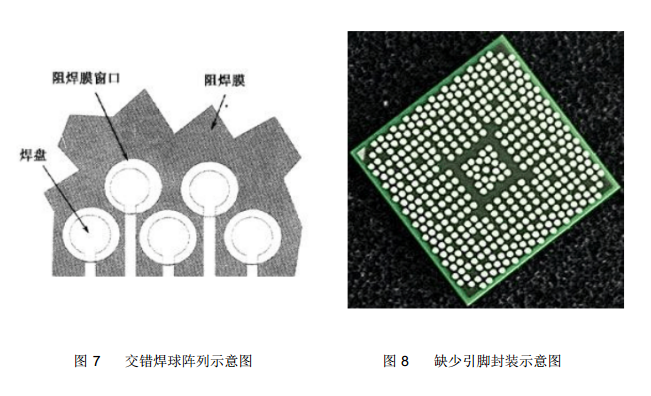

在更小的 PIN 间距(例如 0.3mm ) WLP 器件设计中,如果使用更细小的走线(载流能力差)可能不能支持系统的正常工作,那么我们可以使用其他方法解决此问题,例如使用激光钻孔技术,当然这个缺点就增加了成本,需要激光钻孔是因为机械钻孔有尺寸限制(机械钻孔最小能钻 10mil 的孔) ,除此之外,相邻或对角 PIN 间距很小而不能扇出走线,因此要引入激光钻孔技术。 PCB HDI激光钻孔可以直接在焊盘上打孔(盘中孔)或在焊盘一旁打孔,然后金属化孔洞,通过过孔就可以把走线引入内层。假如在设计中您已经引入激光钻孔技术(高端音频应用或移动电话常用这种技术), PCB成本不是主要问题,那么便可使用这种设计方案。如果设计必须要求低成本 PCB 设计方案(例如 LCD 显示屏),那么这种方案就不太适用了。另一种不常见的设计方案是交错焊球阵列( staggered-bump-array )的 WLP,示意图如图 7(仅示意,此图不是标准交错焊球阵列封装),通过交错 IC 上的引脚可以获得更多的布线空间,但并不是所有 WLP 芯片提供交错焊球阵列封装,对于交错焊球封装,在设计初始阶段,我们需要周密思考 Layout 方案。另外,我们也可以使用缺少几个引脚的 WLP 球栅阵列封装,如图 8(仅示意,此图不是标准缺脚 WLP 封装),这将有更大空间进行布线——或者打过孔或者在内层走更宽的线。不论哪种设计请周密思考设计方案。

结束语

在本教程中,提供了一些基本的设计准则和设计考量,对设计 0.4mm 和 0.5mm PIN间距的 WLP 器件有所帮助。焊盘类型( SMD 和 NSMD)、焊盘件允许最大布线宽度和焊盘间布线方案的选择(激光钻孔、交错阵列 WLP 等)在本文中都有提及,希望对设计 WLP 的工程师有所帮助。如有技术咨询小编,VX:ipcblcy