直到70年代末,未充分开发的毫米波(mmWave)频率范围(30至300ghz)仅限于小范围应用,如光谱学和军用雷达。前端的复杂性和对非标准制造技术的需求使得毫米波模块的成本无法满足大批量和消费市场的需求。自80年代初以来,研发机构展示了重大进展,并在半导体行业取得了进展,为广泛的应用开辟了新的领域:高数据率通信、汽车雷达、机载和导弹跟踪系统、空间光谱分析和成像。据估计,2013年,mmWave组件市场的全球收入约为1.16亿美元,预计到2018年将达到11亿美元,复合年增长率(CAGR)约为59%。2虽然业界认为这是一个巨大的经济机遇,但新兴应用正在带来具体的挑战在电气性能、紧凑性、集成可能性和系统可靠性方面。本文重点介绍中短程通信设备,这些设备说明了与无线收发器的集成及其与其他组件共存相关的一些技术挑战。毫米波频率下的短波长可以看作是集成无源元件的机会,这些元件的典型尺寸与标准电子封装兼容。在某些应用中,诸如波导管、连接器、非平面滤波器和大型天线阵列等体积庞大的元件仍然阻碍着向完全集成和小型化系统发展。就短程、60GHz通信而言,便携式设备有望成为未来十年的主要市场驱动力,因此需要完全集成、紧凑且高性能的收发器。关于天线,小型化过程受到散热器面积和可实现增益之间的基本关系的限制;这通常被视为无线收发器完全集成的瓶颈。

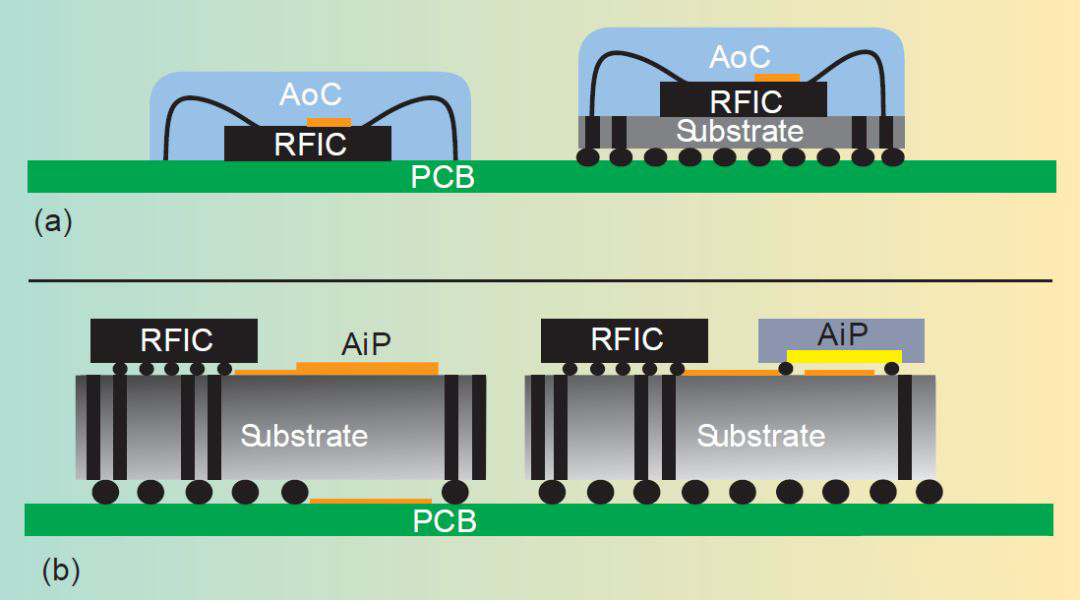

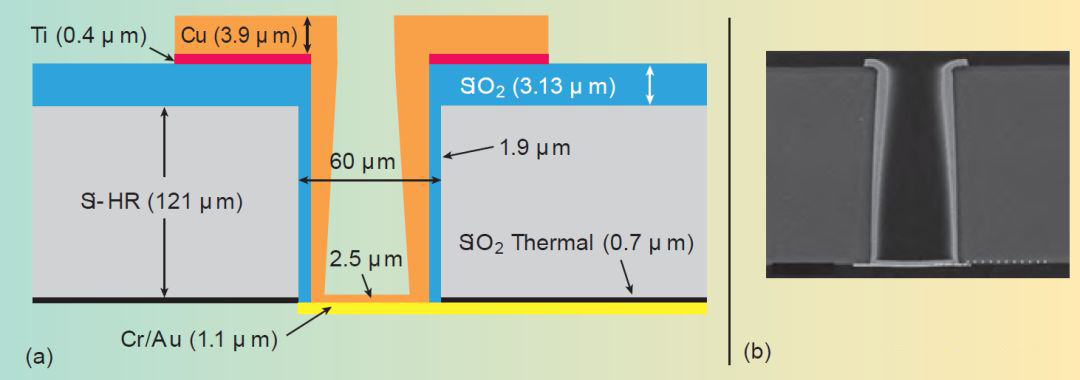

片上天线(AoC)方法包括将辐射元件直接集成到射频集成电路芯片的后端堆栈中,无论是采用CMOS、BiCMOS还是III-V工艺制造(见图1a)。这种解决方案的主要优点在于无需任何射频互连,并且所有射频和基带功能都可以在一个几平方毫米大小的模块上进行联合集成。然而,对于硅基AoCs,衬底的高介电常数(εr=11.7~11.9)和低电阻率(þ~10Ω∙cm)严重降低了匹配带宽和辐射效率。尽管如此,AoC天线的特性仍然可以通过局部地改变衬底的特性来改善。例如,可以通过蚀刻辐射元件下方的空腔或实现悬浮膜来实现。在这两种情况下,空气层的存在使介电损耗最小化,并降低有效介电常数。其他创新的解决方案包括使用离子注入工艺或上述耦合辐射元件的集成对硅衬底电阻率进行局部修改。

图1 AoC(a)和AiP(b)集成方案。

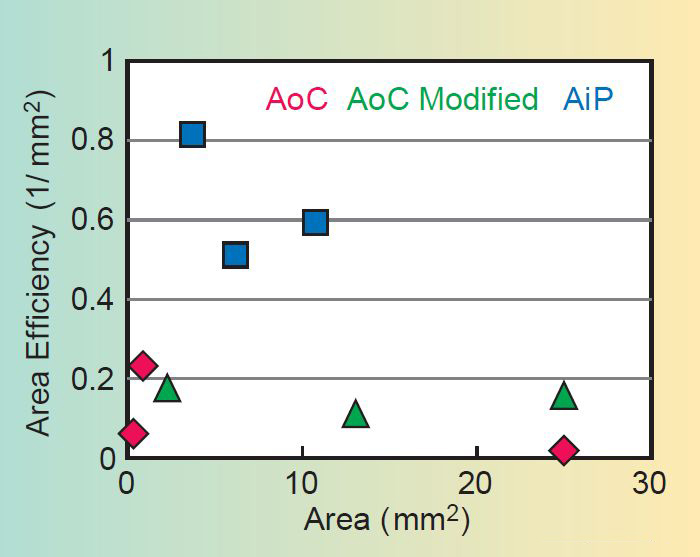

在天线封装(AiP)集成方法中,天线在独立于RFIC芯片的独立衬底上实现(见图1b)。该基板既可以专门用于辐射元件及其馈电线路,也可以作为收发组件和异构集成的封装。因此,AiP设计在mmWave收发器的3D集成方案中起着关键作用,同时提供了选择低介电常数和/或高电阻率衬底的额外自由度。另外,天线允许的面积比舞台允许的大。因此,综合天线性能比较的一个有效基础应该考虑到分配的面积,并且我们可以定义一个新的优点系数来归一化单位面积的实现增益(线性尺度)。图2描绘了60ghz集成天线的文献调查,表明由于使用低损耗衬底而不是CMOS级硅,aip的增益是aoc的2到4倍。

图2集成天线的典型面积效率。

为无线收发器的集成选择一种给定的技术是在几个限制条件之间的权衡:电气性能、热机械可靠性、紧凑性、可制造性和成本。今天的高密度互连(HDI)设计规则继承了成熟成熟的PCB技术,允许线和间隙小于40µm,以及直径小于100µm的微通孔形成,这符合毫米波集成的要求。此外,新一代多层有机(MLO)封装在薄膜和厚膜结构中都使用高质量的电介质。因此,标准的FR-4芯和重分布层层板正逐渐被低损耗的介质(如RO系列和液晶聚合物(LCP))所取代。例如,意法半导体公司利用一种基于RO4003C核对称叠加的技术,开发了一种60GHz、HDI、有机封装

在同样的背景下,陶瓷封装由于其化学稳定性、机械可靠性和密封装配的特性,在大约二十年前被引入以满足关键系统的需要。陶瓷加工允许创建各种通孔和腔体结构以及外部电容器和电感器的组装。标准多层陶瓷封装的垂直分辨率约为50µm。目前使用的两种主要多层陶瓷工艺是低温共烧陶瓷(LTCC)和高温共烧陶瓷(HTCC),最大共烧温度分别约为900°C和1600°C。虽然HTCC工艺为封装提供了很大的物理稳定性,但只有高熔点金属,如钨(Tf=3422°C)和钼(Tf=2623°C)可用于内层布线。不幸的是,与LTCC的铜、钛/金合金或银金属化相比,这些金属的导电率相对较低(分别为8.9×106和18.7×106 S/m),后者在高频下具有较低的导电损耗。在文献中可以找到来自业界的一些令人信服的贡献,例如IBM的60GHz LTCC模块以及MLO包(RO4000和LCP)

作为发展最快的封装技术之一,嵌入式晶圆级球栅阵列(eWLB)是一种结合了先进的再分配层处理和晶圆到模具转移技术的晶圆级封装方法。一个保护风扇的布线和保护聚合物的双重作用。eWLB工艺(包括凸点下金属化)继承自硅微制造线。由于使用了低应力模塑聚合物,eWLB封装可适用于具有天线阵列的大型封装,同时确保线/空间临界尺寸约为15µm。文献中可找到几种集成天线的毫米波封装演示,其中重点介绍了Linz演示的雷达应用University and DICE GmbH.6,7这项最新技术为3D集成提供了很有前景的前景,这得益于采用贯穿封装互连的封装对封装(PoP)组装的可能性。

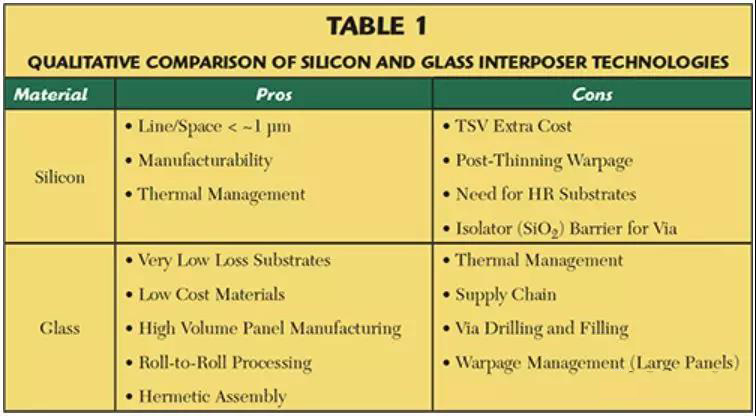

今天的硅后端生产线提供了一个大面板的微制造技术,以实现系统封装(SiP),如微机械加工,光刻,离子和激光蚀刻,以及一个大面板的沉积和层压技术。标准硅工艺可以很容易地达到微米级的分辨率,满足毫米波甚至亚太赫兹系统的要求。在过去的五年中,有机和硅插入器封装已经被ASIC和存储器应用所普及,但是最近的异构集成趋势显示出射频功能的更多展示以及玻璃作为高频应用的潜在候选的引入。

如前所述,硅微制造特别适合于毫米波应用,因为它具有成熟和标准的后端工艺的无与伦比的分辨率。与陶瓷(σ<20 W∙m-1∙K-1)和PCB材料(σ<1 W∙m-1∙K-1)相比,硅封装具有优异的导热性(25°C时σ~150 W∙m-1∙K-1),这在外部功率放大器与收发器芯片组装的典型场景中非常重要。

近年来,人们对2.5D和3D玻璃中间层及其提供的新的集成机会产生了越来越多的兴趣。玻璃基片具有优良的介电性能,具有低介电常数(εr~4~6,取决于成分和工艺)和低损耗正切值,是射频封装和无源器件集成的理想材料。表1比较了玻璃和硅中间层。用大面板代替晶圆有利于大规模生产,而在穿透玻璃通孔(TGV)钻孔和填充以及再分配层(RDL)处理方面取得了重大进展。今天的玻璃中介机构专责小组由朝日、康宁玻璃和3D玻璃解决方案等制造商和供应商以及领导国际中介机构财团的乔治亚理工学院等学术研究机构组成。然而,玻璃面板和加工设备的供应链并没有像硅、有机、陶瓷和eWLB技术那样得到很好的定义。随着下一代3D集成设备的出现,2.5D/3D玻璃插入器技术更可能达到完全成熟;目前,它足以满足高性能计算和数据中心等利基应用,在这些应用中,对成本的关注较少。8

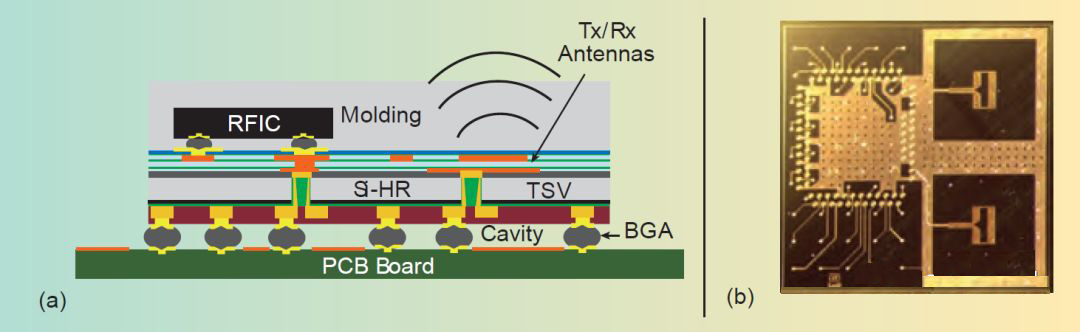

图3 60 GHz模块(a)的横截面示意图和硅插入器芯片(b)的显微照片。

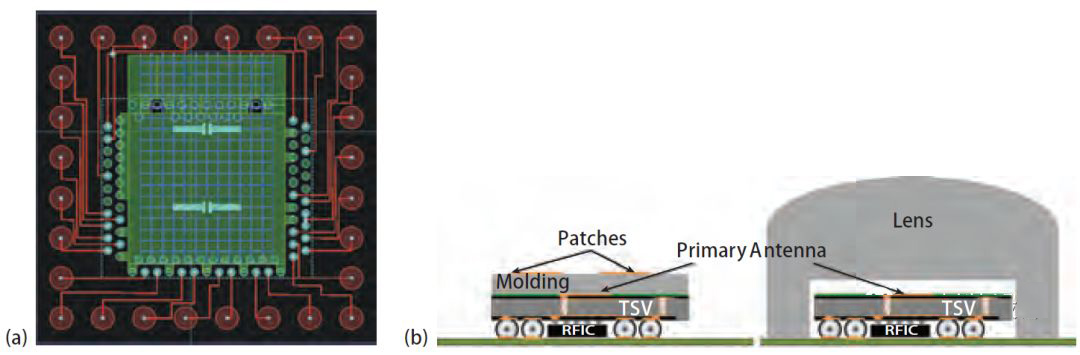

CEA-Leti开发的第一个全功能插入器封装基于高电阻率(ρ>1 kΩ∙cm)、120µm厚的硅衬底,具有两个正面和一个背面铜再分配层。插入器的每一侧分别带有所使用的凸点下金属化,对于射频集成电路倒装芯片(使用铜柱或微凸点)和使用球栅阵列(BGA)焊料球在主PCB板上组装封装。9插入器芯片的两侧使用直径为60µm(纵横比为2:1)的充铜穿透硅通孔(TSV)互连连接。插入器的总面积为6.5 mm×6.5 mm,是迄今为止报道的具有集成天线的最紧凑的60 GHz收发器。图3a显示了模块的未标度横截面以及用于确保组件完整性的插入器、射频集成电路芯片和成型聚合物。60ghz射频集成电路收发机采用65nmcmos工艺制造,两个折叠偶极子天线(用于发射和接收)位于前端的上部RDL层。由铜带和TSV阵列构成的保护环用于减轻两个背腔天线之间的表面波耦合(见图3b)。

图4 TSV鞋楦横截面示意图(a)和SEM视图(b)。

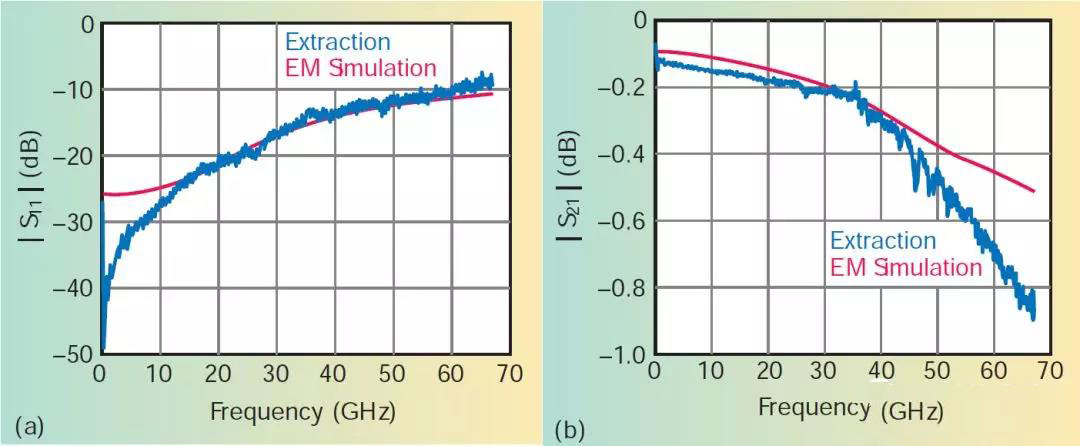

这个模块是一个典型的2.5D集成方案的演示,其中射频集成电路组装在插入器的顶部,并与天线偏移放置。垂直互连是通过最后一个过程使用Leti的定制TSV实现的。图4显示了TSV的横截面和SEM图像。虽然收发机中TSV互连的主要功能是驱动低频和基带信号,但测试车辆包含了额外的测试功能,以通过封装布线和背面天线馈电来研究它们对mmWave的适用性。已经使用射频探针测量和适当的去嵌入技术研究了TSV的电气性能,以提取单个GSG跃迁在直流至67 GHz的宽带响应。11跃迁在60 GHz时显示约0.6 dB的插入损耗,50Ω终端的阻抗失配是主要因素,i、 e.,0.46 dB(见图5)。除了宽带特性外,基带信号完整性还通过频域响应的傅里叶逆变换进行了研究。用5gbps伪随机二元序列(PRBS)进行的瞬态眼图分析显示,眼开度为96%。

图5 GSG配置中50Ω端接TSV过渡的反射(a)和传输(b)。

Leti正在进行的研究旨在创造新一代的毫米波插入器封装,与其他竞争技术相比,具有更好的电气和机械性能、合理的成本和可制造性。目前正在进行布局和预制分析的新模块与第一个演示器保持相同的总厚度;但是,由于集成的高阻抗表面(HIS)反射器设计(见图6a),总面积减少了约33%(从6.5 mm×6.5 mm降至5.3 mm×5.3 mm)。12正在评估两种改进方案,以提高天线性能,如图6b所示,第一个步骤是在插入器顶部层压成型聚合物,并处理金属寄生贴片以提高带宽。第二个目标是通过外部介质透镜提供中程通信能力(大约10米)。在这种情况下,60ghz的目标增益是15dbi。建议的透镜设计基于半球形和抛物线几何形状,采用PA6级机加工塑料(εr=4.3)。四种设计中的两种,直径为6毫米和1厘米的半球形透镜,已经过实验验证。第一次测量使用了一个开放的WR15波导馈源,在57到66GHz范围内显示出12到16dBi的增益。在系统级验证工作流程之后,这些透镜已与60 GHz QFN收发器模块13共同集成,并证明了一个发射透镜的范围提高了四倍,发射和接收透镜的范围提高了7.5倍

图6由A.Moknache(A)和基于HIS天线的新3D集成方案(b)提供的3D中间层简化布局。