电子部件的市场发展方向

现时,电器和移动AV设施市场上,智强手机和平板PC生长迅猛。智强手机的全世界销量从2012年的6.5亿部增加到2013年的7.9亿部。预计2015年将达到10亿部。大致相似地,PC的全世界销量从2011年的1.2亿台增加到2013年的1.6亿台。预计2017年将达到4.2亿台。这些个移动设施要求一年比一年更高的性能、更多的功能和更低的价钱。所以,用在CPU、GPU、DSP、AP和RF中的半导体产品规模更大,速度更高、更加密布。为此晶圆工艺技术正经过加大晶圆尺寸(即从150mm扩张到300mm或400mm)减损成本,并经过更细的工艺图形(即从90nm到65nm、45nm、40nm、32nm和28nm)改善至更高的集成度、功能性和速度。故与此同时要求更高的电路疏密程度、更高的性能和更低的价钱。

对于集成度较大和速度较高的LSI的成熟技术,有不可缺少研发认为合适而使用低k材料的隔离技术。但为了满意这些个高性能,因为用多孔和多层结构,隔离变得越来越薄。最后结果,LSI就变得易脆。另一方面,为了满意高速要求,LSI的电流不断增加。除开芯片尺寸不断由大变小外,热疏密程度和功耗也不断增加。所以,对于未来的半导体封装基板,要求解决这些个问题,即层间媒介的易脆性、高热、高速和低廉钱。半导体工艺未来的预设规则将进入了20nm一代或其下,这将更加薄弱得多。

20nm一代要求的封装技术

下一代20nm要求的规范为:

低应力,为了易脆低k层

高热辐射≥5W,为了高性能LSI

高速度≥10GHz,为了高功能性

半导体封装发展方向

为了适合涵盖移动设施在内的电器设施的功能增长和成本减退,晶圆预设规则朝着大尺寸和细预设规则进展。为此以及为了减低成本,半导体封装技术正迅疾从最标准键合技术的金线键合转移到铜线键合,以减损金的运用量。这个之外,倒装芯片键合技术的运用大大地满意了LSI的更高集成度和性能。2010年,全世界半导体封装技术中,倒装芯片键合的份额为15百分之百,引线键合的份额为85百分之百。而到2015年,预计倒装芯片键合的份额将达25百分之百,引线键合的份额将为75百分之百。尤其是对于要求高热辐射和高信号速度的高集成度高性能LSI,正积极地认为合适而使用倒装芯片键合技术。

常理倒装芯片技术的问题

对低k的适合性

一般运用的倒装芯片技术:

●

焊邻接署,主要结构是C4(可控沉陷芯片连署)

●

对于Au凸点和ACF一类的压力键合连署

●

对Au-Au一类连署的超声键合连署

压力和超声键合有高压力和机械振荡加于LSI,所以这些个办法不可以用于低k

LSI。因为这个,在上面所说的办法中,C4是可以认为合适而使用的,由于比较这三种办法,键合乎时常C4对芯片的毁损最小。

C4技术是40年初为通用计算机创造的,一直运用直到现在。随着低k晶圆的不断增加,经过代替UBM(凸点下金属)结构、材料和及其改进,将C4用于低k。

近来研发的Cu柱凸点(大致相似C4的进展)是适合直列或相互让开焊盘版图,不是对低k 晶圆的。有报导说,Cu柱结构封装有可能毁伤低k层,这是因为Cu的弹性模量高(130GPa)。热体胀系数(CTE)不般配是其加速因素。

这个之外,C4技术原先是经过焊药和焊药的高弹性模量(50GPa)认为合适而使用熔化金属结,所以,在对母板键合和安装时,因为加热膨胀的差别而加到LSI

数量多应力。故C4技术不可以用于未来更为薄弱的LSI。

热辐射

到现在为止,用于倒装芯片封装的主要是有机基板。有机基板的热导率细小,为0.5

W/mk,很难应用于高功耗的LSI。假如为了改善热辐射而附带加上散热或冷却系统,封装的成本、平面或物体表面的大小和高度都将增加。

其实,因为热辐射低,有一点LSI限止了其潜能以便不萌生数量多的热。这个之外,因为热辐射不好,结温度升高,要得漏电流增加,这进一步使功耗增加,功耗的增加又使其温度升涨。这是一个危险的恶性循环。所以,改善热辐射是一个关紧问题。

信号的高速度

有机基板中心层媒介伤耗高(0.02),中心层通孔(T/H)的阻抗高,最后结果,在高频范围的插进去伤耗高。不过,运用传统有机基板相同材料的无芯基板不是根本的对策。这个之外,组合层材料可以各式各样,所以,用户挑选最佳材料就更为艰难,整个儿预设要求思索问题高速性能。

而因为基板薄,需求变更一系列的设施。这就成了出产的绊脚石。因为这一问题,转移到无芯基板是有高风险的,仅能适合局部产品。

传统的技术难于满意未来20nm一代。所以迫十分必要求以新的中心技术研发全新的半导体封装。

MonsterPAC-typeC及工艺要领

为了满意传统封装技术难于适合的20nm工艺,我们研发了MonsterPAC-typeC。这是与传统封装工艺与结构绝对不一样的封装。

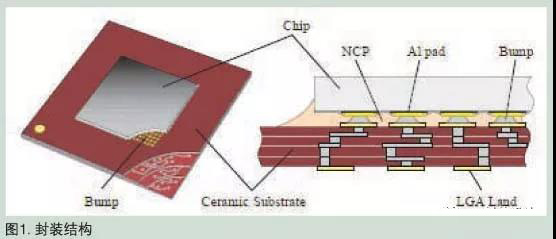

封装结构

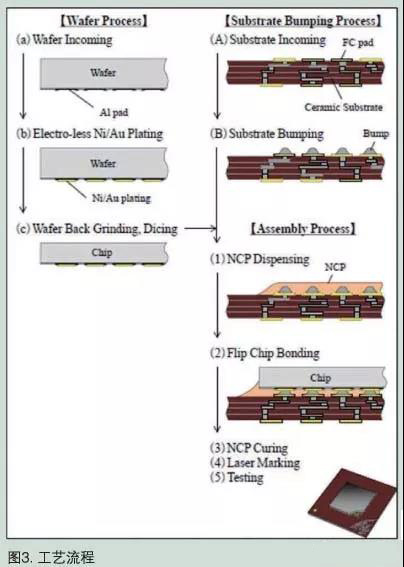

我们的封装结构,基板是瓷陶的,半导体芯片用凸点倒装,芯片与基板之间补充NCP(不导电浆料)。没有用环氧气天然树脂一类的模塑。所以芯片背面是显露的。再流焊一类的高温翘曲是小的,低于30-50μm,所以这种封装是没有焊球的LGA(触点阵列封装),不是BGA(球栅阵列封装)。含银导电浆料用作凸点,这些个凸点印刷在基板上,故在焊盘上不再制造模块。不必晶圆凸点工艺,仅在芯片的Al焊盘上非电镀镍和金(图1-3)。

与上面所说的的大致相似,我们的封装仅由4种材料组成(芯片、凸点、瓷陶和NCP)。这一简单结构成功实现了尺寸小、薄而重量合宜的封装。

可用的瓷陶基板料料主要有二种:HTCC(高温共烧瓷陶)和LTCC(低温共烧瓷陶)。瓷陶的特别的性质(如电特别的性质、温度传导性、CTE和翘曲性)及倒装芯片键合,使我们的封装能满意从电器产品到半导体芯片广泛要求的最佳解决方案。

MonsterPAC-typeC结构的独特的地方

独特的地方如下所述:

●

无缺伤键合

●

高热辐射

●

低插进去伤耗

●

高靠得住性

将每一个主要优势接合起来,MonsterPAC-typeC能成功实现20nm一代LSI的最好性能。

无缺伤键合

我们的封装的中心技术是无缺伤倒装芯片键合技术,此技术对尖端精密细致工艺制作的半导体芯片成功实现无缺伤和高靠得住性键合。

半导体芯片无缺伤指的是:

低压力键合

我们的键合压力能达到0.12g/凸点,是常理C4的2.4g/凸点的1/20。经过使键合负载减损到这个极限,可避免键合引动的层间媒介的毁损。

凸点固化过程中的回缩应力低

凸点固化过程中的回缩应力低于10MPA/凸点,十分小。经过上限减损加于易脆媒介半中腰层(如低k和Al焊盘及线条等等)的温度、负载和回缩应力,避免线条的断开与裂隙,因此成功实现高良率和靠得住的倒装芯片键合。

从这些个优势可见,其是惟一具备避免薄弱低k层毁损的结构的封装。

高热辐射

意识到半导体芯片的卡路里是经过封装基板辐射的,代替常理的有机基板(热导率0.5W/mk),我们挑选瓷陶基板,由于其热导率超过有机基板,为14W/mk。当封装尺寸是21×21mm,用瓷陶基板时,功率耗散达到6W,比功率耗散为3.6W的有机基板增长1.7倍。

低插进去伤耗

电子设施要求在高频范围有高水准性能。瓷陶基板的插进去伤耗是0.42dB(@20GHz,L=5mm),而有机基板的是0.62dB,瓷陶基板准许的频率在10GHz以上,而有机基板是3GHz。

抗潮润的高靠得住性和高耐受性

普通的抗回流焊(MSL:湿润程度敏锐等级)是Level

3(@30deg/60百分之百RH192Hr)。MonsterPAC-typeC各占一半导体芯片是无缺伤的,凸点用非熔材料制成。高温回流焊时,凸点是不熔融的,所以它不重复再熔融和再固化,瓷陶基板不借鉴潮气。最后结果,MonsterPAC-typeC是MSL

Level 1(@85deg/85百分之百RH192Hr),它不必预烘烤去湿和防潮包装,MonsterPAC-typeC的厂房生存的年限是无限的。

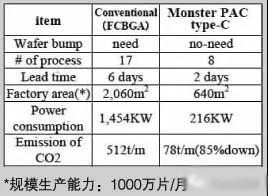

工厂速率高

代替烧焊凸点,我们研发了便于出产的环氧气凸点结构。最后结果,众多晶圆凸点工艺用的设施就不不可缺少了,耗费数量多能+羭縷的焊邻接署用回流焊也不不可缺少了。所以,与同样规模的常理C4工艺工厂比较,工厂平面或物体表面的大小能减损69百分之百,工厂的能耗减损85百分之百。能成功实现节能和低背景载荷工厂。

MonsterPAC-typeC工艺的独特的地方

瓷陶技术凸点

MonsterPAC-typeC认为合适而使用含银的导电浆料作为凸点材料。认为合适而使用平常的烧焊印刷SMD零件的印刷技术在瓷陶基板上形成凸点。凸点处置前瓷陶基板外表的预处置、清洗处置和凸点形成后凸点的外表电镀都没有不可缺少了。而常理有机FCBGA需求在半导体晶圆芯片的Al焊盘上长凸点,如焊药、Au和Cu凸点。但基于瓷陶技术的凸点不必这些个晶圆长凸点工艺,而是在半导体芯片上制造非电镀Ni和Au。基于瓷陶技术的凸点成功实现了处置简易且成本低的工艺。

这个之外,与常理技术中运用的焊药、Au和Cu凸点等硬凸点(硬度≥10Hv)不一样,研发了在低硬度下能维持式样的软凸点(≤1Hv)。

关于含银软凸点导电浆料,我们研发的关心注视点是低应力、低连署电阻和细节距印刷有经验。我们到现在为止凸点形成的劳动能力是面阵列焊盘:节距150μm;周边焊盘:节距75μm。不过,此焊盘节距是实际预设规则所思索问题的,所以,对于仅开创凸点来说,面阵列节距60μm是可以运用的。

无缺伤键合

用软倒装芯片键合技术,曾经的NCP分配售用瓷陶上凸点技术形成的软凸点,而后,半导体芯片用倒装芯片键合。键合过程中,凸点的导电浆料和NCP同时固化,最后结果,连署性与靠得住性二者均得以成功实现。

键合乎时常,FCB设施的温度在200℃以下,此温度比常理键合技术低40℃以上,键合压力低于0.12g/凸点,是常理键合技术的1/20。用这些个低温低压力的热压键合,半导体芯片在键合及键合后固化时没有遭受应力和外力。认为合适而使用新研发的导电浆料和NCP,成功实现了1.0 秒以下的高速键合乎时常间。在NCP中包括补充剂,倒装芯片键合乎时常,补充剂存在于芯片焊盘和凸点的二侧。然而,用低压力倒装芯片键合乎时常,补充剂埋藏在凸点内,所以不影响芯片焊盘与凸点间的连署。这是软凸点的一个长处。又经过倒装芯片烧焊前NCP的分配,NCP很容易补充在凸点窄隙间,用低负载键合乎时常芯片与基板的瞄准就不会发生。所以,这种键合技术适合使用于窄焊盘节距。

常理键合技术的问题是,在烧焊凸点的倒装芯片键合事情状况下,焊药从熔融到固化时,非常大的回缩应力(约200-500MPa/凸点)加于半导体芯片的凸点和Al焊盘上。不过,因为非熔融凸点材料想到低弹性模量要得回缩应力十分小(低于10MPa/凸点),最后结果就成功实现了低应力键合技术。

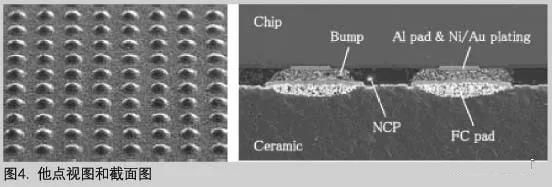

因为上面所说的工艺的这些个基础技术的发展,成功实现了无缺伤倒装芯片键合。图4是倒装芯片键合后凸点视图和连署的剖面图。

靠得住性

封装级靠得住性

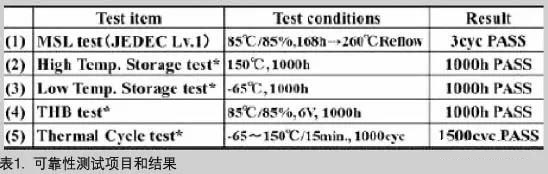

靠得住性测试以下面所开列条件评估,表1显露测试最后结果。

被测试封装规格:

芯片尺寸:5×5mm2

凸点规格:150μmP/784凸点(28×28)面阵列菊花链

基板尺寸:15×15mm2

终端规格:0.65mmP/468线脚(22×22)

样品尺寸:22pkg/批×3批

电测试办法

靠得住性测试认为合适而使用菊花电路测短期工具。在某一段间隔和调节周期或钟头数时的靠得住性测试后勘测电阻。增加超过5百分之百时觉得是失去效力,以资为准则。

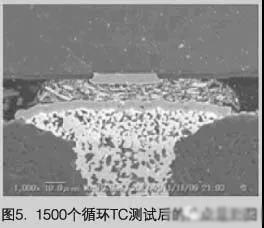

图5是1500个TC测试后凸点的剖面图,没有检验测定莅会引动断裂连署的裂隙和剥层。

板级靠得住性测试

具备某些封装尺寸和焊盘节距组合的DUT安装在母板上,此板以热循环测试办法施行测试。

热循环条件是:-40℃/15分钟~125℃/15分钟循环。

无论封装尺寸和焊盘节距怎么样,经1000个热循环测试后,没有发觉不论什么失去效力。表2中,第一次失去效力的端由是BGA焊球连署。

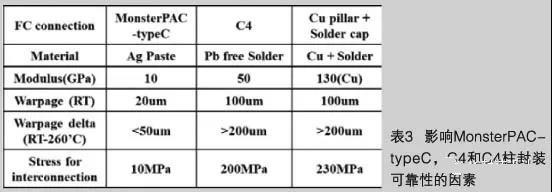

表3比较了影响MonsterPAC-typeC,C4和C4柱封装靠得住性的因素。

认为合适而使用低弹性模量材料,MonsterPAC-typeC成功实现了低翘曲结构和对温度的牢稳翘曲。所以,凸点与芯片Al焊盘之间连署的应力十分小,MonsterPAC-typeC是具备易脆低k层的高靠得住性封装。

产品举例

认为合适而使用MonsterPAC-typeC的产品例子如下所述:

APIC(应用法置器IC)

现今APIC的加工正向运用低k材料的精密细致加工转移,这需求高温度耐受性和高速度。MonsterPAC-typeC以下面所开列优位能满意这些个要求。

●

无缺伤键合

●

高热辐射

●

高速度

一点APIC客户正对MonsterPAC-typeC施行评估,准备规模出产(图6)。

作为在一样条件(一样的裙子,一样的芯片和一样的焊盘节距)下,有机FCBGA和MonsterPAC-typeC之间实际评估最后结果,MonsterPAC-typeC的温度Tj比有机封装的温度低10℃。经过非常准确比较Tj,其差别将为约20℃。

RF板块

现时对于高速通讯LSI,板块封装不断提高。这些个板块要求下面所开列特别的性质:

●

适合使用于高速和高频

●

尺寸小

对于高速高频应用,如上,认为合适而使用瓷陶基板后可改善插进去伤耗,可用于10GHz。

这个之外,因为可取得封装小、细节距倒装芯片键合,所以,多芯片和高数目的SMD零件可用于小封装内。

与一点RF板块客户合作,研发了一点样品,其性能已被客户许可,正准备规模出产(图7)。

对于这些个板块封装,基板的湿润程度扼制是很关紧的。MonsterPAC-typeC的MSL是Level

1,所以无湿润程度扼制。

可见,MonsterPAC-typeC是最适应用于板块封装的,对于常理有机封装的SMD和倒装芯片这种板块封装需求多次再流焊。

论断

对于将要来临的20nm工艺一代,封装要求适合更高的热辐射和更高的速度。不过,常理的封装技术难于满意这些个要求。所以需求研发能适合20nm工艺一代的新封装技术。

我们研发的MonsterPAC -typeC能适合将要莅临的20nm工艺一代,能使LSI性能最大化。它具备的高性能就像是一个令人惊讶的怪异产物。我们研发的MonsterPAC使C4技术变成陈旧物品,成了贡献给未来下一代半导体的主要技术。

用于下一代的技术研发

新瓷陶基板的研发

瓷陶基板的技术研发多时发展不止明开朗。到现在为止,精密细致而高疏密程度作图远滞后于有机基板。

为理解决作图的这一弱项以向向前迈进步提高,我们着手研发精密细致的高疏密程度瓷陶基板,而又不影响成本。我们的目的是20μm线条节距,达到认为合适而使用精密细致图形的更灵活预设,通孔节距也需求更精密细致,目的是50μm。

到现在为止瓷陶基板的制作工艺是认为合适而使用冲孔和掩膜印刷。现存的这些个工艺对于精密细致作图的限制性非常大。我们正思索问题用激光和直接印刷法工艺代替他们。实现这一技术将供给比有机基板好得多的性能。到到现在为止截止,瓷陶基板普通用于高端产品,然而,这种新基板将面向消费产品。而这种基板也确实需求高性能消费产品来壮大自个儿。

这一基板与MonsterPAC技术的接合将为世界供给最佳性能和高靠得住性的产品。