很多针对半导体和集成电路 (IC) 封装的热度量的范围介于 θja 至 Ψjt之间。 通常情况下,这些热度量被很多 用户错误的应用于估计他们系统中的结温。 本文档描述了传统和全新的热度量,并将它们应用于系统级结温 估算方面。

结至环境热阻,θja,是最常见的报告的热度量,它也是最经常被误用的。θja是安装在特定测试试件上 IC 封 装散热性能的度量。 θja的目的是给出一个封装的相对散热性能可与之进行比较的度量值。 因此,TI 器件的 散热性能可以与其他公司生产的器件相比较。 当两家公司使用标准化测试来测量 θja时,这是可行 的,JEDEC 在 EIA/JESD 51 系列文档中具体说明了此类测试。 然而,有时并未遵循 JEDEC 条件,并且对 于标准的偏离也未记录在案。 这些测试变化会对 θja的测得值产生很大的影响。 因此,除非使用 θja值来公布 测试条件,否则这些测试条件值得怀疑。

使用以下步骤来执行 θja测量(总结自 EIA/JESD 51-1):

Step 1. 一个部件,通常是一个安装在测试版上的集成电路 (IC) 封装,此封装包含一个能够耗散功率并 测量最大芯片温度。

Step 2. 测试芯片的温度感测组件被校准。

Step 3. 封装/测试版/系统被放置在一个不通风 (θja) 或空气流通 (θma) 环境中。

Step 4. 一个已知功率在测试芯片内耗散。

Step 5. 在达到稳定状态后,结温被测量。

Step 6. 已测得的环境温度与测得的结温之间的差异被计算出来,并除以耗散的功率,从而得出一个以 °C/W 为单位的 θja值。

很不幸的是,θja常常被系统设计人员用来估算他们系统中所使用的器件的结温。 这个等式通常被认为可有效 地根据 θja来计算结温:

![]()

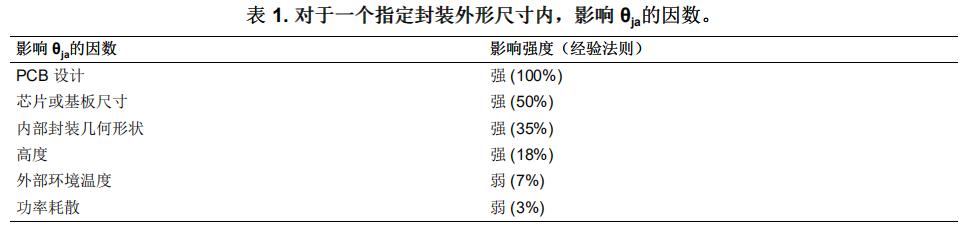

这是 θja热参数的误用,这是因为 θja是一个并不专属于封装的可变函数,它也是诸如已安装部件上印刷电路板 (PCB) 的设计和布局布线等很多其它系统级特性的函数。 实际上,测试板是一个焊接在器件引线上的散 热片。 对测试板的设计或配置的改变将改变散热片的效率,并因此改变 θja。 事实上,在不通风的环境 中,JEDEC 定义的 θja测量,大约芯片产生的功率的 70-95% 由测试板耗散,而不是从封装的表面散发。 由 于系统板很少接近被用来确定 θja的测试试件,θja使用公式 1的应用将导致极端错误的值。 表 1列出了在所有材料保持恒定时,将影响指定封装外形尺寸内 θja的因数。 第一列列出了因数,而第二列 给出了凭经验法则估算出的此因数所造成的影响。

根据 θja并不是封装本身的特性,而是封装,PCB 和其它环境因素的特性这一事实,它最好用作不同公司的 封装散热性能的对照。 例如,如果相对于竞争对手所公布的 45°C/W 值,TI 针对一个封装公布了一个

40°C/W 的 θja值,那么 TI 部件在应用中有可能比竞争对手的部将多冷却 10%。

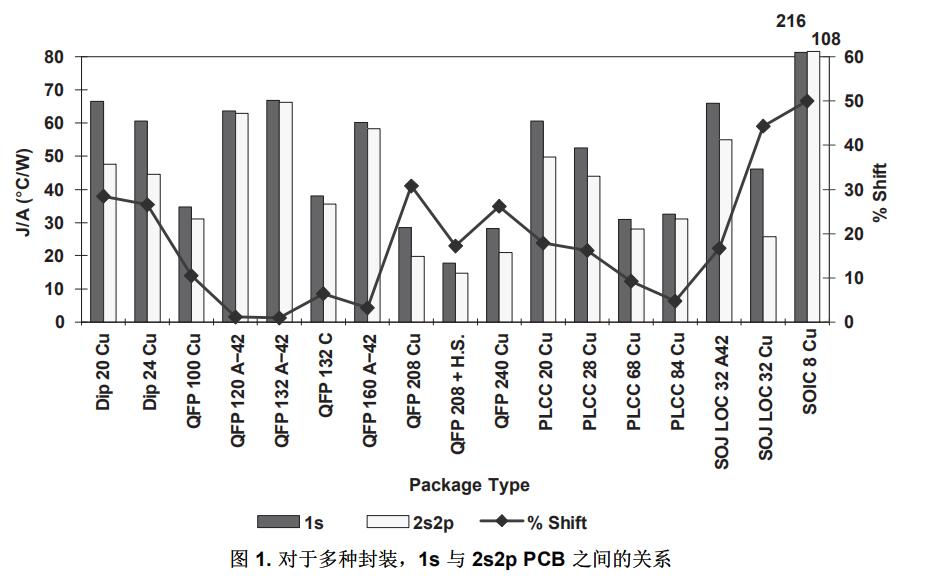

最近,JEDEC 已经建立了一组标准用来测量并报告 IC 封装的散热性能。 这些标准全部属于 EIA/JESD 51项下。 EIA/Semi 也具有一组与 JEDEC 版本完全不同的热标准。 由于 θja不是一个常量,所以在尝试一个比 较前,确定用来计算或测量 θja的标准就变得十分关键。 在 JEDEC 技术规范内,允许两个测试板类型。 一个 1s(单信号层)配置给出了一个针对适度板上组装、 多层系统级 PCB 应用的典型使用值。 一个 2s2p(双信号层、双隐蔽式电源层)配置给出了一个最佳情况 性能估算,假定采用了具有隐蔽式电源和接地层的稀疏板上组装、高走线密度板设计。图 1显示了对于 17中不同封装类型,针对这两个电路板的 θja差异。 请注意,针对这些模型,所有材料和封装几何图形保持恒定。

图 1. 对于多种封装,1s 与 2s2p PCB 之间的关系 如图所示,单单一个 1s 与 2s2p 测试卡结构间关系的函数即可产生最多 50% 的 θja变化。

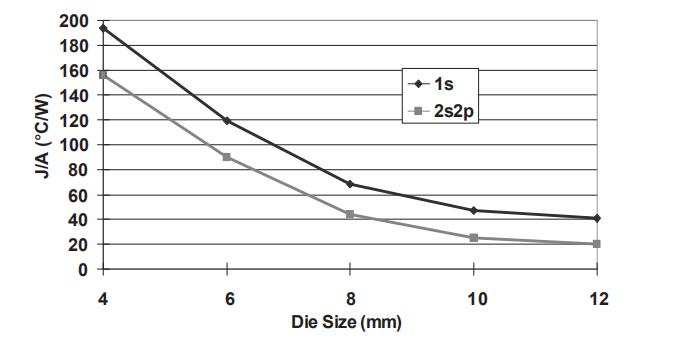

如果芯片或基板足够大的话,一个封装内的芯片或裸片基板都可发挥均热片的功能。 这个均热片有两重功 效。 首先,它将能量从芯片热点分散到封装表面上更广阔的面积上,从而增加对流能量损耗。 第二,它增 加了基板到引线指或封装焊球的热传输,然后将热量传导至 PCB。图 2显示了卷带式空间阵列芯片级封装(CSP) 中芯片尺寸对 θja 的影响。 如图所示,针对此封装的 θja随芯片尺寸变化了大约 8 倍。 如果计划缩小 芯片尺寸,那么很有必要重新测量或重新计算一个封装的 θja。

图 2. 芯片尺寸对 CSP 的影响

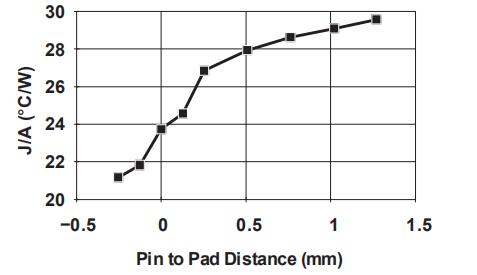

这个话题是指一个封装内的布局布线,不管它是一个传统的引线框架封装、小型基板(S 基板)封装、引线 片载 (LOC) 或球状引脚栅格阵列 (BGA) 封装。 越来越多普通的几何形状也可以对封装散热性能产生主要的 影响。 这些可以包括如图 3中所示的封装中引线顶端与芯片基板间的距离,或者甚至是基板和引线指之间的 引线框架。 后者是薄型封装中特别重要的热标准。 在 BGA 封装中,内插板走线布局在将热量从芯片分散至 封装焊球,再传导至 PCB,的过程中十分重要。

图 3. J/A 与 引脚到基板距离间的关系

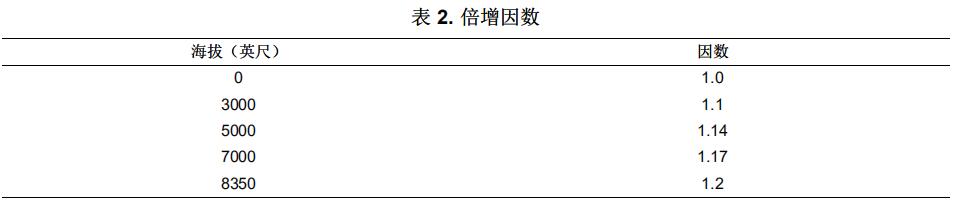

由于周围环境的空气压力随着海拔的变化而变化,空气的冷却效率也在发生变化。 IBM [1]曾经证明在海拔8000 英尺高运行的器件会比在海平面上运行的器件热 20%。 其它调查已经显示当在不同的海拔使用器件 时,风扇性能和内部底板空气流动会有很大变化。 应该将这些影响考虑在内,特别是当未从散热的角度考虑 系统设计时更是如此。 很多主要的系统公司具有压力室以便在不同的有效海拔来测试他们的系统。 通常情 况下,这些公司用器件装备他们的设计来测量器件运行在不同分压下的内部组件温度。表 2列出了取自 IBM公司的倍增因数来降低 θja额定值:

由于空气的密度、粘度和热容量随着温度的变化而变化,所以当我们发现 θja随着周围温度的变化而变化时就 不应感到意外了。 TI 热实验室中的试验显示当在 0-100°C 的环境温度范围内测量时,θja会提升 10-20% –也 就是说,100°C 环境温度中的 θja大约比 0°C 环境温度中的 θja提升 20%。

器件的表面温度促使封装的对流和辐射能量损失。 封装表面变得越热,到周围环境的对流和辐射热损耗就越 有效。 因此,当封装的功率加倍时,θja提升了大约 3% 这一情况就很正常了。 对于极低功率耗散,θja有时 比额定封装功率水平高 2-3 倍。

Theta-ja (θja) 是一个系统级参数,这个参数在很大程度上取决于上面部分中所描述的系统参数;因此,有时 定义一个 Theta-ja 效用, θjaeffective,会比较有用,这只是运行在相关系统中的器件的 θja。 如果θjaeffective可以 从系统中的热建模或测量中估算的话,可使用公式 1来计算结温,前提是系统上周围组件的功率不发生变 化。然后公式 1变成:

![]()

导致一个 θjaeffective的系统条件应该在报告一个 θjaeffective时始终被定义。

结至外壳热阻度量最开始是设计用来在散热片被连接后估算一个封装的散热性能。 JEDEC JESD51.1 规 定,Theta-jc 是“一个半导体器件的运行部分到最近接芯片安装区域的封装(外壳)表面的热阻,此时同一表 面被适当散热以大大减少表面上的温度变化。” 虽然现在没有定义 θjc的可用 JEDEC 技术规范,但是确实有 一个非常通用的测量 θjc的行业做法。 在以下部分中描述了这个做法。 SEMI 标准 G43-87 描述了一个测量 θjc的液体浸入方法。 虽然 TI 已经在过去使用了这个方法,它只具有历史价值,而并不在这里详述。

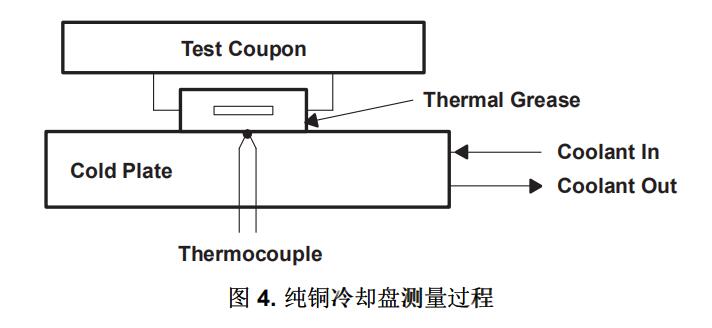

这个方法强制几乎所有测试器件的功率通过一个已定义的封装表面。 根据器件上散热片的安装方法,这也许 是封装的最底层。 总的来说,它是封装的顶层表面。θjc在确定芯片和安装散热片的表面之间热阻方面比较有 用。总结起来,此过程是:

Step 1. 通常包含一个热测试芯片的 IC 封装被安装在一个测试 PCB 上,它通常是 1s JEDEC 定义的测 试板。

Step 2. 当外壳顶部被测量时,此封装在一个dead bug布局中与一个纯铜冷却盘(一个具有循环恒定温 度液体的纯铜块)压配。 否则,当封装的主冷却路径通过一个焊接盘进入 PCB 时,一个到封 装底部的纯铜冷却盘触点通过 PCB 提供。

Step 3. 硅树脂散热油脂或其他散热接口材料提供冷却盘与封装间的散热连接。

Step 4. 在测试试件周围提供了隔热以大大降低寄生热损耗。

Step 5. 为器件加电。

Step 6. 测试芯片的结温被测量。

Step 7. 通过压在这个表面上的热电偶或其它温度传感器,与冷却盘接触的封装表面的温度被测量。

Step 8. 通过将测得的温度 delta 除以已耗散的功率来计算 θjc。

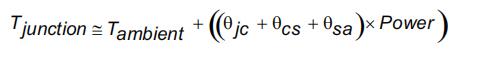

之前对 θjc已过时的理解显示在公式 3中。

![]()

在这里,被报告的封装散热性能 θja是两个电阻,θjc和 θca的和。θca代表外壳至环境热阻,它由这个等式定 义。 对于具有金属罐的封装,这也许是个有效的等式,在这类封装中,温度相对恒定,与 PCB 没有热连 接。 但是,这些条件并不适用于当今与 PCB 紧密连接的塑料或陶瓷封装。 在现在的封装中,大散热变化率 很常见,所以公式 3的意义值得商榷。 一个传统的,但是无效的,θjc的用法就是计算运行在一个系统中的芯片的结温。 运行在系统中的器件外壳温 度使用热电偶,IR 摄像头或荧光探测器。 下面的等式被错误地用来计算结温:公式 4:

![]()

这里的错误在于,在典型塑料封装中,只有一小部分热能量从封装的顶部对流和辐射出去。 很多模型已经显 示,芯片 60-95% 的热能量从封装连接的 PCB 上对流和辐射出去。 如果用户认为全部功率从顶部表面耗散 的话,用公式 4计算出的结温要高于实际温度。 在具有热工裕量的设计中,这是个麻烦,但是在没有热工裕 量的设计中,可采取错误限制。 θjc的这个限制被全新的热度量,Ψjt,所克服,在下面对它进行说明。 公式 5显示了 θjc针对这些实例的适当应用,此时一个高效散热片被应用到器件的顶部,对于这个器件,θjc比 θja小:

在这里,θsa是散热片的散热片至环境性能,而 θcs是散热连接材料的外壳至散热片热阻(请见公式 7)。 环 境温度是用于描述 θsa特性的位置,通常距离散热片有一定的距离。 这个等式是针对封装对准确的等式,在 这里,θjc比 θja小,这意味着当采用充足有效的散热片时,大多数热量可以通过封装的表面散发出去。 公式 6显示了一个比公式 5θja,θjc或 θsa的任一组合更加准确的近似值,如果 θja对系统配置已知的话:

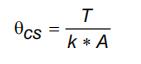

θcs的最好方法是实际测量 θcs值,但是如果这是不可能的话,公式 7可被用来估算 θcs。 请注意,由于 忽略了任意两个表面之间可产生的热连接电阻,这仅仅是一个估算值。

其中:

T = 封装和散热片之间连接层的厚度

K= 热连接材料的总体散热传导率

A = 散热连接材料的应用面积

某些封装具有诸如散热块或外露垫等构造,这些构造为封装的顶部,底部或上下端散热。 当只有单个表面用 于散热时,根据 JEDEC JC51.1 技术规范,这个表面就是将被用于 Theta-jc 的表面。 某些时候,设计人员 希望也将封装顶部的散热片包括在内,虽然外露垫被焊接到 PCB 上。 在这样的实例中,为了避免在提及表 面时造成的混淆,对 Theta-jc 顶部 (θjctop) 和 Theta-jc 底部 (θjcbottom) 进行定义是适当的做法。 顶部表面是背 对着 PCB 的封装表面,而底部表面是面对 PCB 的封装表面。 当 θjcbottom被测量时,制作了一个具有切口的 特殊 PCB 以实现底部封装表面与纯铜冷却盘的接触。 当与纯铜冷却盘接触时,封装底部表面读取的温度成 为外壳温度,这个温度用来计算外壳和芯片结温之间的温度 delta。

应该注意的是,德州仪器 (TI) 有时已经使用 Theta-jp 或结至外露垫的命名法,来表示结点与封装外露垫之 间的热阻。 不论这个垫是暴露在封装的顶部或底部,这个命名法都已经被使用。

在一次为用户社区提供热度量以从测得的外壳温度估算使用中的结温的尝试中,一个全新的热度量,Ψjt,已 经被业界采用 (EIA/JESD 51-2)。 这个度量由希腊字母 Psi(Ψ) 而不是 Theta (θ) 定义,这是因为 Ψjt不是真正地热阻。

下面从 EIA/JESD 51-2 中总结了 Ψjt 的测量过程:

Step 1. 在一个测试板上安装一个测试封装,此封装通常包含一个散热测试芯片。

Step 2. 将一个细规度热电偶导线(36 规度或更小)黏结到封装的顶部中央。

Step 3. 沿着封装来热电偶导线以大大减少热电偶的散热性。

Step 4. 在测试芯片中耗散功率。

Step 5. 测量测试芯片结温和热电偶温度。

Step 6. 将结温和表面温度间的散热变化率除以耗散的功率。

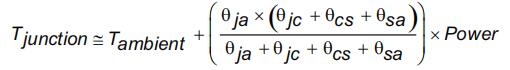

为什么 Ψjt不是一个真正的热阻? 在上面的过程中,测试芯片所产生的热能量被允许沿着优先散热传导路径 正常流动。 从芯片流动到封装顶部的热量在测量中是未知的,但是假定为器件的总功率,以实现 Ψjt计算的 目的。 很明显,这个假设是无效的,但是当用这种方法进行计算时,Ψjt成为一个非常有用的数,这是因为 此试验配置与 IC 封装的应用环境十分类似。 这样的话,测试期间,从芯片流向封装顶部的能量数量与流进 一个应用环境中的能量分割类似。 与公式 4相比,使用公式 8可以非常接近地估算实际结温。

![]()

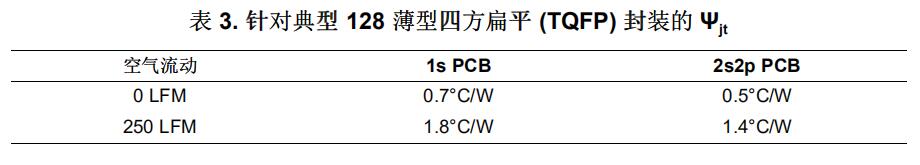

对于塑料封装,相对于 4-15°C/W 的 θjc值, Ψjt的典型值为 0.5-2.0°C/W。较薄的封装具有比较厚封装更小 的 Ψjt值。 具有嵌入式散热块的封装的 Ψjt值接近为零。 您应该注意到,Ψjt随着电路板结构和空气流通情况 的变换而变化,如表 3中所示。 这些值通过建模获得。

外壳温度被定义为器件顶上最热的温度。 在大多数实例中,这是器件的顶部中心或器件的盖子。 可使用一 个红外 (IR) 摄像机、荧光探测器、热电偶或 IR 枪式探测器(具有 4mm 直径的最大观察视野)来执行外壳 温度测量(为了实现准确性),提及这些测量设备只是为了列举几个技术。 当热电偶被选中作为执行测量的 技术时,应该使用细规度导线(36 至 40 规度,J 或 K 线)以大大减少热电偶的局部冷却。 您应该意识 到,如果外壳温度由大于 36 的规度热电偶测量,热电偶吸收表面的热量,冷却正在被测量的位置,从而使 公式 8的计算无效。 使用一个大规度热电偶来测量封装顶部表面所带来的影响是可观的,从而将环境和实际 表面温度之间的 delta 减少 50% 或者更多。 即使当 36 规度或者更小热电偶被采用时,也会有错误发生。

如果正在使用一个热电偶,它应该被接至封装表面的中央 (±1mm),一侧上的热传导环氧树脂的微珠小于等 于 2mm x 2mm。 不建议将热电偶捆扎在封装表面。 为了大大减少热电偶的散热性,导线应该沿着封装的 对角线穿过,向下到达 PCB 表面,并且在从 PCB 竖起前长度要超过 25mm。 通过使用胶带可将热电偶导 线钉在 PCB 上以实现这个走线的目的。 热电偶导线规度的不正确使用会导致 5-50% 的测量错误。 当使用一个 IR 摄像机或 IR 枪式探测器时,请确保根据被测量表面的发射率来校正读数。 详细信息请参见 您的工具文档。 由于散热片覆盖了将被测量的表面,所以测量应用了散热片的外壳温度意味着特别的挑战。 如果您希望在应 用了散热片的表面上测量外壳温度,建议使用以下步骤。

Step 1. 在散热片上钻一个直径 1mm 或更小的孔,当散热片被连接上时,使这个孔位于封装的中央。 一定要在将散热片连接到封装之前在散热片上打孔。 如果压敏黏合剂被用来固定散热片,请打 孔钻过这个黏合剂。 请确保没有金属毛边或其他材料干扰贴合表面。

Step 2. 将散热片贴在封装上。 如果环氧树脂被用来散热片黏贴,用蜡、泡沫或其他材料填充步骤 1 中 钻出的孔以确保这个孔不会被环氧树脂填满。 请小心,不要使这个材料污染散热片黏贴表面。

Step 3. 用散热油脂来填充这个孔。 如果这个孔被塞住以避免环氧树脂填充,请一定清空这个孔。

Step 4. 将一个上面描述的细规度热电偶穿过这个孔,并且用一滴环氧树脂或胶带固定。

当打算应用散热片时,不应使用 Ψjt。 而应使用公式 5和公式 6。

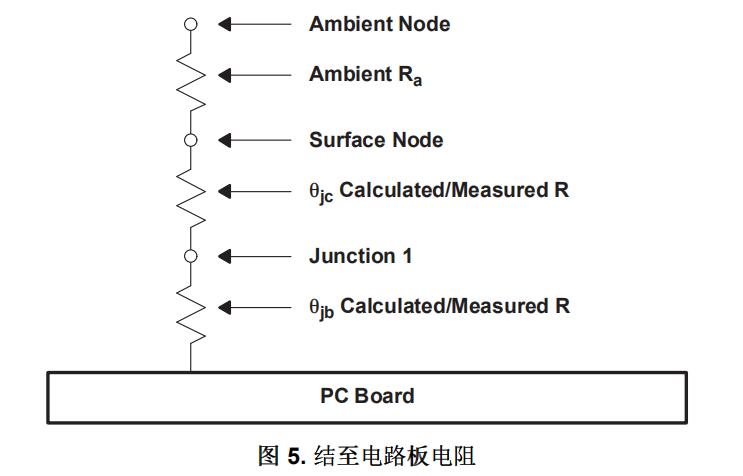

结至电路板热阻,或结至引脚热阻,尝试用一个数字表示封装和电路板之间的热阻。 现实中,结至电路板热 阻是分布的,具有不同的电阻路径,例如结至引脚至电路板以及结通过塑料通过空气至电路板。 然而,一个 诸如 θjb的单热度量在根据以下简单 3 电阻器散热近似值来第一遍估算结温时比较有用。 在这个模型下,结 至电路板电阻就是测得的或建模获得的 θjb值。 结至外壳表面的电阻就是测得的或建模获得的 θjc值。 环境电 阻,Ra,可从封装顶部的对流热损耗和辐射损耗计算得出。

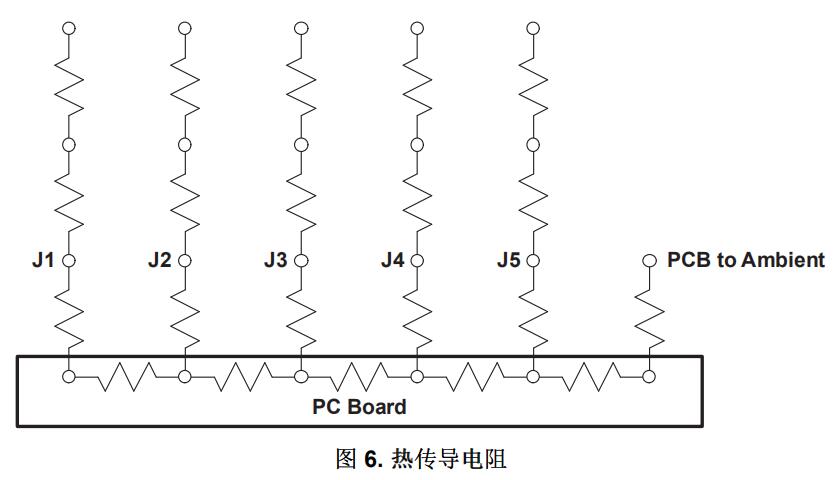

对于一个完整的系统仿真,电路板应该进一步包含于电路板材料、走线、热导孔等相关的热传导电阻,以实 现图 6中显示的系统中的每个封装的结温计算。 PCB 至环境的热阻应该由很多分布电阻表示,对于这个 图,这些分布电阻被搜集在一起成为 PCB 至环境电阻。

使用 θjb在一个比上面显示的模型更加详细的模型中计算系统结温的问题在于确定如何重新分配信号热阻节 点,这个节点将 θjb端接在系统 PCB 上的封装上。 在使用空间阵列封装的情况下,芯片、封装和电路板紧密的热连接在一起,以至于将封装热连接表示为一个点是错误的。 一个常见的解决方案是将封装下方的 PCB表面与一盘非常高的热传导性材料短接在一起。 这引入了错误。 另外一个解决方案是在电源和 PCB 之间包 含一个封装尺寸大小的固体材料块。 计算了这个块的传导性以给出电源和系统电路板之间的合适 θjb热阻。 在欧盟的 ESPIRIT 集团的赞助下,已经在欧洲完成了被称为紧凑模型的封装,此封装使用少量的模拟热阻[2]。 紧凑模型使用一个更加精密的热阻网络来更加准确地表示封装散热性能。 现在,紧凑模型常见于大多 数系统级散热建模工具,并可向 TI 索取。

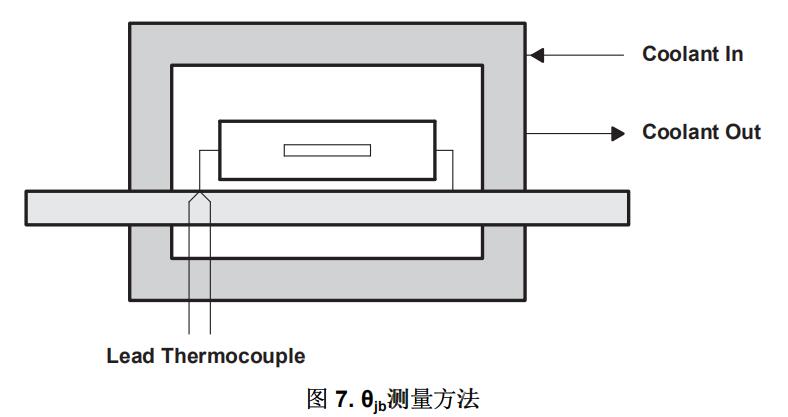

测量 θjb的主要方法如下:

Step 1. 包含一个散热测试芯片的测试包被安装在测试板上。

Step 2. 一个细规度热电偶(36-40 规度)被粘结或焊接在最靠近芯片的器件引脚上。 在使用 BGA 封 装的情况下,热电偶被焊接或粘结到最接近芯片的封装边沿下的走线上。

Step 3. 电路板被固定在一个特殊的双冷却盘装置内,此装置在封装和冷却盘表面具有隔热层,但是在 冷却盘与电路板之间有热触点。 冷却盘为 PCB 散热。

Step 4. 功率在芯片内耗散。

Step 5. 芯片和引脚的温度被监视。

Step 6. 当实现了稳定状态时,结至引脚间温度的 delta 除以总功率耗散。 在 EIA/JESD 51-8 中对这个过程进行了更加准确的定义。

、

Ψjb 的概念与 Ψjt相似。 它是指结温和中央封装引脚温度间差异的测量,除以器件的功率耗散。 这样的话, 它不是真正的热阻,这是因为通过这个热阻的功率实际分割是未知的。

Ψjb使得系统设计人员能够用一个细规度热电偶来测量电路板温度,并反过来使用公式 9计算结温。 应该注 意的是,由于器件热量的 70%-95% 由 PCB 散发,Ψjb接近 θjb。

![]()

Ψjb的测量由 EIA/JESD 51-6 定义。 在选择热偶类型、规度时应该小心,并且在将热电偶穿过 PCB 时,应 该采用与热电偶测量外壳温度用于 Ψjt测量时所用的方式相类似的方式。 在进行 Ψjt测量时,IR 摄像机或光 线探测器可被用来测量 PCB 温度。 然而,由于图像采集点的尺寸太小,所以 IR 散热枪式探测器不太适 用。

标记有工业用温度范围的德州仪器 (TI) 器件工作在 -40°C 的 85°C 环境温度下,此时要小心谨慎以确保不超 过绝对最大运行温度。 请注意,系统级散热设计被要求规定不超过最大运行器件温度,即使输入环境空气温 度介于 -40°C 和 85°C 之间时也是如此。 当工业用温度范围被指定时,最小运行温度为 -40°C。 由于没有 定义工业用温度含义的行业标准,所以公司和公司之间会有可能存在变化。 标记有商用温度范围的德州仪器 (TI) 器件工作在 0°C 的 70°C 环境温度下,此时要小心谨慎以确保不超过绝 对最大运行温度。 当商用温度范围被指定时,最小运行温度为 0°C。

结温— 封装内硅芯片的最高温度。

建议运行温度— 器件在设计使用寿命内持续运转在指定性能时的结温。 如果器件在高于这个温度的环境内 运行,器件的可靠性有可能会降级。 某些器件将在这个温度以上不能工作。 其它偶尔会用到的措辞 是建议持续运行结温。

绝对最大运行温度— 器件可供电运转的最大结温。 如果器件持续运转在这个温度下,器件的使用寿命会减少。 其它偶尔会用到的措辞最大运行温度。

绝对最大结温— 超过这个温度,器件会出现损坏。 器件在这个温度上有可能不能工作或达到预期的性能。

最大外壳温度— 有时,给出一个最大外壳温度,而不是指定最大运行温度。 在最大外壳温度上运行器 件(无散热片)会导致芯片运行在建议运行结温上。 有时,这被写成 T外壳。 T外壳通常在封装顶部表面 的中央进行测量。

周围空气温度— 对个源列出了不同的位置以确定周围环境温度 NEBS 将进入系统盒中的空气温度指定为环 境空气温度。 AEC 将器件下方的空气温度指定为环境空气温度。 JEDEC 指定 PCB 之前的空气流温 度。 有时,在器件的上方测量环境空气温度,作为对环境的理解。 这些测量位置中的每一个都产生 一个针对环境空气温度的不同温度。 在任何情况下,影响器件稳定性和功能性的关键因数是结温,而 不是环境温度,理解这一点很重要。 由于结温和环境温度是互相关联的,在采取任何系统级分析前, 澄清环境温度假设十分关键。