这一趋势对印制电路板(PCB)的线路精度、铜层质量及基板适配性提出了更高要求 —— 传统减成法工艺已难以满足线宽 / 线距 25μm 以下的高端 PCB 制造需求,而PCB 半加成法工艺(SAP/mSAP) 凭借其高精度、高稳定性的技术特性,逐渐成为高端 PCB 及类载板(SLP)制造的核心技术方案。

本文将从工艺概念界定、核心原理、技术优势、应用场景、常见问题解决及未来趋势六个维度,全面拆解 PCB 半加成法工艺,为 PCB 制造企业、电子设备厂商及技术选型者提供系统性的技术参考。

在深入探讨工艺细节前,需先明确PCB 半加成法工艺的核心分支 —— 标准半加成法(SAP)与改良型半加成法(mSAP)的定义及差异,避免技术术语混淆。

SAP 是半加成法的基础形态,核心逻辑是 “先形成薄铜种子层,再通过电镀加厚目标线路,最后去除非线路区域薄铜”。其技术定位为 “中高端 PCB 制造方案”,适用于线宽 / 线距 30-40μm 的高密度互连(HDI)板,如服务器 PCB、中高端智能手机中层板等。

mSAP 是 SAP 的升级迭代技术,针对 “更高精度线路制造” 需求优化而来。其核心改良点在于 “初始铜层厚度缩减” 与 “蚀刻工艺优化”—— 初始化学镀铜层厚度从 SAP 的 2-5μm 降至 1-2μm,同时引入 “差分蚀刻” 技术,大幅提升线路边缘精度。mSAP 的线宽 / 线距能力可达 15-25μm,是类载板(SLP)、5G 毫米波模块等高端产品的核心制造工艺。

对比维度 | 标准半加成法(SAP) | 改良型半加成法(mSAP) |

初始铜层厚度 | 2-5μm | 1-2μm |

线宽 / 线距能力 | 30-40μm | 15-25μm |

蚀刻方式 | 常规闪蚀 | 差分蚀刻(精细控制) |

核心优势 | 成本适中、工艺成熟 | 超高精度、线路均匀性好 |

适用产品 | 中高端 HDI 板、服务器 PCB | 类载板、5G 模块、汽车高端 PCB |

无论是 SAP 还是 mSAP,其核心逻辑均遵循 “‘种子层 + 电镀加厚’替代传统‘蚀刻减薄’”,但在流程细节上存在差异。以下分别拆解两种工艺的关键步骤及技术要点。

SAP 工艺需经过 6 个关键步骤,每个环节的参数控制直接影响最终 PCB 质量:

• 步骤 1:基板预处理

选用玻璃纤维布基板(如 FR-4)或高频基板(如 PTFE),通过 “脱脂→微蚀→粗化” 处理,去除基板表面油污及杂质,增加表面粗糙度。此步骤需控制微蚀深度(通常 50-100nm),确保后续化学镀铜层的附着力。

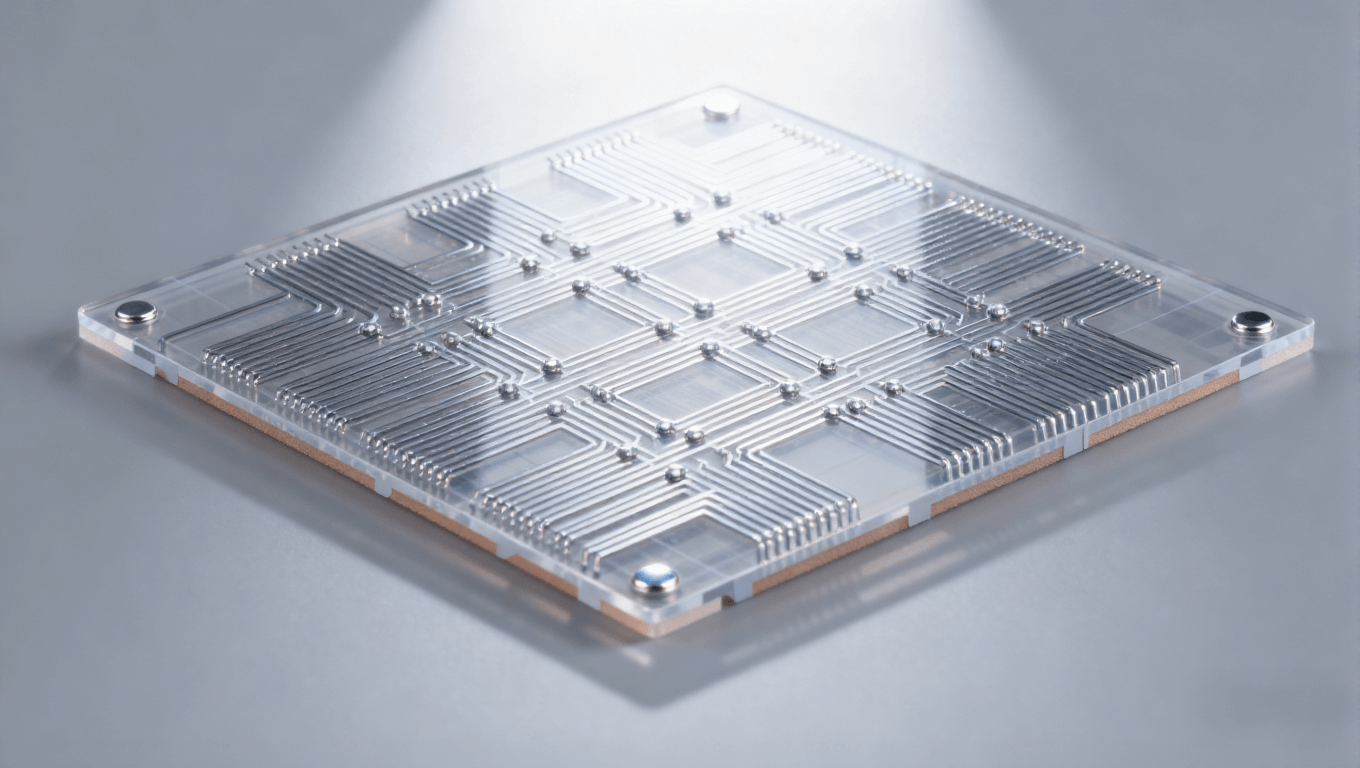

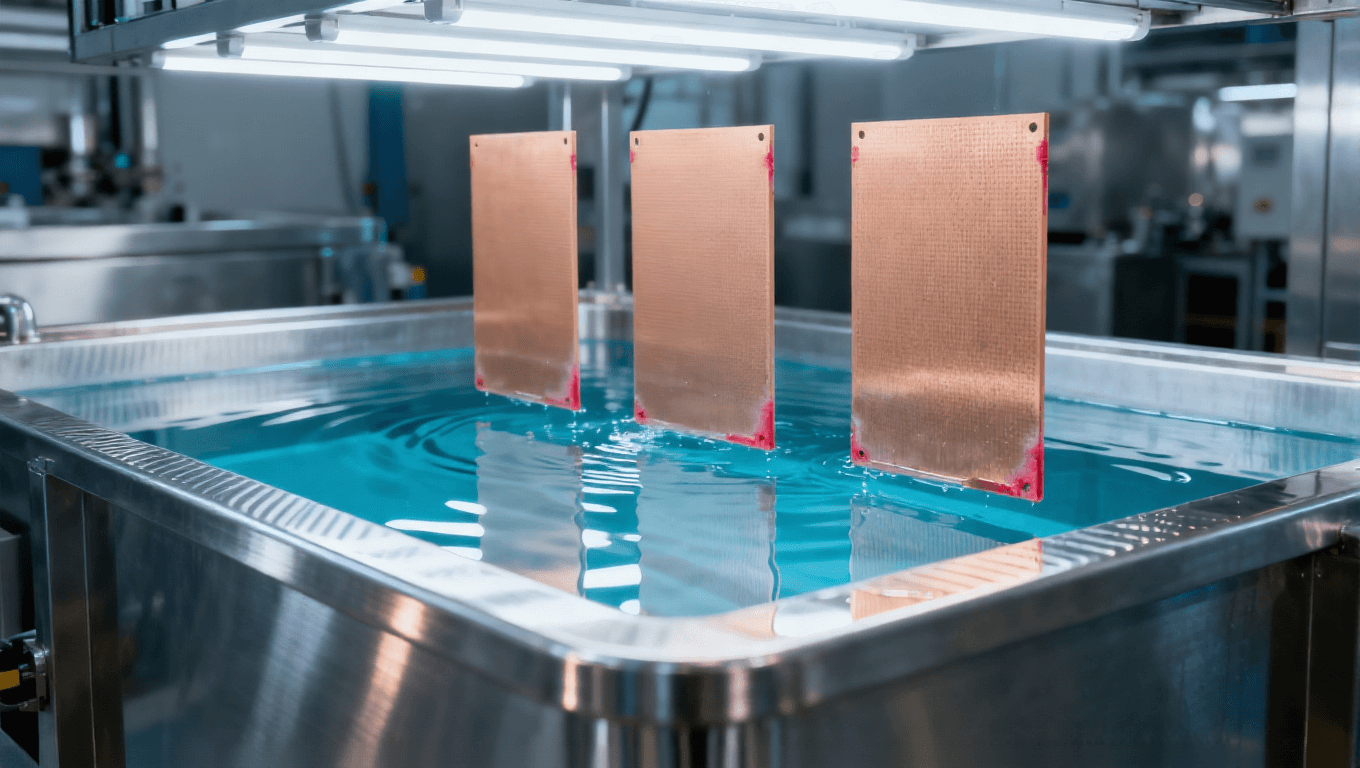

• 步骤 2:化学镀铜(种子层形成)

将预处理后的基板浸入化学镀铜液(主要成分:硫酸铜、甲醛、EDTA),在常温(25-30℃)下反应 15-20 分钟,形成 2-5μm 的均匀薄铜层。这层铜是后续电镀的 “种子”,需保证无针孔、无漏镀。

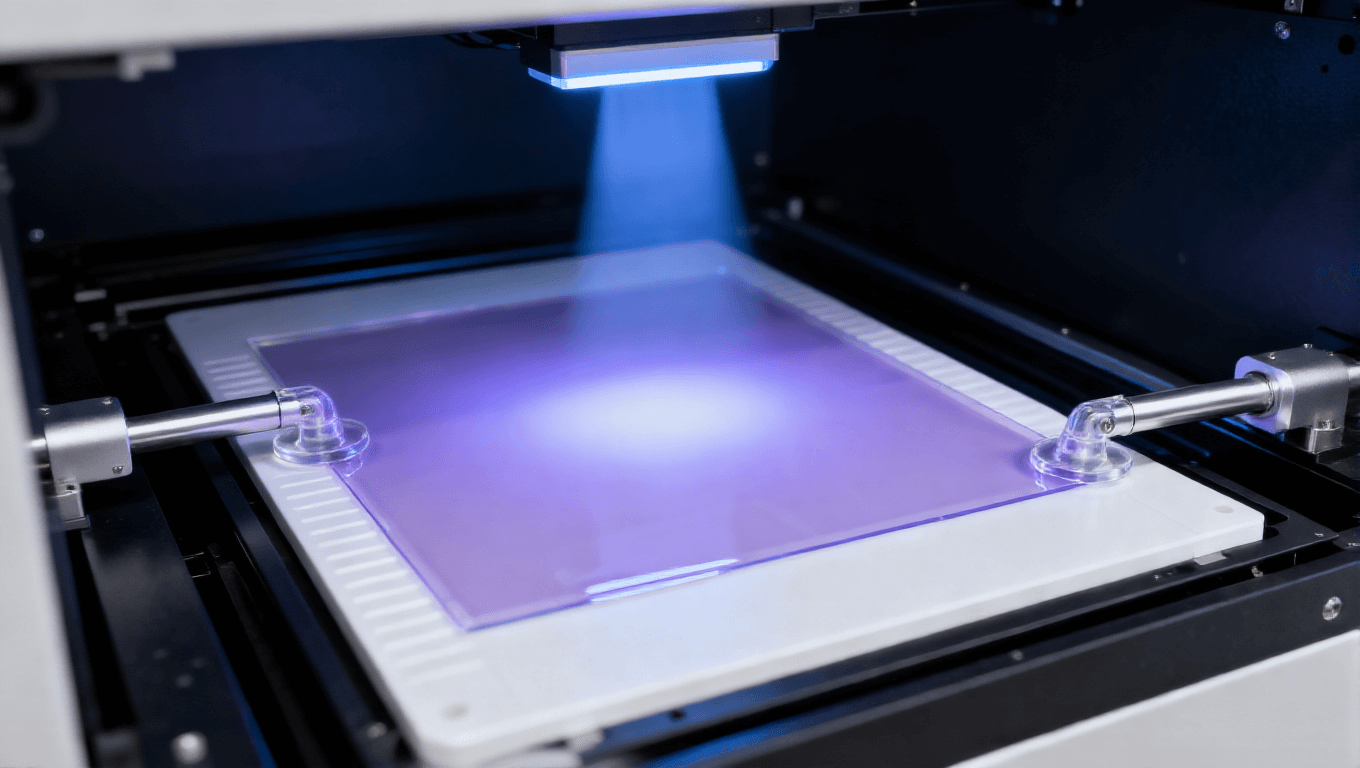

• 步骤 3:光刻胶涂覆与显影

在化学镀铜层表面涂覆感光光刻胶(干膜或湿膜),通过紫外光曝光(曝光能量 80-120mJ/cm²),将线路图案转移至光刻胶层;再用显影液(如碳酸钠溶液)去除未曝光区域的光刻胶,露出需电镀加厚的线路区域。

• 步骤 4:图形电镀(线路加厚)

将显影后的基板放入电镀槽(电镀液含硫酸铜、硫酸),以基板为阴极、纯铜为阳极,通以 1-2A/dm² 的电流密度,电镀 20-30 分钟,使露出的铜层厚度从 2-5μm 加厚至 15-30μm(根据设计需求调整)。

• 步骤 5:光刻胶剥离

用剥离液(如氢氧化钠溶液)去除线路表面残留的光刻胶,此时基板表面形成 “加厚线路 + 未加厚的种子层” 两种结构。

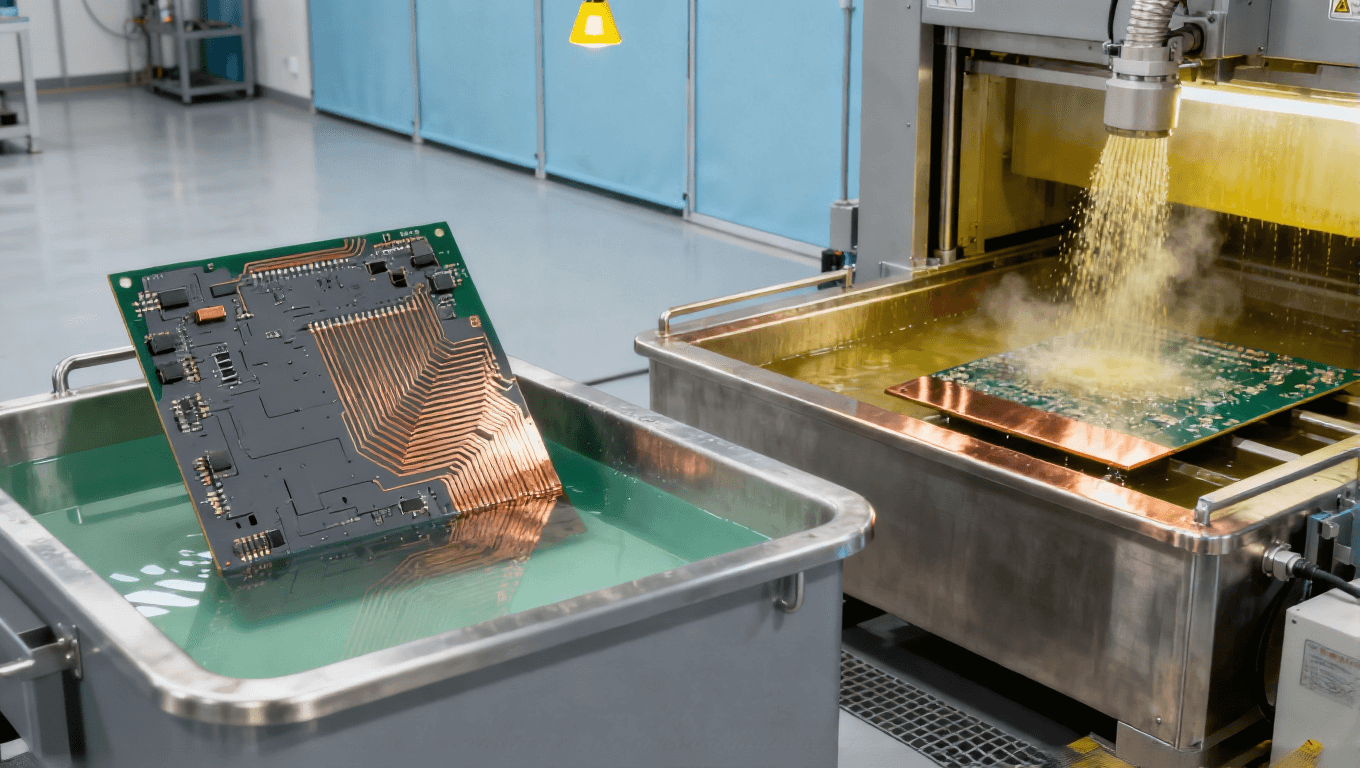

• 步骤 6:闪蚀(去除多余种子层)

采用弱蚀刻液(如过硫酸铵溶液)轻微蚀刻(蚀刻时间 30-60 秒),去除未被电镀线路保护的种子层(2-5μm),最终保留完整的加厚线路。此步骤需严格控制蚀刻时间,避免损伤目标线路。

mSAP 在 SAP 基础上进行了 3 处关键改良,以实现更高精度:

• 改良 1:超薄初始铜层制备

采用 “物理气相沉积(PVD)+ 化学镀铜” 复合工艺,先通过 PVD 形成 0.1-0.5μm 的金属薄膜,再叠加化学镀铜至 1-2μm,相比 SAP 的纯化学镀铜,初始铜层的均匀性提升 40%,为精细线路制造奠定基础。

• 改良 2:差分蚀刻技术

传统 SAP 的闪蚀为 “一次性蚀刻”,而 mSAP 采用 “两次差分蚀刻”:第一次蚀刻去除大部分多余种子层,第二次用低浓度蚀刻液(如盐酸 + 双氧水)精细修正线路边缘,使线路边缘粗糙度(Ra)控制在 1μm 以下,线宽偏差缩小至 ±1μm。

• 改良 3:光刻工艺升级

采用 “深紫外光刻(DUV)” 替代传统紫外光刻,曝光分辨率从 30μm 提升至 10μm,同时搭配高精度显影设备,解决细线路(≤20μm)的显影残留问题。

为凸显半加成法的技术优势,需将其与 PCB 行业传统的 “减成法”“半减成法” 进行对比,明确不同工艺的适用场景。

工艺类型 | 核心逻辑 | 线宽 / 线距能力 | 铜层均匀性 | 材料利用率 | 适用场景 |

减成法 | 基板覆铜→蚀刻去除多余铜 | ≥50μm | 较差(±10%) | 低(50%-60%) | 普通消费电子 PCB、玩具 PCB |

半减成法 | 薄铜基板→电镀加厚→蚀刻 | 30-50μm | 一般(±8%) | 中(70%-80%) | 中端 HDI 板、路由器 PCB |

半加成法(SAP) | 无铜基板→化学镀 + 电镀 | 30-40μm | 良好(±5%) | 高(90%-95%) | 高端 HDI 板、服务器 PCB |

改良半加成法(mSAP) | 超薄种子层→差分蚀刻 | 15-25μm | 优秀(±3%) | 高(95% 以上) | 类载板、5G 模块、汽车高端 PCB |

从对比可见,半加成法(尤其是 mSAP)在 “高精度”“高材料利用率” 上具有绝对优势,但其工艺复杂度和设备投入也更高,因此主要用于高端 PCB 制造;而减成法因成本低、工艺简单,仍适用于中低端产品。

为何半加成法能成为高端 PCB 制造的主流选择?其核心优势可概括为四点:

随着智能手机、可穿戴设备的 “微型化”,PCB 线路从 “毫米级” 向 “微米级” 跨越。mSAP 工艺可实现 15μm 线宽 / 15μm 线距(甚至更细),相比传统减成法(≥50μm),线路密度提升 3 倍以上,能在相同基板面积上集成更多元器件,满足设备小型化需求。

半加成法的铜层形成过程为 “化学镀(均匀覆盖)+ 电镀(加厚)”,铜层晶粒更细小、结晶更致密,且无传统减成法 “蚀刻残留” 问题。测试数据显示,mSAP 工艺制造的 PCB 铜层抗拉强度可达 350MPa 以上,耐弯折次数(-40℃~125℃循环)比减成法产品提升 50%,适用于汽车电子、工业控制等对可靠性要求高的场景。

传统减成法对基板表面平整度要求高,难以适配高频基板(如 PTFE)、柔性基板(PI)等特殊材料。而半加成法的 “化学镀铜” 可在非导体表面均匀成膜,即使是表面粗糙度较高的高频基板,也能形成稳定的铜层。这一特性使其在 5G 通信(需高频基板)、柔性电子(需 PI 基板)领域具有不可替代的优势。

传统减成法需蚀刻掉 70% 以上的覆铜,不仅浪费铜资源,还产生大量蚀刻废液(含重金属离子)。半加成法仅需蚀刻 “种子层”(占总铜量的 10%-20%),铜资源利用率提升至 90% 以上,蚀刻废液排放量减少 60%,符合国家 “双碳” 政策及 PCB 行业绿色制造趋势。

半加成法(尤其是 mSAP)的技术优势使其在多个高端领域实现规模化应用,以下为四大核心场景:

类载板是 “介于 PCB 与 IC 载板之间的高端产品”,主要用于智能手机主板(如苹果 iPhone、华为 Mate 系列),需承载 CPU、内存等核心芯片。由于芯片引脚间距仅 0.3mm 以下,需线路精度达 20μm 以内,mSAP 工艺成为类载板制造的唯一选择。目前全球类载板市场中,80% 以上的产品采用 mSAP 工艺,预计 2025 年市场规模将突破 50 亿美元。

5G 通信模块(如基站射频单元、终端毫米波模块)需使用高频基板(如 PTFE),且线路密度高(需集成多通道信号线路)。半加成法可在 PTFE 基板表面形成稳定铜层,同时 mSAP 的精细线路能力可减少信号串扰,提升模块通信效率。国内头部通信企业(如华为、中兴)的 5G 基站模块已全面采用 mSAP 工艺。

新能源汽车的车载雷达、自动驾驶控制器等组件,需在 - 40℃~150℃的极端温度下稳定工作,且线路需耐受振动、冲击。半加成法制造的 PCB 铜层附着力强、耐温性好,可满足汽车电子的 “车规级” 可靠性要求。目前特斯拉、比亚迪等车企的高端车型已采用 mSAP 工艺 PCB。

Mini/Micro LED 显示屏的驱动板需为每颗 LED 芯片提供独立线路,线路密度达 “每平方厘米千条以上”,线宽 / 线距需控制在 20μm 以内。mSAP 工艺的精细线路能力可精准匹配这一需求,目前三星、京东方的 Mini LED 显示屏驱动板已采用 mSAP 工艺量产。

在半加成法量产过程中,企业常面临 “附着力不足”“精度偏差” 等问题,以下为三大典型问题及应对方案:

• 问题表现:后续电镀或弯折测试时,铜层出现剥离。

• 核心原因:基板预处理不彻底(表面油污残留、粗化不足);化学镀铜液活性降低。

• 解决方案:

a. 优化预处理流程:增加 “等离子清洗” 环节,去除基板表面有机污染物;将微蚀深度提升至 80-120nm,增强表面粗糙度。

b. 实时监控化学镀铜液:定期检测镀液浓度(硫酸铜浓度控制在 8-12g/L),每 2 小时补充一次还原剂(甲醛),确保镀液活性稳定。

• 问题表现:显影后线路边缘模糊,线宽偏差超过 ±2μm。

• 核心原因:光刻胶涂覆厚度不均;曝光能量不稳定;显影液温度波动。

• 解决方案:

a. 采用 “狭缝涂布” 技术替代传统辊涂,使光刻胶厚度偏差控制在 ±1μm 以内。

b. 安装曝光能量监控仪,实时调整曝光能量(DUV 光刻控制在 100-110mJ/cm²)。

c. 为显影槽加装恒温系统,将显影液温度稳定在 28±0.5℃。

• 问题表现:线路不同区域的铜层厚度差超过 5μm,影响电流传导稳定性。

• 核心原因:电镀槽内电流分布不均;电镀液搅拌不充分。

• 解决方案:

a. 在电镀槽内加装 “辅助阳极”,优化电流分布,使线路边缘与中心的电流密度差缩小至 ±0.2A/dm²。

b. 采用 “空气搅拌 + 喷淋搅拌” 复合方式,提升电镀液流动性,确保铜离子均匀分布。

随着电子技术的持续迭代,半加成法工艺将向 “更精细、更融合、更绿色” 方向发展:

目前 mSAP 的线宽能力为 15-25μm,未来通过 “极紫外光刻(EUV)+ 原子层沉积(ALD)” 技术,可实现 5-10μm 的亚微米级线路,满足 IC 载板(如先进封装用载板)的制造需求,进一步模糊 PCB 与 IC 载板的技术边界。

随着 “系统级封装(SiP)” 的普及,PCB 需与芯片封装更紧密结合。未来半加成法将实现 “PCB - 封装一体化” 制造,即在 PCB 制造过程中直接完成芯片的局部封装,减少封装环节,提升系统集成度。

一方面,将 “无氰化学镀铜” 技术规模化应用,替代传统含氰镀液,减少有毒物质排放;另一方面,开发 “可回收光刻胶”,通过溶剂回收实现光刻胶的循环利用,降低材料成本与环境污染。

PCB 半加成法工艺(SAP/mSAP)是 PCB 行业从 “中低端制造” 向 “高端智造” 升级的核心技术支撑。其高精度、高可靠性的特性,不仅满足了消费电子、5G、汽车电子等领域的高端需求,更推动了 PCB 行业的技术迭代与产业升级。