在半导体行业不断追求 “更小、更快、更节能” 的发展历程中,传统二维平面封装技术逐渐面临物理极限的挑战。当芯片制程逼近原子尺度,单纯依靠缩小晶体管尺寸来提升性能的难度与成本呈指数级增长,而三维堆叠封装设计的出现,为这一困境提供了关键解决方案。

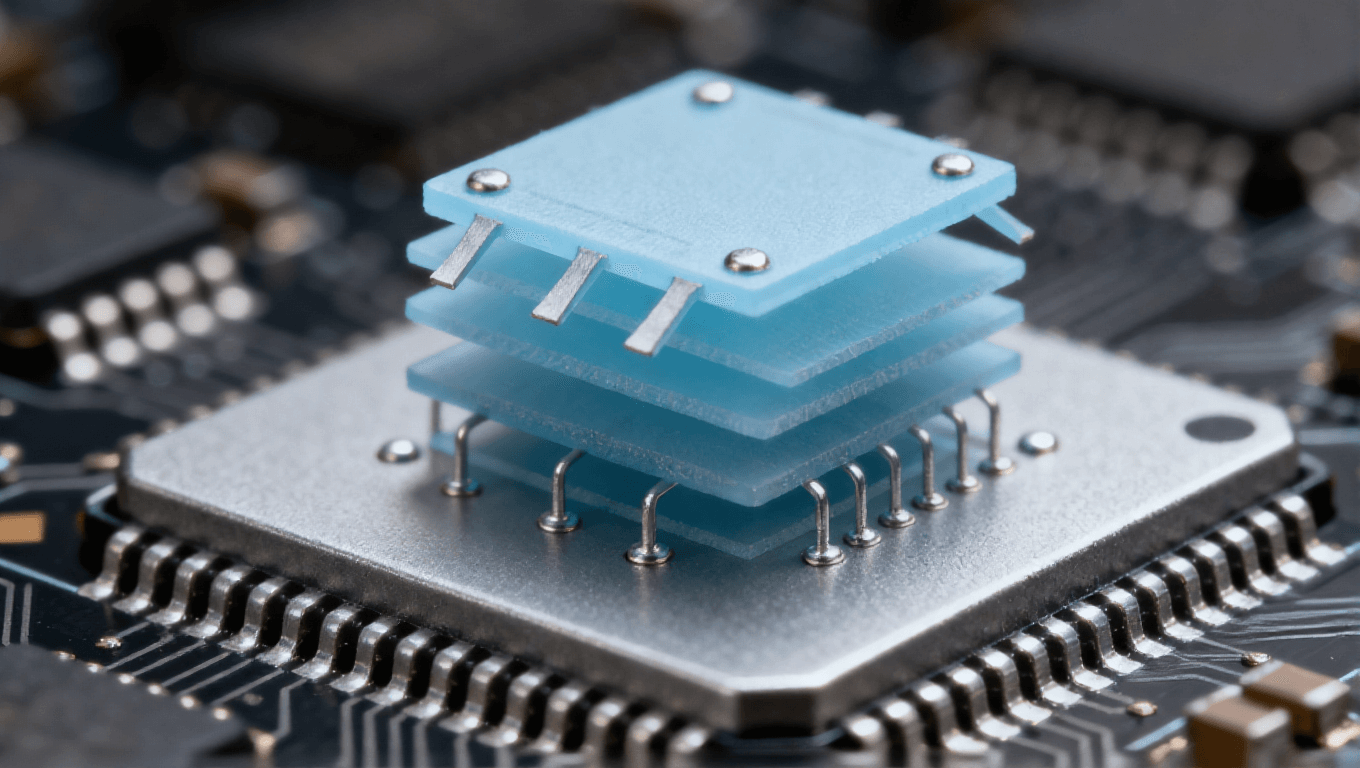

三维堆叠封装设计(3D Stacked IC Packaging)是指通过垂直方向上的堆叠集成,将多颗芯片、芯片与无源器件或不同功能的晶圆紧密结合,形成一个高度集成的系统级封装(SiP)结构。与传统二维封装相比,其核心价值体现在三个维度:一是空间利用率的飞跃,垂直堆叠使封装面积减少 40%-60%,尤其适配智能手机、可穿戴设备等小型化终端;二是互连效率的提升,芯片间垂直互连距离缩短至微米级,信号传输延迟降低 30% 以上,同时功耗减少 20%-35%;三是功能集成的灵活性,可实现逻辑芯片、存储芯片、射频芯片等异质器件的一体化集成,快速满足复杂系统需求。

从行业发展来看,三维堆叠封装设计已从概念验证阶段进入规模化应用阶段。根据 SEMI 数据,2024 年全球三维堆叠封装市场规模突破 80 亿美元,预计 2028 年将达到 180 亿美元,年复合增长率超 20%。这一增长背后,是消费电子、汽车电子、人工智能等领域对高性能、高密度封装的迫切需求,也印证了三维堆叠封装设计成为半导体产业链核心竞争力的事实。

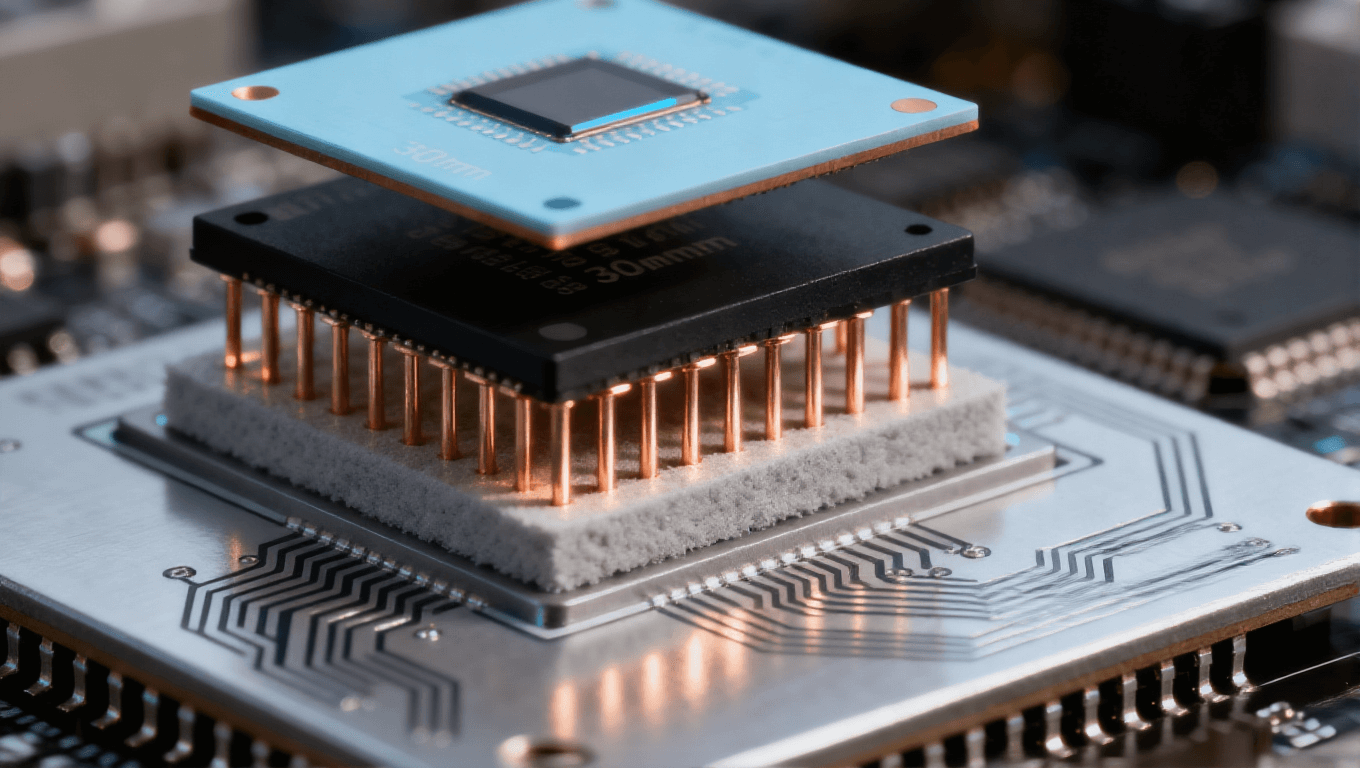

三维堆叠封装设计并非单一技术,而是由多个核心技术模块协同构成的复杂体系。其中,硅通孔(TSV)技术、微凸点(Micro Bump)技术与晶圆键合(Wafer Bonding)技术共同构成了垂直互连的基础,也是决定封装性能的关键环节。

硅通孔技术是三维堆叠封装的核心支撑,其原理是在硅晶圆上钻出直径为 5-50 微米的微小通孔,通过金属化处理(通常为铜电镀)形成垂直导电通道,实现上下晶圆或芯片的电气连接。相较于传统的引线键合(Wire Bonding),TSV 技术的优势在于:

1. 互连距离极短,仅为传统引线键合的 1/100-1/10,大幅降低信号衰减与传输延迟;

2. 可实现高密度互连,每平方毫米可容纳数百个通孔,满足多芯片集成的信号需求;

3. 支持 “面对面”“背靠背” 等多种堆叠方式,灵活适配不同器件组合。

TSV 技术的工艺流程主要包括四个步骤:首先是 “通孔刻蚀”,通过深反应离子刻蚀(DRIE)在硅晶圆上形成高深宽比(通常为 10:1-30:1)的通孔;其次是 “绝缘层沉积”,在通孔内壁覆盖二氧化硅(SiO₂)或氮化硅(Si₃N₄),防止电流泄漏;然后是 “种子层制备”,采用物理气相沉积(PVD)工艺沉积钛 / 铜种子层,为后续金属化做准备;最后是 “铜电镀填充”,通过电化学沉积将铜填满通孔,形成导电通道。

若说 TSV 是垂直互连的 “桥梁”,微凸点则是连接不同芯片的 “精密接口”。在三维堆叠封装中,当芯片或晶圆需要面对面堆叠时,微凸点负责实现上下芯片的直接电气连接,其尺寸通常在 20-50 微米,间距(Pitch)可缩小至 40 微米以下,远小于传统焊球(C4 Bump)的尺寸(100 微米以上)。

微凸点技术的核心挑战在于 “高精度” 与 “高可靠性”。从工艺角度看,其制备流程包括:

1. 凸点下金属化(UBM):在芯片焊盘上沉积铬 / 铜 / 金或钛 / 镍 / 金多层金属,增强焊盘与凸点的结合力,防止金属扩散;

2. 凸点成型:采用电镀工艺制备锡银(SnAg)、铜(Cu)或金(Au)凸点,确保凸点高度均匀、形貌一致;

3. 回流焊接:通过加热使凸点融化,与对接芯片的焊盘形成可靠的金属间化合物(IMC),实现电气与机械连接。

为应对微凸点的可靠性问题,行业通常采用 “-underfill(底部填充)” 工艺,在凸点间隙注入环氧树脂,吸收热应力与机械应力,避免凸点在温度循环或振动环境下断裂。

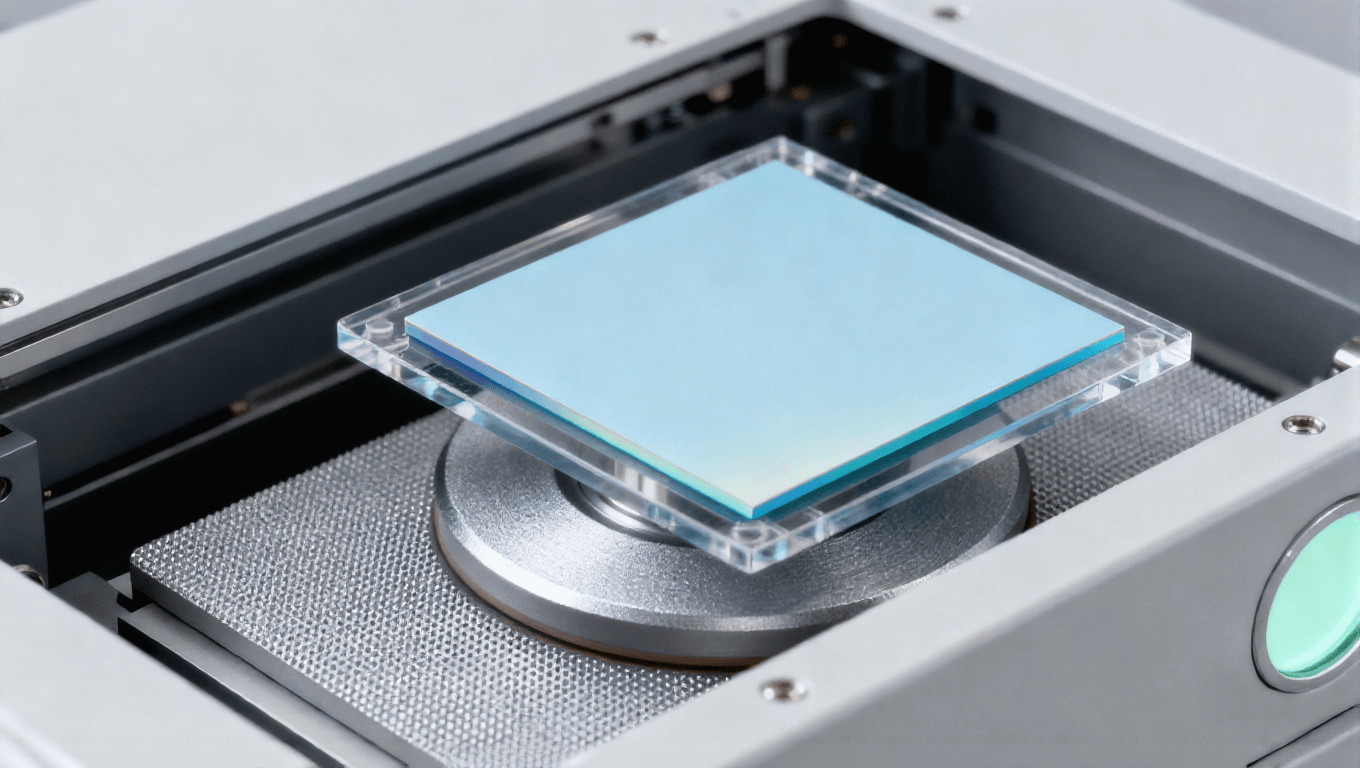

晶圆键合技术是将两片或多片晶圆在特定条件下(温度、压力、真空)紧密结合的工艺,确保三维堆叠结构的机械稳定性与封装气密性。根据键合材料的不同,主流技术可分为 “直接键合” 与 “中介层键合” 两类:

• 直接键合:无需额外粘合剂,通过晶圆表面的原子间作用力(如范德华力、共价键)实现结合,典型代表是 “硅 - 硅直接键合(SDB)” 与 “氧化硅 - 氧化硅键合(SiO₂-SiO₂)”。该技术的优势是键合强度高、界面电阻低,适用于对性能要求苛刻的场景(如图像传感器、射频器件);

• 中介层键合:通过聚合物(如聚酰亚胺、苯并环丁烯)或金属层实现晶圆连接,工艺温度低(通常低于 300℃),兼容性强,适合异质晶圆(如硅晶圆与化合物半导体晶圆)的堆叠。

无论采用哪种键合方式,“对准精度” 都是核心指标。目前行业主流的对准设备可实现 ±0.5 微米的对准误差,而随着堆叠层数增加(如 4 层以上堆叠),对准误差的累积会直接影响互连可靠性,因此 “分步对准” 与 “误差补偿算法” 成为高端三维堆叠封装设计的关键技术难点。

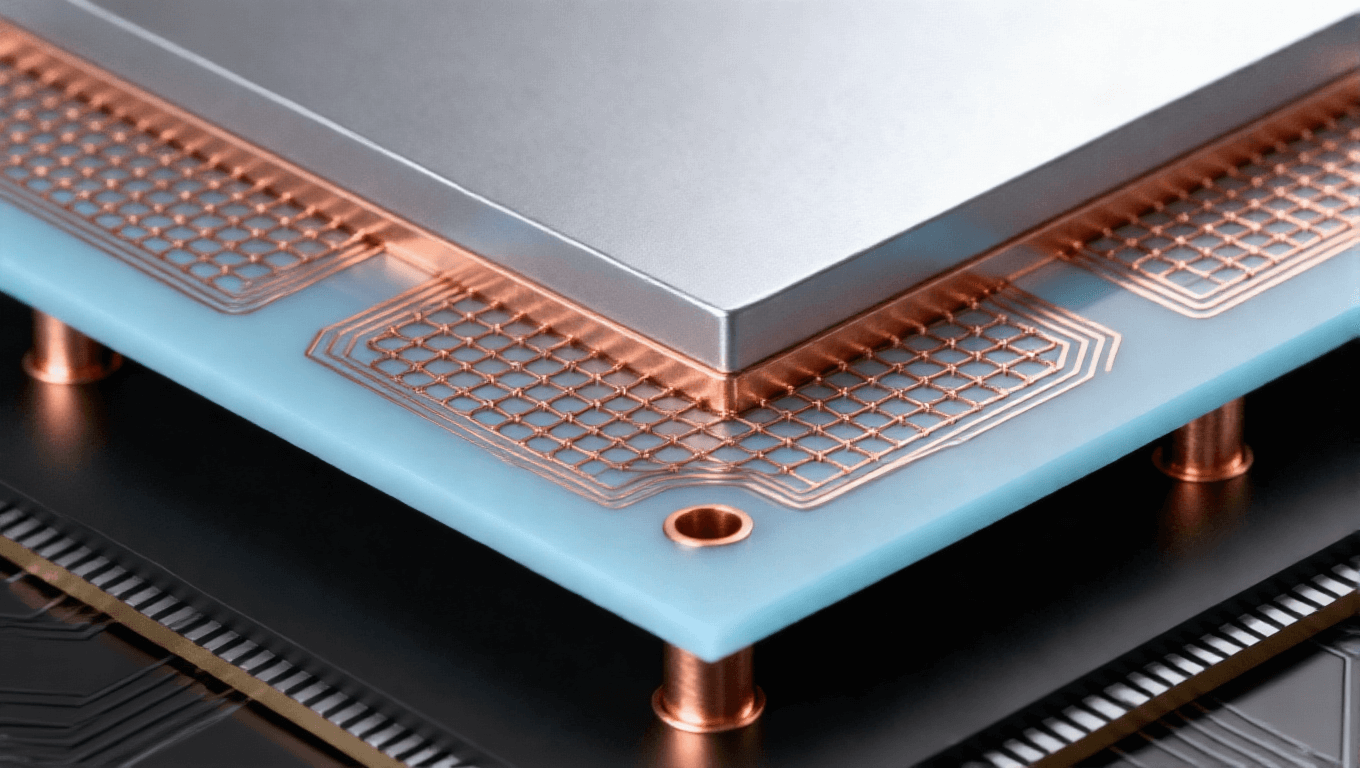

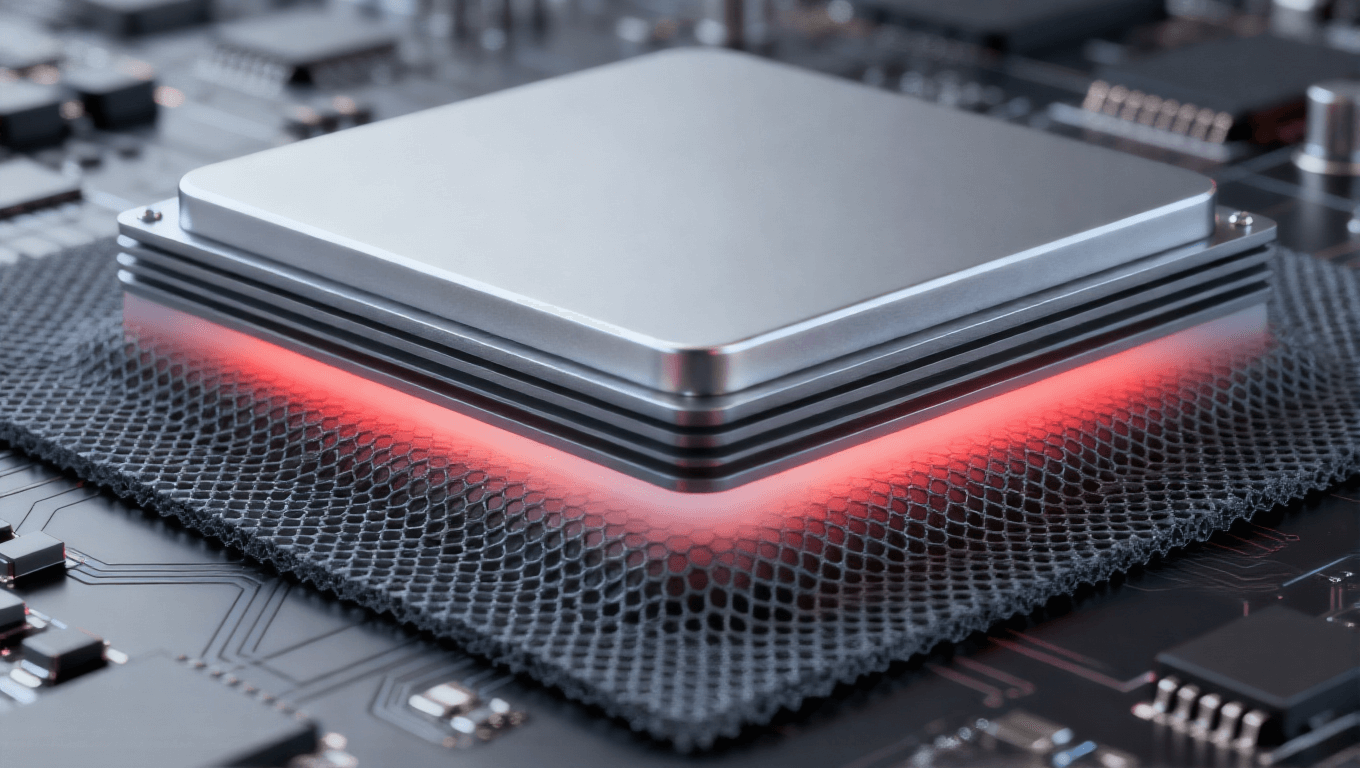

尽管三维堆叠封装设计优势显著,但在实际量产过程中,仍面临热管理、对准精度、可靠性测试三大核心工艺难点。这些难点不仅影响产品良率,更直接决定了技术的应用范围,因此行业内已形成一系列针对性的解决方案。

三维堆叠封装将多颗芯片垂直堆叠,使单位体积内的功率密度大幅提升(部分高端产品功率密度可达 50W/cm³ 以上),而芯片(尤其是逻辑芯片、AI 芯片)在工作时会产生大量热量。若热量无法及时散出,芯片温度会快速升高,导致性能下降(如 CPU 频率降频)、寿命缩短,甚至出现烧毁风险。

热管理难点的核心原因有两个:一是垂直堆叠结构使热量难以通过传统的 “底部散热” 方式导出,热量在堆叠层间积聚;二是异质集成场景下(如逻辑芯片与存储芯片堆叠),不同芯片的热膨胀系数(CTE)差异较大,温度变化会导致层间产生热应力,进一步加剧可靠性问题。

针对这一难点,行业已形成 “主动散热 + 被动散热” 结合的解决方案:

1. 被动散热优化:在堆叠结构中嵌入 “热界面材料(TIM)”,如石墨烯、纳米银浆,提升层间热传导效率;同时采用 “散热顶盖(Heat Spreader)” 设计,将堆叠芯片的热量传导至外部散热系统;

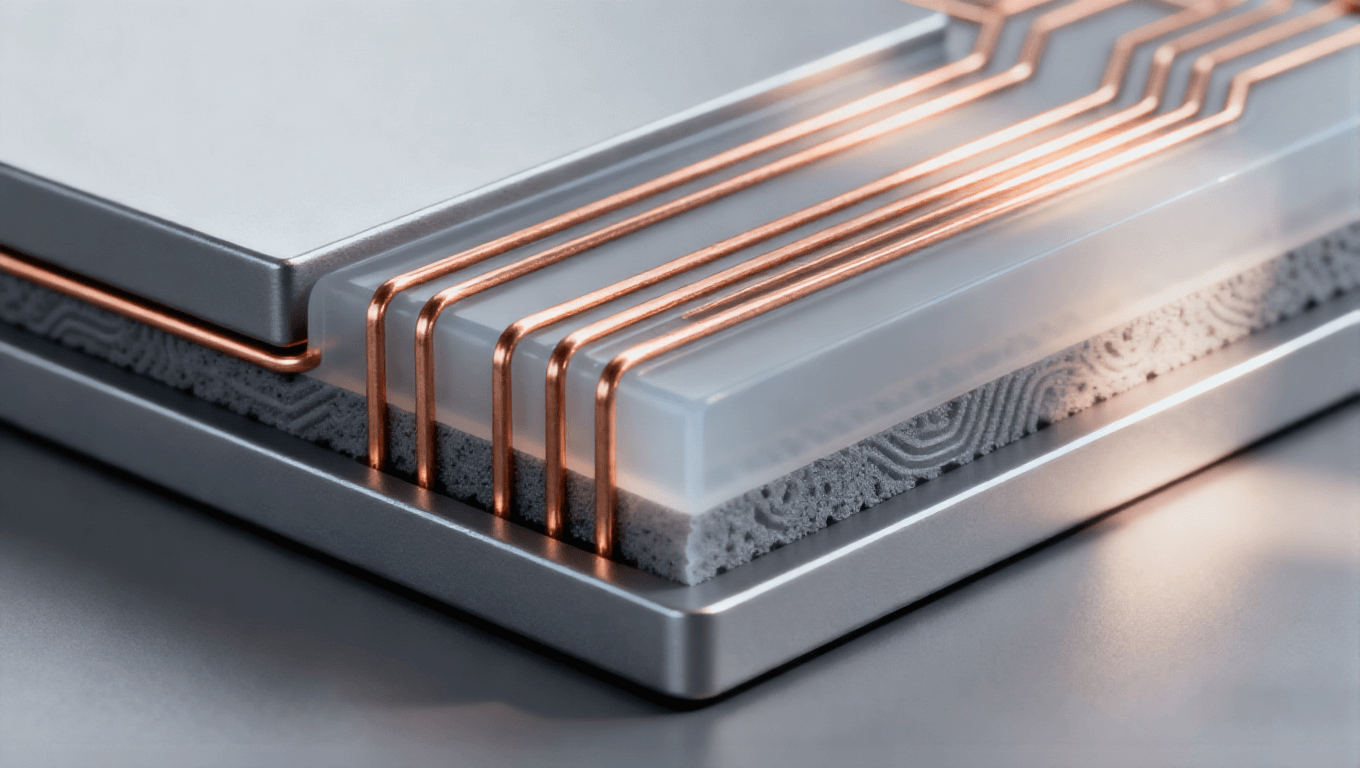

2. 主动散热创新:对于高功率场景(如 AI 服务器芯片),引入 “微流道散热” 技术,在晶圆或封装内设计微小流道,通过冷却液循环带走热量;部分厂商还尝试将 “热电冷却器(TEC)” 集成到封装中,通过半导体温差效应主动降温;

3. 设计层面优化:采用 “非对称堆叠” 布局,将高发热芯片(如逻辑芯片)放置在靠近散热端的位置,低发热芯片(如存储芯片)放置在内部,减少热量传递路径;同时通过芯片分区供电、动态功耗管理,降低局部热点温度。

在三维堆叠封装设计中,每增加一层堆叠,就需要一次晶圆或芯片的对准与键合。由于设备精度、材料变形等因素,每次对准都会产生微小误差(通常为 ±0.1-±1 微米),而误差的累积会导致上下层的 TSV 或微凸点无法精准对接,进而出现开路、短路等问题,严重影响良率。

对准精度难点的典型场景是 “3 层以上逻辑芯片堆叠” 与 “异质晶圆堆叠”。前者由于堆叠层数多,误差累积效应明显;后者由于不同晶圆的材料特性差异(如硅与碳化硅的硬度、热膨胀系数不同),在键合过程中易发生变形,导致对准偏差。

为解决这一问题,行业主要从 “设备升级” 与 “工艺优化” 两个方向突破:

1. 高精度对准设备:采用 “双 - sided alignment(双面对准)” 技术,通过晶圆上下两侧的摄像头同时捕捉对准标记,实时调整晶圆位置,将单次对准误差控制在 ±0.3 微米以内;部分高端设备还引入 “激光干涉测量” 模块,进一步提升对准精度;

2. 误差补偿算法:在封装设计阶段,通过有限元分析(FEA)模拟键合过程中的材料变形,提前预留补偿量;在量产阶段,通过机器视觉系统实时检测对准误差,动态调整键合参数(如压力、温度),抵消误差累积;

3. 中间层(Interposer)技术:引入硅或玻璃中间层,先将芯片与中间层对准键合,再通过中间层实现多层堆叠。中间层可作为 “缓冲层”,减少直接堆叠的对准难度,同时提升互连可靠性。

三维堆叠封装结构复杂,包含大量垂直互连通道与异质器件,其可靠性测试面临两大挑战:一是 “故障定位难”,传统的探针测试无法覆盖内部堆叠层,难以精准定位开路、短路等故障;二是 “测试场景多”,需要模拟高温、低温、湿度、振动等多种环境,验证长期可靠性,测试周期长、成本高。

针对这些挑战,行业已开发出一系列专用测试技术:

1. 非破坏性测试(NDT)技术:采用 “超声扫描显微镜(SAM)” 检测层间键合质量,通过超声波反射信号判断是否存在空洞、分层等缺陷;利用 “X 射线断层扫描(X-CT)” 实现三维结构成像,直观观察内部互连情况;

2. 电学测试技术:开发 “晶圆级测试(Wafer-Level Test)” 方案,在堆叠前对每颗晶圆进行全面测试,筛选出不良品,减少后续封装成本;引入 “边界扫描测试(BST)”,通过芯片内置的测试电路,实现对内部互连通道的电学性能检测;

3. 可靠性验证标准:遵循 JEDEC(联合电子设备工程委员会)制定的可靠性测试标准,如温度循环测试(TC)、高温高湿偏压测试(HBM)、机械冲击测试(MS)等,确保产品在不同应用场景下的长期稳定性。

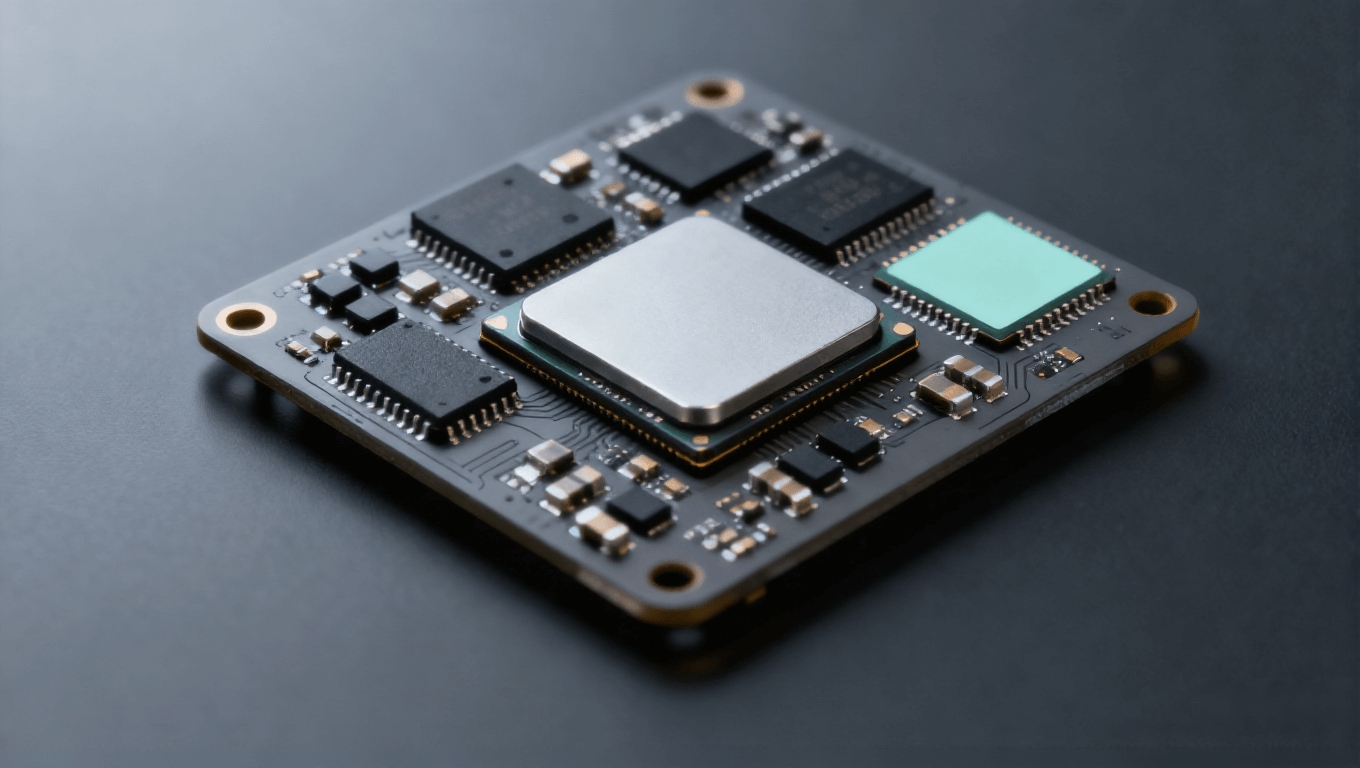

随着技术的成熟,三维堆叠封装设计已在消费电子、汽车电子、人工智能与数据中心三大领域实现规模化应用,成为推动这些领域产品创新的核心技术之一。以下结合具体行业案例,分析其应用特点与价值。

消费电子(如智能手机、平板电脑、可穿戴设备)对产品尺寸与性能的要求极为苛刻,三维堆叠封装设计恰好满足这一需求。以智能手机为例,其核心芯片(如 AP 应用处理器、图像传感器)采用三维堆叠封装后,可在缩小封装面积的同时,提升数据传输速度与存储容量。

典型案例 1:苹果 A 系列芯片的 3D 堆叠封装

苹果自 A15 芯片开始,采用 “逻辑芯片 + 内存芯片” 的 3D 堆叠封装设计(称为 “3D IC”),将 A15 的 CPU/GPU 核心与 LPDDR5 内存垂直堆叠,封装面积较传统二维封装减少约 30%,同时内存带宽提升 50% 以上。这一设计使 iPhone 13 系列在有限的机身空间内,实现了性能与续航的双重提升。

典型案例 2:三星图像传感器的 3D 堆叠

三星的 ISOCELL JN1 图像传感器采用 “像素层 + 逻辑层” 的 3D 堆叠设计,将负责信号处理的逻辑电路转移到像素层下方,使传感器尺寸缩小至 1/4 英寸(约 6.35 毫米),同时像素尺寸保持在 0.64 微米,兼顾了小型化与高画质。该传感器已广泛应用于中高端智能手机的前置摄像头与后置副摄像头。

在消费电子领域,三维堆叠封装设计的未来趋势是 “多芯片异构集成”,例如将 AP、射频芯片、电源管理芯片(PMIC)、传感器等集成到一个封装中,形成 “系统级封装(SiP)”,进一步提升终端产品的集成度与性价比。

汽车电子(如自动驾驶芯片、车规级 MCU、车载雷达)对封装的可靠性与安全性要求远高于消费电子,需满足 - 40℃-150℃的宽温度范围、10 年以上的使用寿命,以及抗振动、抗电磁干扰等严苛条件。三维堆叠封装设计通过优化互连结构与材料选择,可满足这些 “刚性要求”。

典型案例 1:特斯拉自动驾驶芯片(HW4.0)

特斯拉 HW4.0 自动驾驶芯片采用 “2 颗 GPU 核心 + 1 颗 CPU 核心 + 多颗神经网络加速器” 的 3D 堆叠封装设计,通过 TSV 技术实现核心间的高速互连,数据处理能力达到 200TOPS(每秒万亿次操作)。为满足车规可靠性要求,该封装采用 “陶瓷基板” 替代传统的有机基板,提升热稳定性与抗振动能力;同时引入 “冗余互连” 设计,即使部分 TSV 出现故障,仍可通过备用通道实现信号传输,保障自动驾驶功能安全。

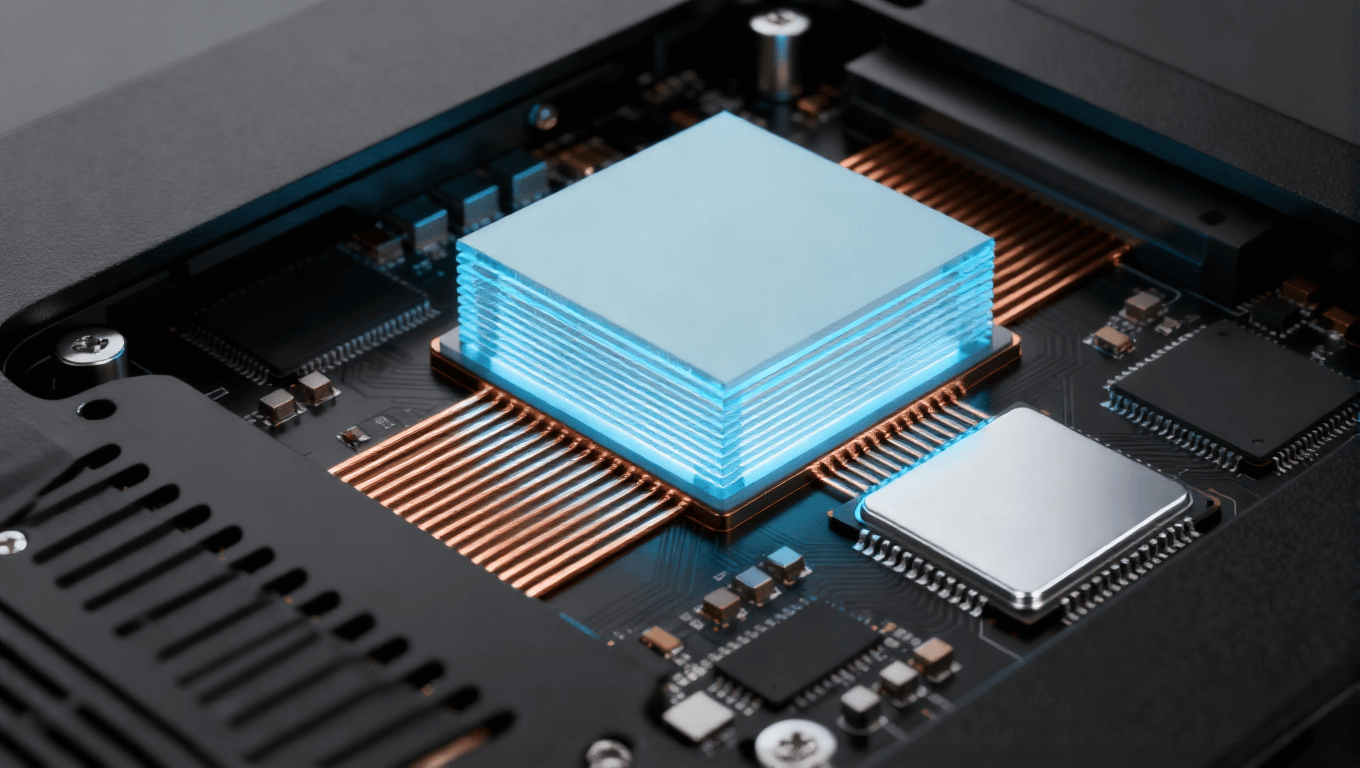

人工智能(AI)训练与数据中心场景对芯片的算力需求呈指数级增长,而传统二维封装的芯片由于互连延迟高、功耗大,难以满足需求。三维堆叠封装设计通过 “内存与逻辑芯片的紧密集成”,大幅提升内存带宽、降低功耗,成为 AI 芯片的核心封装方案。

典型案例 1:英伟达 H100 GPU 的 3D V-Cache 技术

英伟达 H100 GPU 采用 “3D 堆叠缓存(V-Cache)” 设计,将 24GB 的 SRAM 缓存通过微凸点技术垂直堆叠在 GPU 核心上方,使缓存容量较上一代产品提升 3 倍,内存带宽达到 3.3TB/s。这一设计使 H100 在 AI 训练任务(如大语言模型训练)中的算力提升 40% 以上,同时功耗降低 15%,有效缓解了 “内存墙” 问题(即内存速度跟不上 CPU/GPU 算力的瓶颈)。

典型案例 2:英特尔至强处理器的 3D 堆叠封装

英特尔第 4 代至强处理器(Sapphire Rapids)采用 “逻辑芯片 + 高带宽内存(HBM)” 的 3D 堆叠封装,将 8 颗 HBM2e 内存芯片垂直堆叠在处理器核心旁边,通过 TSV 技术实现高速互连,内存带宽达到 1TB/s 以上。该设计使至强处理器在数据中心的虚拟化、云计算任务中,能够更高效地处理大规模数据,提升服务器的整体性能。

在 AI 与数据中心领域,三维堆叠封装设计的未来方向是 “多层堆叠与异质集成”,例如将 GPU、CPU、HBM 内存、AI 加速器集成到一个 “3D 芯片系统” 中,进一步突破算力与功耗的极限。

随着半导体行业对高性能、高密度、低功耗封装的需求持续增长,三维堆叠封装设计将在技术、应用、成本三个维度呈现明确的发展趋势,这些趋势不仅将推动技术本身的成熟,还将重塑半导体产业链的竞争格局。

未来,三维堆叠封装设计将与 7nm 以下先进制程深度融合,形成 “先进制程 + 先进封装” 的协同创新模式。一方面,先进制程的芯片尺寸更小、性能更强,为三维堆叠提供了更优的 “积木”;另一方面,三维堆叠封装可弥补先进制程的成本劣势,通过 “小芯片(Chiplet)+3D 堆叠” 的组合,实现 “用成熟制程封装替代先进制程单片” 的效果,降低成本。

同时,堆叠层数将从目前的 2-4 层向 8 层以上甚至 16 层突破。例如,台积电已宣布开发 “3D Fabric” 技术,支持 8 层以上的晶圆堆叠;三星则在研发 “3D IC Stacking” 技术,计划实现 16 层存储芯片的垂直堆叠。多层堆叠将进一步提升集成度,但也对热管理、对准精度、可靠性测试提出更高要求,推动相关配套技术的创新。

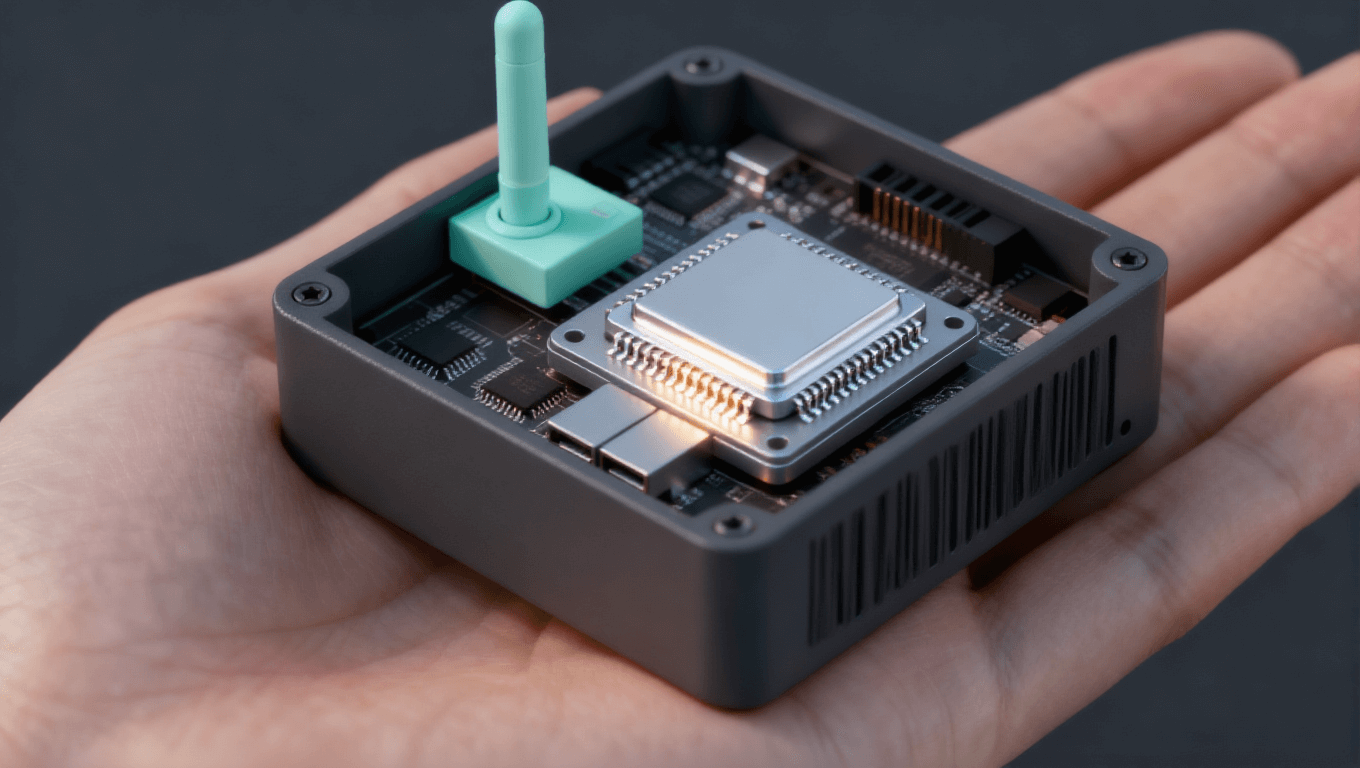

目前,三维堆叠封装设计主要应用于高端产品(如旗舰手机芯片、AI 服务器芯片、车规级高端 MCU),但随着技术成熟与成本下降,其应用将逐步向中低端领域渗透。例如:

• 在消费电子领域,千元机的处理器将逐步采用 “2 层堆叠封装”,实现性能提升的同时控制成本;

• 在工业电子领域,工业 MCU、传感器将采用三维堆叠封装,满足小型化、低功耗的需求;

• 在物联网(IoT)领域,可穿戴设备、智能传感器将通过 “3D 堆叠 + SiP” 的方式,实现多功能集成与超低功耗。

应用领域的拓展将进一步扩大三维堆叠封装的市场规模,同时推动技术向 “定制化” 方向发展 —— 针对不同领域的需求,开发专用的堆叠方案(如工业领域的高可靠性方案、IoT 领域的低功耗方案)。

三维堆叠封装设计作为突破半导体性能瓶颈的核心技术,通过垂直堆叠集成实现了空间利用率、互连效率与功能集成的三重突破,已成为消费电子、汽车电子、AI 与数据中心领域的关键支撑技术。尽管其面临热管理、对准精度、可靠性测试等工艺难点,但行业已形成成熟的解决方案,推动技术从高端领域向中低端领域渗透。

从行业发展来看,三维堆叠封装设计不仅是一种封装技术,更是半导体产业链 “从单一芯片竞争转向系统级集成竞争” 的标志。未来,随着技术与先进制程的深度融合、应用领域的持续拓展、成本的逐步下降,三维堆叠封装设计将成为半导体行业创新的核心驱动力,为终端产品的性能升级与功能创新提供无限可能。