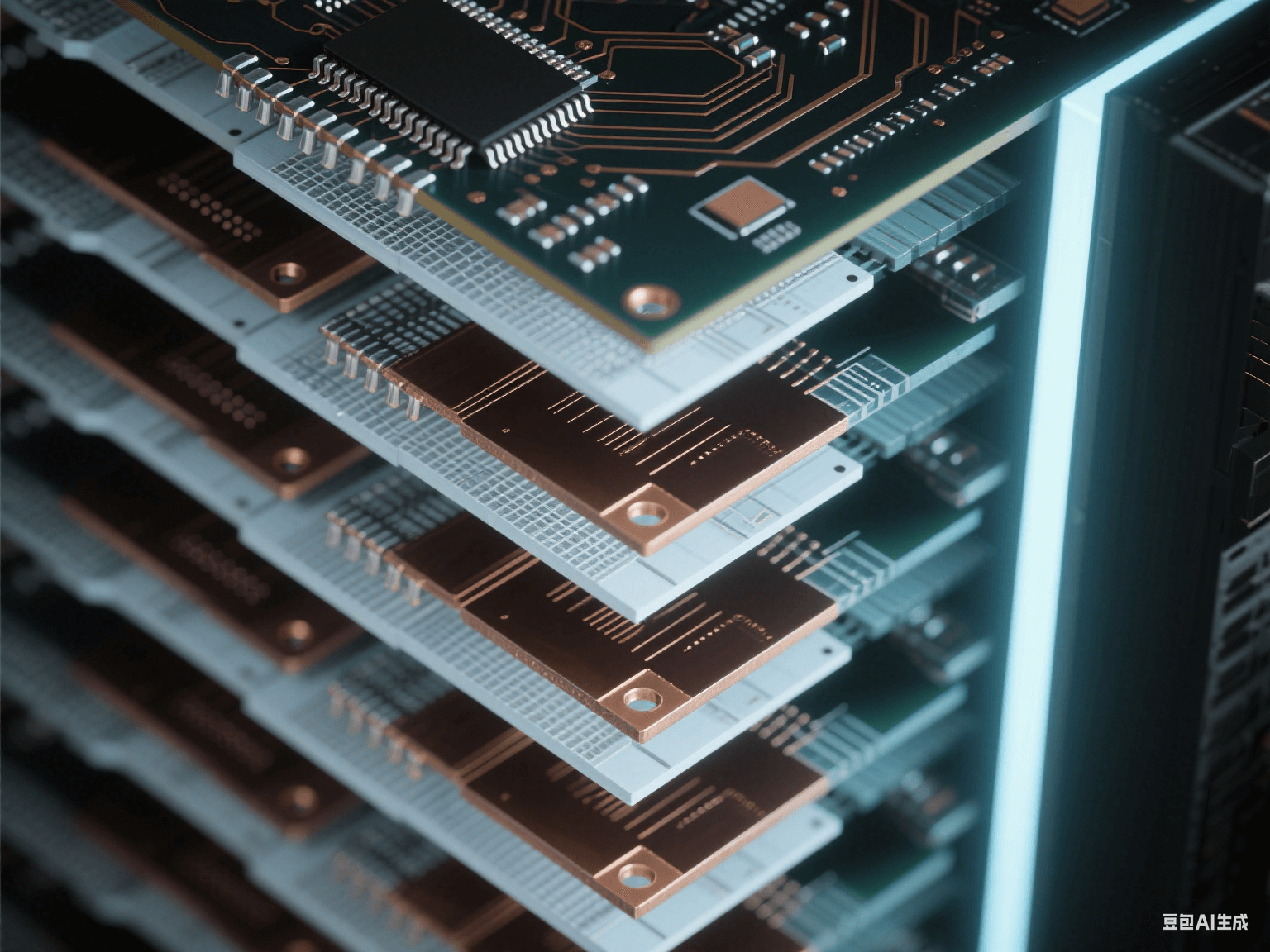

在高速、高密度电子设备的设计与制造中,PCB 叠层结构优化是决定其电气性能、信号完整性、电源完整性、热管理能力乃至最终可靠性的关键环节。它远非简单的层压板堆叠,而是涉及材料科学、电磁场理论、热力学和精密制造工艺的复杂系统工程。通过精心规划铜箔层、介质层的排列顺序、厚度选择以及材料属性匹配,工程师能够有效控制阻抗、降低串扰、管理热量并优化电磁兼容性(EMC),为现代电子产品奠定坚实的物理基础。

在 GHz 级高速电路设计中,PCB 叠层结构优化的首要目标是保障信号完整性 (SI)。信号传输路径的特性阻抗(如常见的 50 欧姆或 100 欧姆差分)必须严格匹配。叠层设计通过精确计算和选择不同层的介质材料厚度 (Dk 值) 与铜箔厚度,结合特定的走线宽度 / 间距,实现精准的阻抗控制。优化的叠层能显著减少信号在传输线中的反射损耗,确保信号波形纯净,数据高速稳定传输。这对于服务器、高端路由器、5G 基站等设备至关重要。不合理的设计会导致信号畸变、误码率飙升,甚至系统功能失效。

电源分配网络 (PDN) 的稳定性是系统可靠运行的保障。优化的叠层结构通过精心设计电源层 (Power Plane) 与地层 (Ground Plane) 的邻近配对(如相邻层或紧密耦合层),形成低阻抗、低电感的去耦电容回路。这种设计能有效抑制电源噪声,为芯片提供瞬时大电流需求,防止因电压跌落造成的逻辑错误或重启。特别是对于处理器、FPGA、高速存储器等功耗大、开关速度快的器件,合理设置多个接地层和电源层,并优化其相对位置和间距,是维持系统低噪声运行的核心策略。

随着电子设备功率密度的持续攀升,热管理成为严峻挑战。PCB 叠层结构优化在散热路径设计中扮演重要角色。通过策略性地增加内部大铜面(用于电源 / 地)的面积和厚度,利用导热系数较高的基板材料(如金属基板、高导热 FR4 或专用散热材料),以及在关键发热元件下方布置导热通孔阵列等手段,可以显著提升 PCB 将热量从芯片传递到散热器或外壳的效率。优化铜层分布还能平衡整个板面的热分布,避免局部过热热点,提升长期可靠性。这在汽车电子、大功率 LED 照明、工业控制设备中尤为关键。

电子设备必须满足严格的电磁辐射 (EMI) 和抗干扰 (EMS) 标准。优化的叠层结构是控制 EMC 的有效手段。连续、完整的接地层为高频噪声电流提供低阻抗回流路径,将电磁场约束在板内,减少向空间辐射的能量。电源 - 地平面形成的平板电容也能吸收和滤除高频噪声。合理的叠层安排还能最小化信号层与电源 / 地层之间的环路面积,降低差模辐射。通过模拟仿真和实际测试验证叠层对 EMC 性能的影响,是设计流程中不可或缺的环节。

PCB 叠层结构优化必须兼顾性能和成本效益。增加层数通常能带来性能提升(如更好的隔离、更低的噪声),但也意味着更高的原材料成本和更复杂的加工工艺(如对位精度要求、压合次数增加)。工程师需要精确评估性能需求,选择性价比最优的层数方案。同时,优化还需考虑工厂的工艺能力(如最小线宽 / 线距、最小孔径、层间对准精度)和材料的可获得性。选择通用性强、供应稳定的材料组合,并设计符合标准制造公差的结构,能有效提高良率、缩短交期、降低成本。在消费电子等价格敏感领域,这种平衡尤为重要。

在毫米波、射频微波领域,PCB 叠层结构优化面临更苛刻的要求。介质材料的介电常数 (Dk) 和损耗角正切 (Df) 的稳定性、一致性成为首要关注点。低 Df 材料(如罗杰斯系列、泰康尼克系列)被广泛采用以降低传输损耗。叠层设计需严格保证传输线结构的均匀性,避免因层压不均匀导致的阻抗突变。微带线、带状线、接地共面波导 (GCPW) 等不同传输线结构对参考地平面的位置和完整性要求各异,需在叠层中精确实现。此外,高频下趋肤效应显著,铜箔的表面粗糙度也成为影响插入损耗的关键因素。

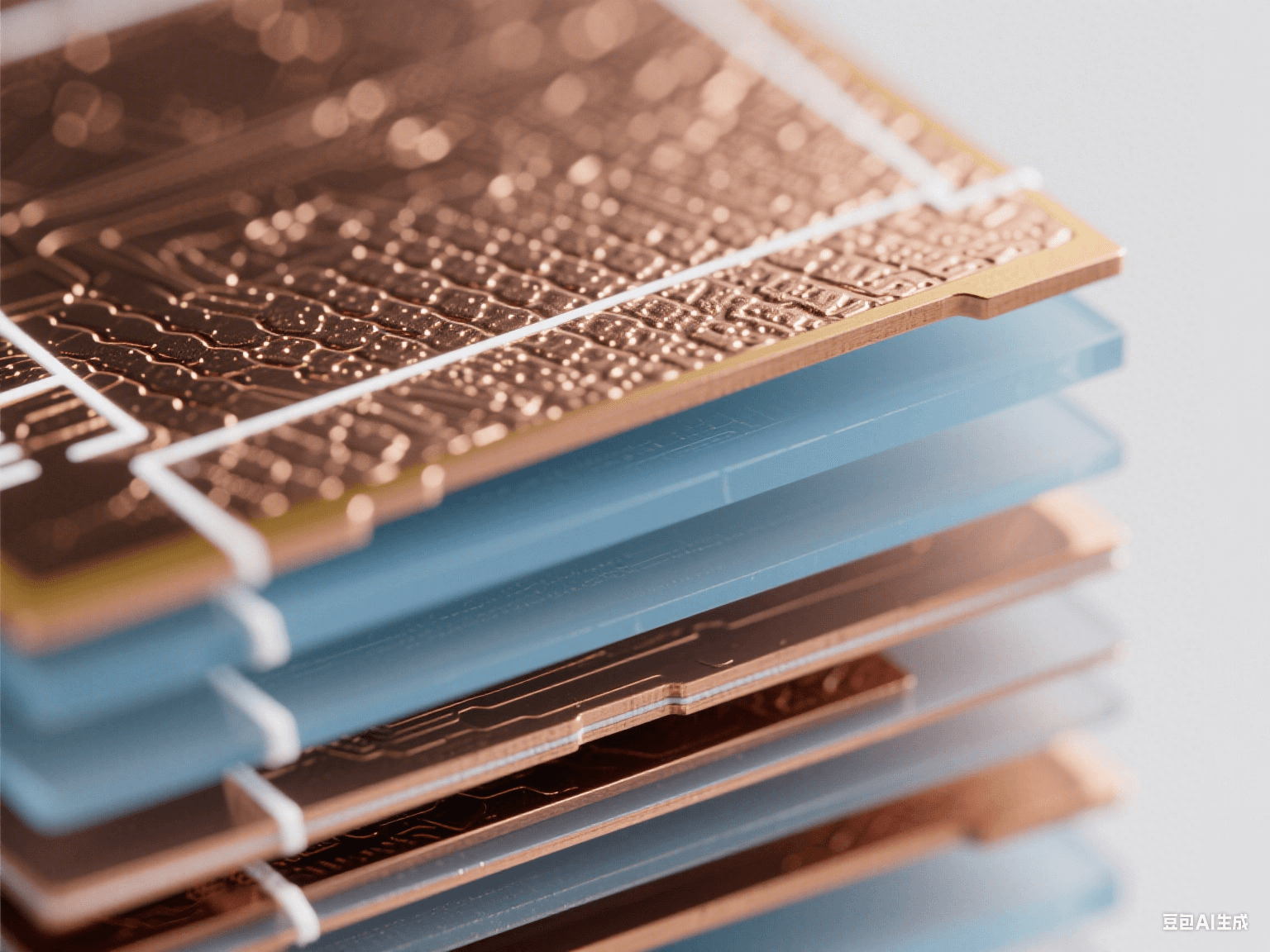

现代PCB 叠层结构优化深度依赖新材料和新工艺。高玻璃化转变温度 (Tg)、低损耗 (Low Loss)、超低损耗 (Very Low Loss) 的覆铜板材料不断涌现,为高速、高频设计提供更多选择。混合叠层技术(Hybrid Stackup)允许在同一块 PCB 上组合使用不同性能等级的基材(如高速数字部分使用低损耗材料,普通电路使用标准 FR4),实现成本与性能的最优配置。背钻(Controlled Depth Drilling)技术能有效去除高速信号过孔上不必要的高频谐振短桩(Stub),提升信号质量。任意层互连(Any Layer HDI)技术通过极微细的激光孔和电镀填孔工艺,实现超高密度互连,为小型化、高性能设备提供支撑,其叠层设计更为精密复杂。

实现成功的PCB 叠层结构优化是一个系统工程:

1. 需求定义:明确电路功能、信号速率、电源电流、工作环境、成本目标、尺寸限制及 EMC 要求。

2. 叠层方案规划:初步确定层数、信号 / 电源 / 地层分配、关键阻抗目标值。

3. 材料选型:根据电气、热、机械和成本要求选择核心 / 半固化片材料、铜箔类型。

4. 详细参数计算与仿真:使用专业工具(如 Polar SI9000, Ansys HFSS, Cadence Sigrity)精确计算阻抗、插入损耗、串扰;进行电源完整性(PI)和热仿真分析。

5. 叠层图(Stackup Drawing)生成:清晰标注各层顺序、材料型号、厚度、铜厚、完成厚度公差、阻抗控制要求。

6. 与制造商协作:将叠层图提供给 PCB 制造商进行可行性评估(DFM),根据其反馈微调材料或结构。

7. 原型制作与测试:制作原型板,通过 TDR(时域反射计)、网络分析仪、示波器等设备进行信号完整性、电源完整性和 EMC 测试,验证设计并迭代优化。

• 5G 通信基站:毫米波 AAU 板卡采用超低损耗材料(如罗杰斯 RO4835™)和复杂混合叠层,严格控制射频通道的插损和相位一致性,优化散热路径应对高功耗 PA 散热需求。

• 人工智能服务器:GPU 加速卡需多层(16L 以上)设计,通过密集的电源 / 地平面对和优化的叠层阻抗,确保高速 SerDes 通道(如 PCIe 5.0/6.0, DDR5)的信号完整性及大电流供电的稳定性。

• 高端医疗器械(如 MRI):对低噪声和超高可靠性要求严苛,叠层优化侧重于多层屏蔽设计、低热膨胀系数材料选择以抵御温度循环,确保微弱生物电信号采集的准确性。

• 汽车 ADAS 控制器:在严苛的车规环境(温度、振动)下,叠层设计需选用高可靠性材料,优化热管理设计,并确保高速摄像头、雷达传感器接口的信号完整性。

在电子产品持续向高速化、小型化、多功能化发展的浪潮中,PCB 叠层结构优化已从一项基础设计环节跃升为核心竞争力。它深刻影响着电子系统的性能上限、可靠性水平和制造成本。掌握其原理、方法并紧跟材料工艺发展,是电子工程师和 PCB 设计师不可或缺的关键能力。深入理解信号、电源、热、EMC 之间的复杂耦合关系,借助先进的设计与仿真工具,并与制造伙伴紧密协作,才能持续实现PCB 叠层结构的卓越优化,为下一代电子设备的创新突破提供坚实的硬件平台。

欲了解更多专业 PCB 叠层设计 解决方案,欢迎联系 IPCB (爱彼电路) 技术团队!