在半导体芯片的批量生产中,ATE 测试板是连接自动测试设备(ATE)与被测器件(DUT)的关键载体,其性能直接决定了芯片良率判定的准确性。本文结合行业前沿技术与公开技术白皮书,深度解析 ATE 测试板的材料选型、结构设计及可靠性优化方案,揭秘如何通过精密制造实现 0.1% 以下的测试误判率,为芯片设计、制造企业提供技术参考。

一、ATE 测试板的技术原理与核心价值

一、ATE 测试板的技术原理与核心价值

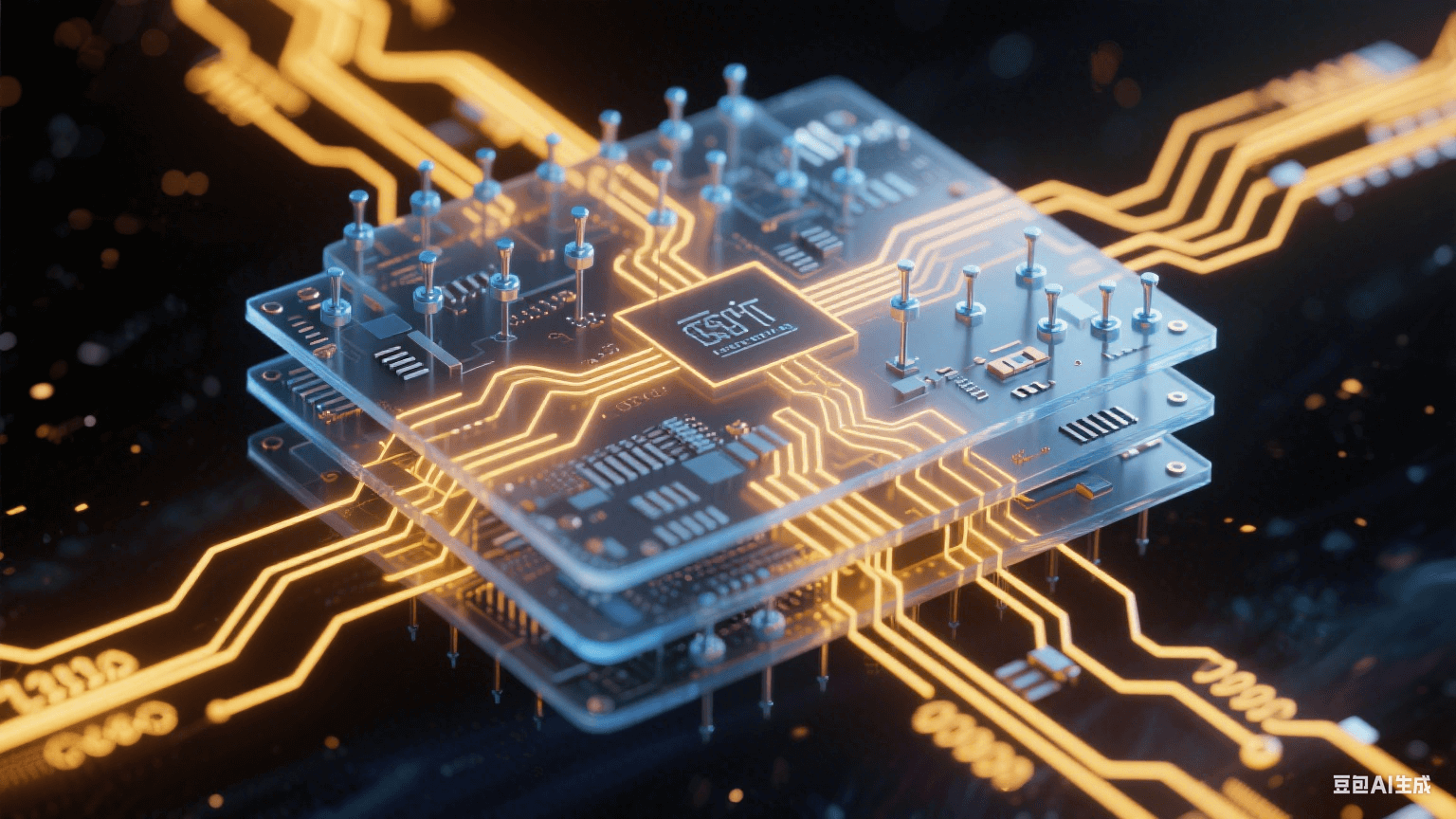

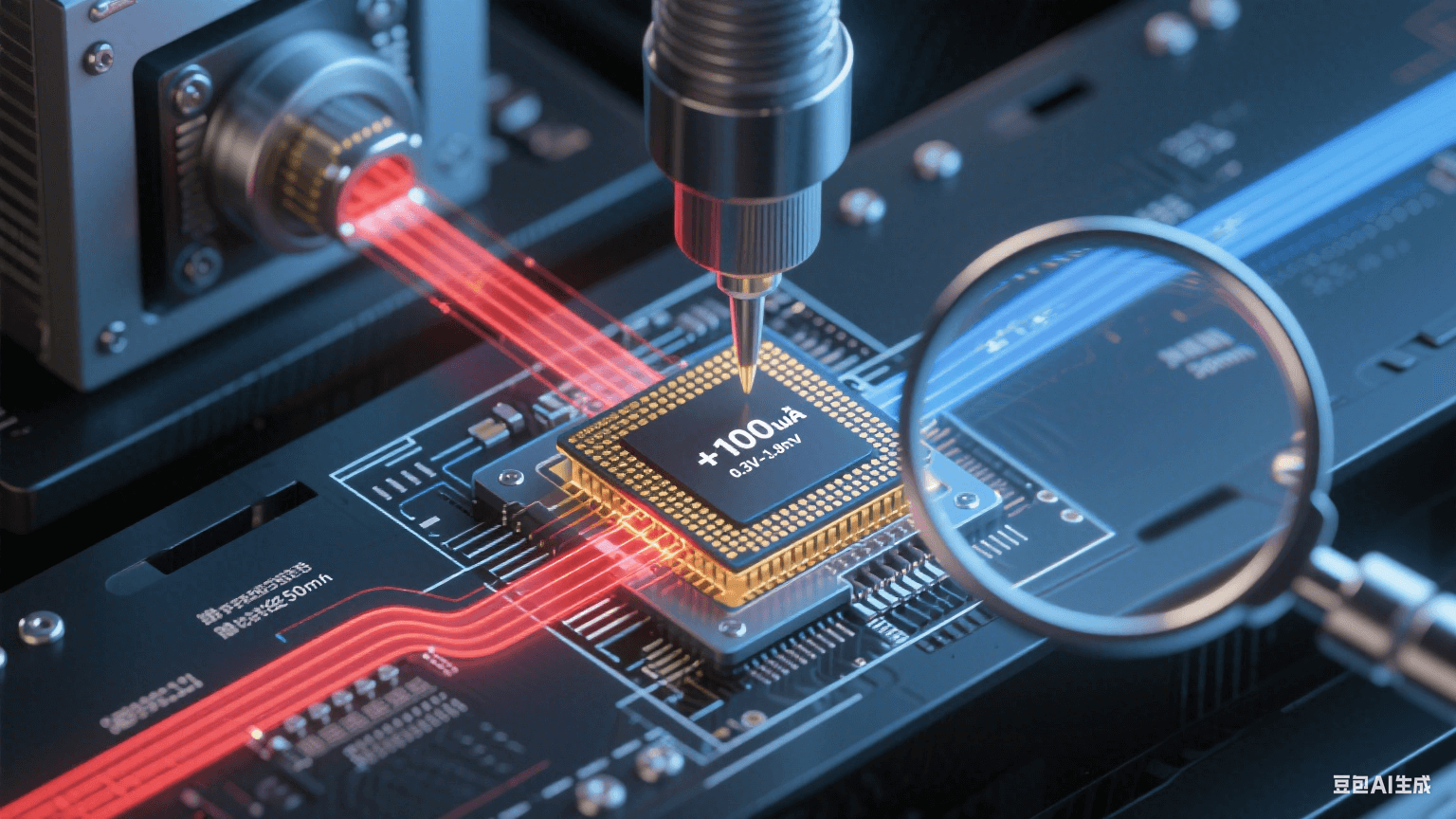

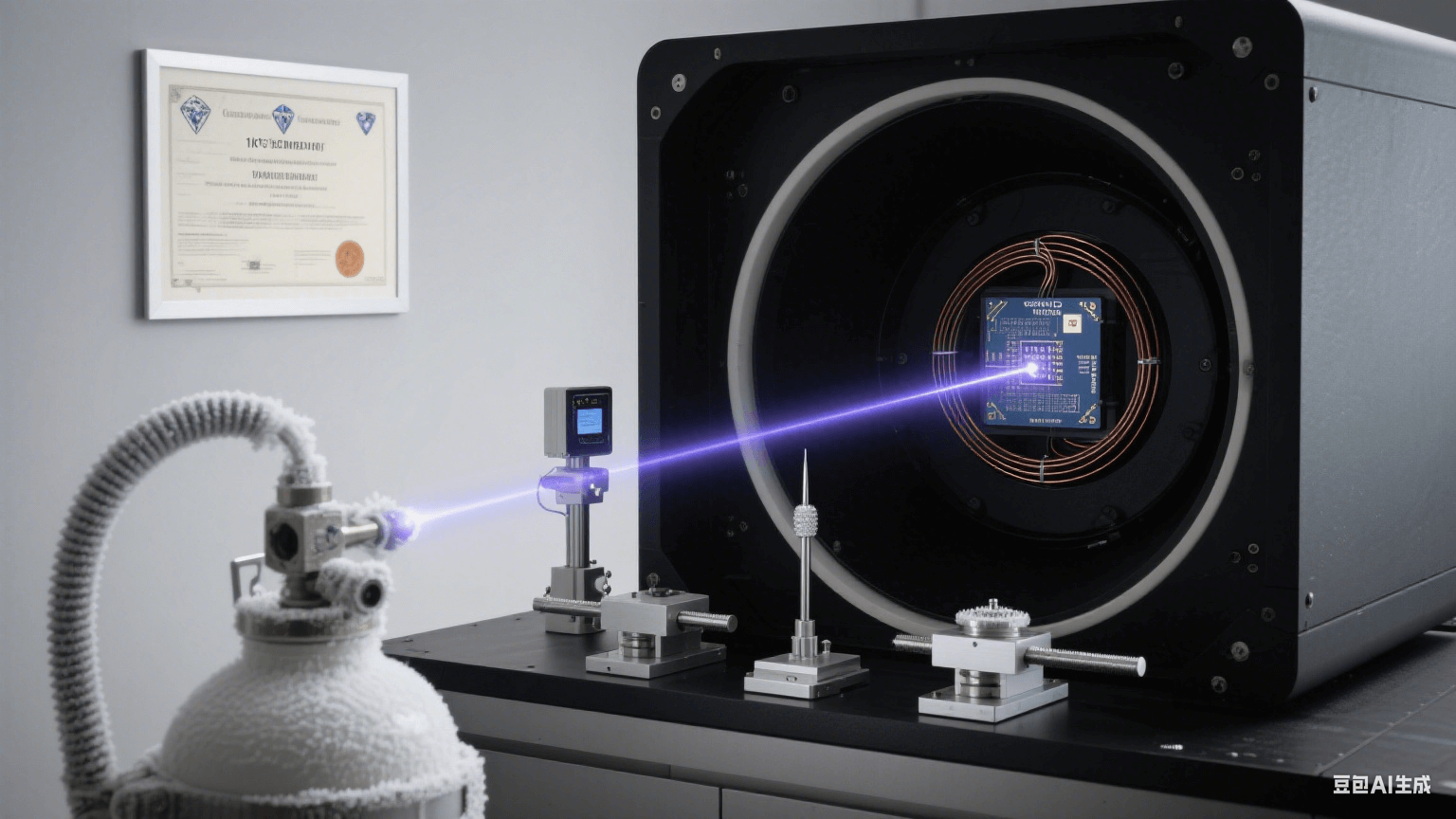

ATE 测试板的核心功能是实现测试机与芯片之间的信号精准传递。其工作原理可简化为 “激励输入 - 响应输出 - 对比判定” 的闭环流程。测试机通过 ATE 测试板向芯片施加特定电信号(如直流电压、脉冲序列),同时采集芯片的输出响应,与预设标准值对比后判定芯片是否合格。例如,在检测芯片 Pin 脚保护二极管时,需通过 ATE 测试板注入 ±100μA 电流,并测量电压是否在 0.3V~0.8V 范围内。

这种信号传输对测试板的电气性能提出严苛要求:接触电阻需≤50mΩ 以避免信号衰减,绝缘阻抗需≥10GΩ 以防止串扰,同时需支持最高 50GHz 的高频信号传输。

根据测试阶段不同,ATE 测试板可分为晶圆测试(CP)用探针卡和封装测试(FT)用负载板。前者需在微米级间距下实现探针与芯片焊盘的可靠接触,后者则需适配多种封装形式(如 QFN、BGA)的机械接口。

两类测试板共同面临的挑战包括:

热管理:高密度测试时,探针接触点温升可达 15℃以上,可能导致芯片参数漂移;

信号完整性:在 10GHz 以上频率下,传输线阻抗偏差需控制在 ±5% 以内,否则会引发反射和失真;

机械精度:探针卡的平面度需≤±2μm,以避免弹坑效应损坏晶圆。

二、核心组件的选型与设计要点

二、核心组件的选型与设计要点

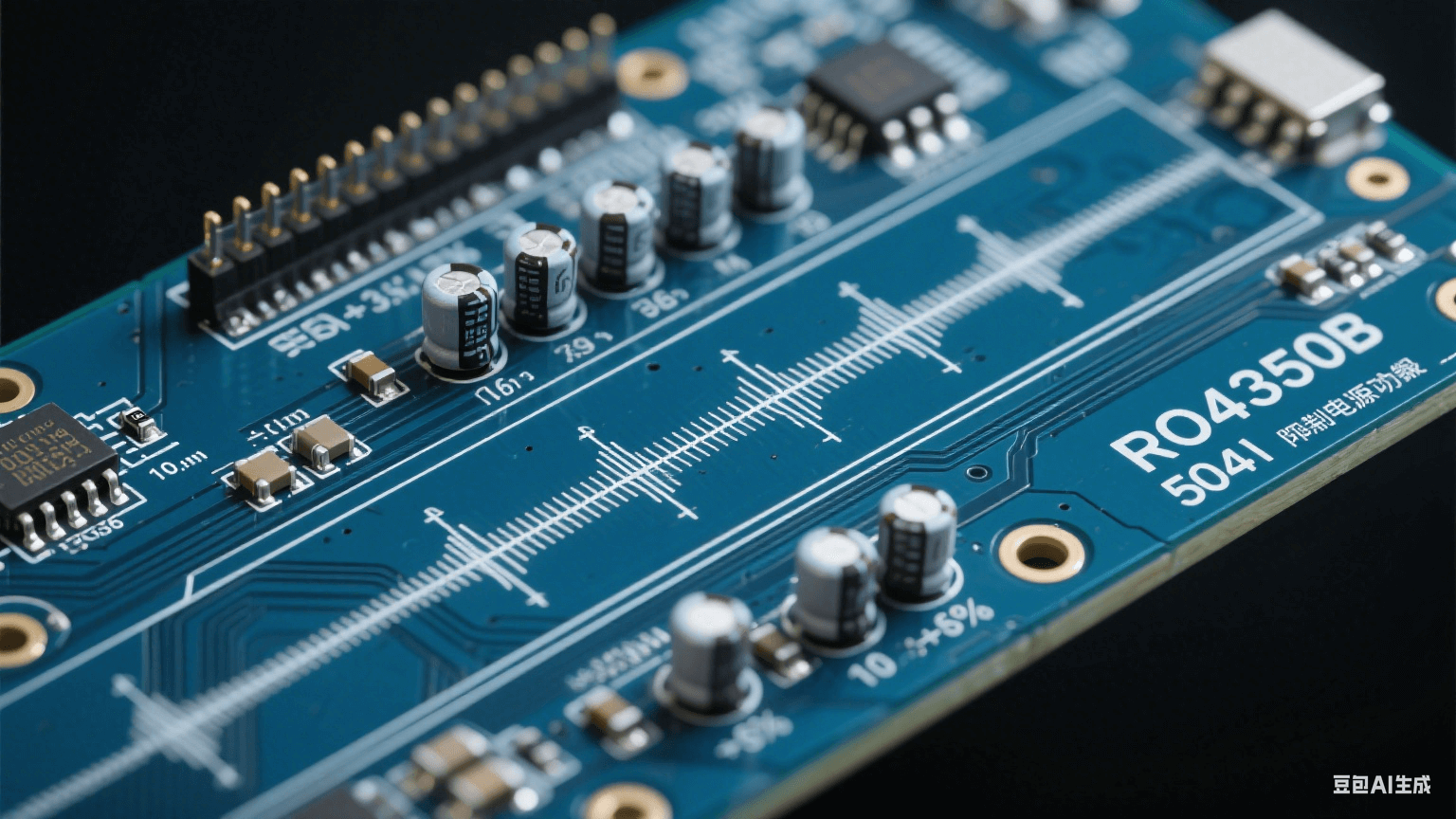

ATE 测试板通常采用高频高速材料,如 RO4350B(介电常数 3.66@10GHz)或 EM-827(介电损耗 0.002@10GHz)。这类材料的选择需平衡以下参数:

介电特性:低介电常数可减少信号延迟,低损耗因子可降低高频下的能量衰减;

热膨胀系数(CTE):需与探针卡框架材料(如殷钢)匹配,避免热应力导致结构变形;

机械强度:20 层以上的多层板需承受≥50N 的探针接触力而不发生分层。

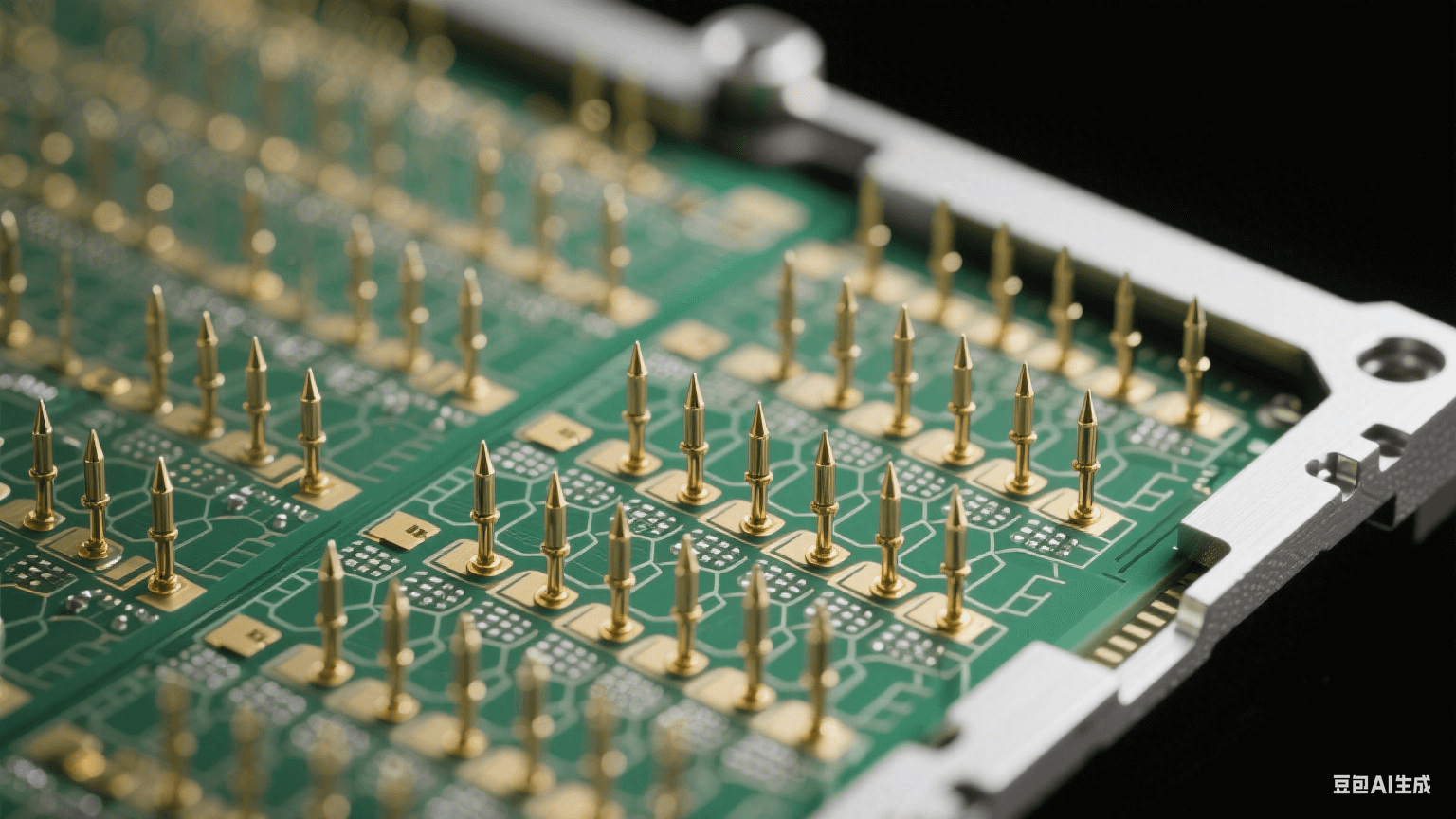

探针卡与测试板的协同设计是确保测试精度的关键。行业实践表明,当探针接触力控制在 8-12gf、针尖曲率半径≤5μm 时,测试板的探针寿命可达 8 万次以上,较常规参数(15gf 接触力、10μm 曲率半径)提升 50%。

为实现这一目标,需遵循以下原则:

探针阵列布局优化:采用交错排列或蜂窝结构,可将信号通道密度提升 30%,同时减少相邻探针的电磁干扰;

焊盘表面处理:镀金层厚度需≥3μm,且粗糙度 Ra≤0.1μm,以降低接触电阻并防止氧化;

应力释放设计:在探针密集区域增加应力缓冲层(如聚酰亚胺薄膜),可将探针断裂风险降低 60%。

高频测试板需采用多层差分对设计,例如:

阻抗控制:50Ω 微带线的线宽公差需≤±5%,蚀刻深度公差≤±2μm;

层间对准:内层图形与外层图形的偏移需≤±10μm,否则会导致信号传输延迟不一致;

去耦设计:每 10 个信号引脚需配置 1 个 0.1μF 的高频陶瓷电容,以抑制电源噪声。

三、测试流程优化与质量控制

三、测试流程优化与质量控制

ATE 测试板的校准分为三个阶段:

开路 / 短路校准:通过标准件消除测试板本身的寄生参数影响;

负载校准:在实际测试负载下验证信号传输延迟和损耗;

动态校准:在测试过程中实时监测探针接触电阻,当变化超过 10% 时自动触发重新校准。

这种校准流程可将测试误判率从 0.3% 降低至 0.08%,尤其适用于 5G 射频芯片等高精度测试场景。

为确保测试板的长期稳定性,需进行以下测试:

温度循环测试:在 - 40℃~125℃范围内进行 1000 次循环,验证材料的热疲劳性能;

振动测试:在 20-2000Hz 频率下施加 5G 加速度,检查焊点和机械结构的可靠性;

寿命测试:通过 10 万次探针插拔实验,评估焊盘和探针的磨损程度。

随着先进封装技术(如 Chiplet、SiP)的普及,ATE 测试板的通道密度需从当前的 2000pin 提升至 5000pin 以上,同时线宽 / 线距需突破 30μm/30μm 的极限。例如,某 3nm 制程晶圆测试板已采用 0.15mm 微孔和 0.05mm 线宽设计,可支持 1024 个探针的密集排列。

未来 ATE 测试板将集成更多智能功能:

嵌入式传感器:实时监测探针接触力、温度等参数,实现异常预警;

机器学习算法:通过历史测试数据预测探针磨损趋势,优化测试周期;

自适应阻抗匹配:根据被测芯片的特性自动调整信号传输参数,提升测试效率。

除传统集成电路测试外,ATE 测试板正逐步渗透至以下领域:

功率半导体:用于 IGBT、SiC MOSFET 等器件的高压大电流测试,需耐受 1200V 电压和 200A 电流;

车规级芯片:满足 AEC-Q200 标准,支持 - 40℃~150℃宽温环境下的稳定测试;

量子芯片:开发低噪声、高隔离度的测试板,适配量子比特的超低温(<1K)测试需求。

从 28nm 到 3nm 制程的演进,ATE 测试板始终是半导体检测的 “精度守门人”。随着半导体产业向更高性能、更低功耗方向发展,测试板技术将持续突破信号完整性、热管理和机械可靠性的边界。企业需紧跟行业趋势,通过材料创新、结构优化和智能化升级,打造适配未来测试需求的高精度载体,为全球半导体产业链的高质量发展提供坚实支撑。