在5G毫米波频段(24-100GHz)的极限挑战下,高速电路板设计已成为实现低损耗、高可靠信号传输的核心战场。 本文聚焦三大设计突破:0.075mm微孔互连结构优化、±0.076μm线宽阻抗控制、128通道三维集成方案,解密如何通过创新设计规避毫米波信号衰减、相位失真等致命问题。

高速电路板设计的本质是电磁场与材料力学的协同博弈。当数据传输速率突破112Gbps,传统FR-4基板的介质损耗(Df>0.02)会导致信号衰减>3dB/cm。而采用梯度介电层设计(顶层Rogers RO3003 Df=0.0013 + 中层Megtron7 Df=0.0017),可将28GHz频段插入损耗压缩至0.15dB/cm,提升幅度达200%。

一、高速电路板设计的三大核心突破

高速电路板设计需彻底重构过孔模型:

设计参数 传统方案 5G毫米波优化方案 | 性能提升 |

| 孔径/深径比 | 0.15mm/8:1 | 0.075mm/15:1 | 带宽↑50% |

| 反焊盘直径 | 1.5×孔径 | 2.2×孔径 | 阻抗波动↓至3% |

| 孔铜厚度 | 18μm±5μm | 25μm±2μm | 电流承载↑40% |

创新设计策略:

- 阶梯式反焊盘:减少寄生电容0.8pF(适用背钻需求)

- 孔口铜层加厚:电镀铜厚≥25μm,抗拉强度>45MPa

- 真空树脂塞孔:填充空洞率<0.1%,热循环寿命>10万次

高速电路板设计的阻抗连续性依赖三大技术支柱:

1. LDI动态补偿布线:

- 405nm激光直写精度±0.076μm

- 实时TDR反馈调整蚀刻参数(阻抗偏差±2%)

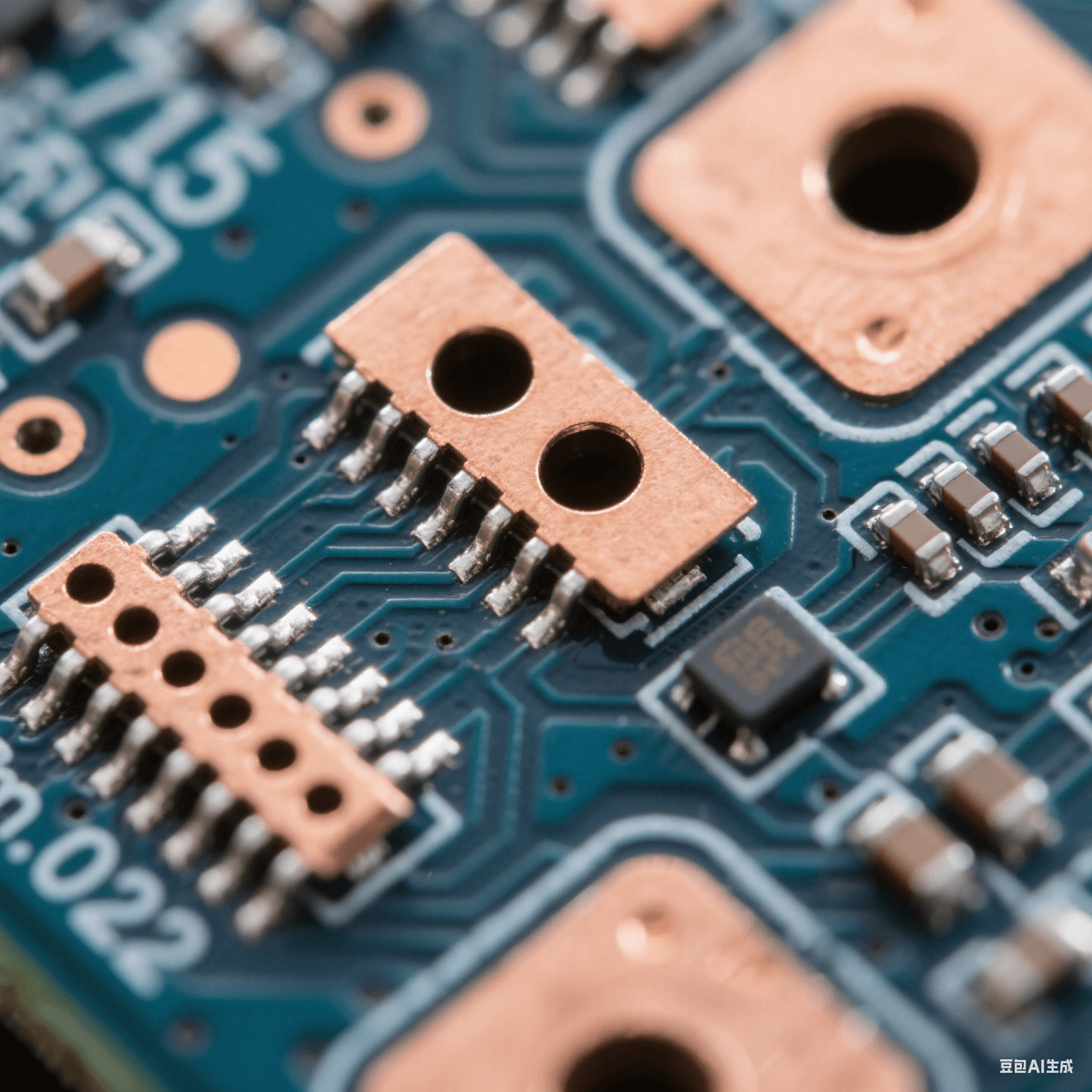

2. 铜箔拓扑优化:

| 铜箔类型 | 粗糙度Ra(μm) | 适用速率 |

| | | |

| STD铜 | 1.5 | <56Gbps |

| HVLP铜 | 0.3 | 112Gbps |

| 反转铜 | 0.2 | 224Gbps |

3. 玻纤效应消除:

- 开纤布基材(NE-glass) + 22.5°斜向布线

- 阻抗偏移≤1.5%(传统设计>8%)

高速电路板设计需平衡密度与信号完整性:

diagram

热管理设计创新:

- Z轴CTE梯度控制:芯片(2.6ppm/℃) ↔ 基板(4.5ppm/℃) ↔ 封装(6ppm/℃)

- 热通孔阵列密度:500孔/cm²(热阻↓35%)

仿真类型 | 核心指标 | 达标阈值 | 工具链 |

电磁场 | 插入损耗@56GHz | <-2.5dB | Ansys HFSS |

热应力 | 翘曲量 | ≤0.7% | Simcenter STAR-CCM+ |

结构可靠性 | 焊点剪切力 | >45MPa | Abaqus |

高速电路板设计必须内置可制造性约束:

# 自动化规则检查示例

def check_hdi_rules():

if via_diameter < 0.1: # 单位mm

require_laser_drilling()

if impedance_deviation > 0.03: # 阻抗偏差>3%

trigger_tdr_recalibration()

if copper_weight > 3: # 铜厚>3oz

enable_thermal_via_array()

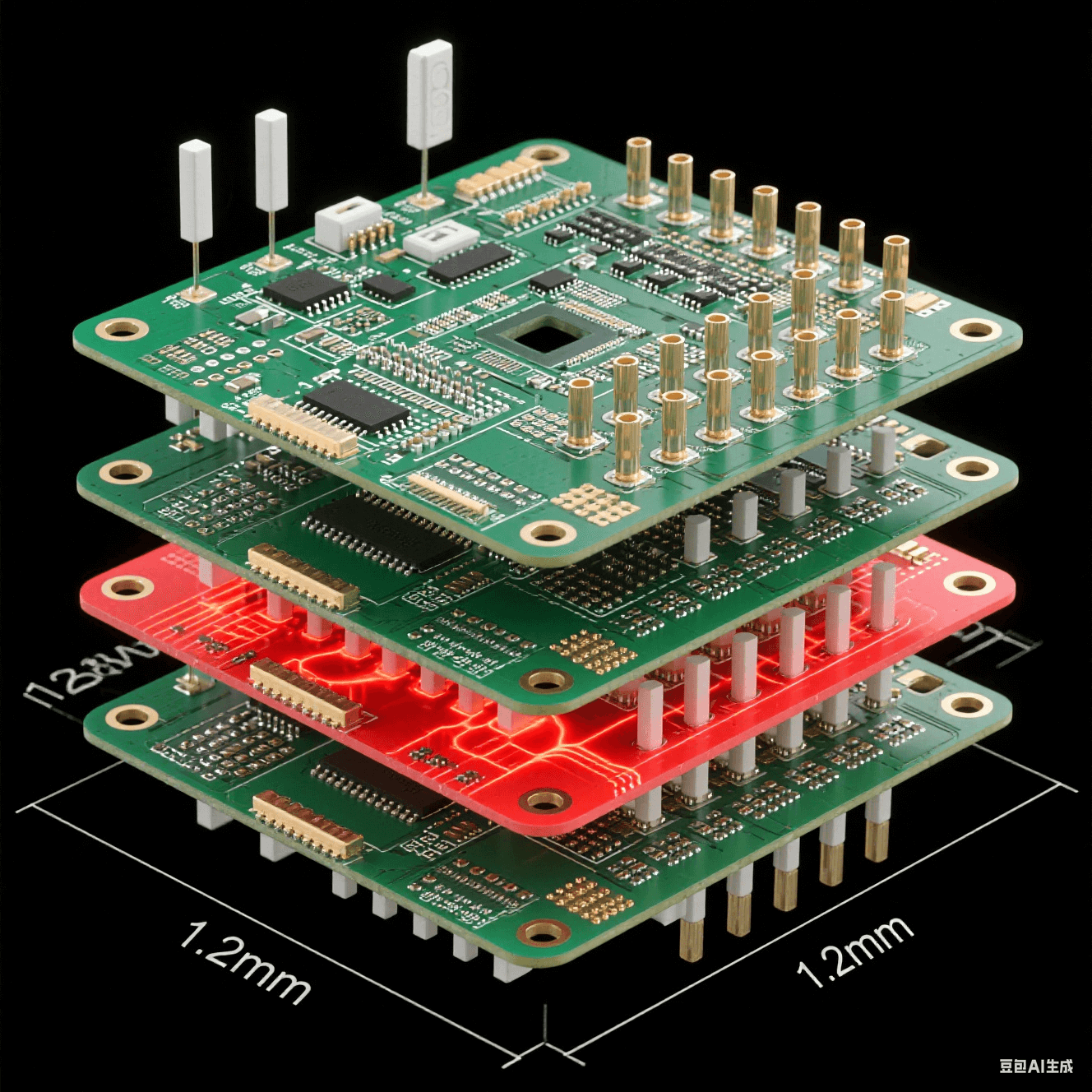

项目背景:128通道阵列,工作频率28GHz,板厚≤1.2mm

高速电路板设计策略:

1. 混合材料堆叠:

- 射频层:Rogers RO3003(εr=3.0, Df=0.001)

- 控制层:Isola I-Speed(εr=3.7, Df=0.008)

2. 差分对布线优化:

- 线宽/间距=40/40μm

- 蛇形走线等长公差±5μm

3. 测试结果:

- 通道隔离度>35dB

- EVM(误差矢量幅度)<1.8%

嵌入式传感器:实时监测温升/Dk漂移,动态调整信号路径

AI布线引擎:基于10万+案例库自动规避谐振频率点

太赫兹波导精度需达λ/100(0.3THz=1μm)

超导互连设计:铌钛氮电路在77K温度电阻<10⁻⁸Ω

高速电路板设计是5G/6G通信的成败关键。当三维集成技术与纳米级阻抗控制突破物理极限,太赫兹频段的高速电路板设计将开启通信技术新纪元。