高速电路板设计技术阻抗匹配是指负载阻抗与激励源内部阻抗相互适应,获得最大功率输出的一种工作状态。为了防止高速PCB布线时的信号反射,要求电路的阻抗为50Ω。这是一个近似数字。一般规定同轴电缆的基带为50Ω,频带为75Ω,双绞线为100Ω。它只是一个整数,为了匹配方便。

根据具体电路分析,采用并联交流终端,电阻电容网络作为终端阻抗。端接电阻R必须小于或等于传输线阻抗Z0,电容C必须大于100pF。推荐使用0.1UF多层陶瓷电容。电容具有阻低频通高频的作用,所以电阻R不是驱动源的直流负载,所以这种端接方式没有任何直流功耗。

串扰是指信号在传输线上传播时,由于电磁耦合到相邻传输线上而引起的不希望有的电压噪声干扰。耦合分为电容耦合和电感耦合。过大的串扰可能会导致电路误触发,导致系统无法正常工作。根据串扰的一些特点,可以总结出几种降低串扰的方法:

1、增加线距,减少平行长度,必要时采用点动法接线。

2、当高速信号线满足条件时,增加端接匹配可以减少或消除反射,从而减少串扰。

3、对于微带传输线和带状传输线,将走线高度限制在地平面范围内可以显着降低串扰。

4、在布线空间允许的情况下,在串扰比较严重的两根线之间插一根地线,可以起到隔离的作用,从而减少串扰。传统PCB设计由于缺乏高速分析和仿真指导,信号质量无法保证,大部分问题要到制版测试才能发现。这大大降低了设计效率,增加了成本,在激烈的市场竞争中显然处于劣势。

因此,对于高速PCB设计,业内人士提出了一种全新的设计思路,成为一种“自顶向下”的设计方法。经过各种策略分析和优化,大部分可能出现的问题都被规避了,节省了很多。确保满足项目预算、生产高质量印制板并避免繁琐且代价高昂的测试错误的时间。使用差分线传输数字信号是控制高速数字电路中破坏信号完整性因素的有效措施。

印刷电路板上的差分线相当于工作在准TEM模式下的差分微波集成传输线对。其中,位于PCB顶部或底部的差分线相当于耦合微带线,位于多层PCB内层的差分线相当于宽边耦合带线。

数字信号以奇模传输方式在差分线上传输,即正负信号的相位差为180,噪声以共模方式耦合在一对差分线上,接收器中的正负两个通道的电压或电流相减,从而得到消除共模噪声的信号。差分对的低电压幅值或电流驱动输出,实现了高速集成和低功耗的要求。

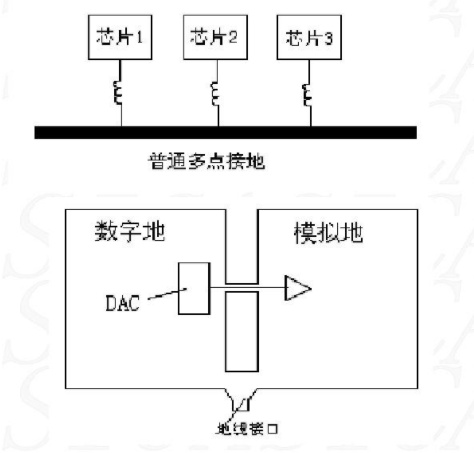

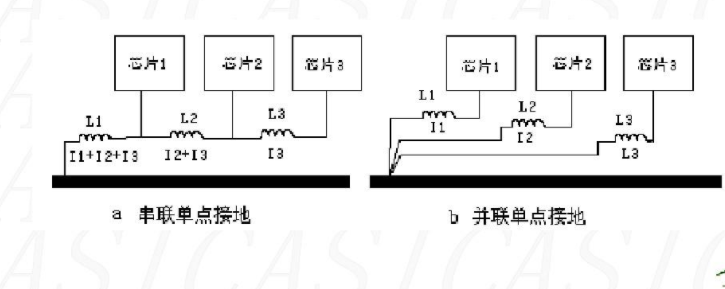

三种接地方式:

1、单点接地:适用于低频电路,优点是保证接地回路互不干扰。

2、浮地:可以将电路板地与其他地隔离,减少干扰。常用于工业控制和PLC。

3、多点接地:高速电路使用,优点是接地回路阻抗最小。