首先介绍叠层封装技术的发展现状及最新发展趋势 , 然后采用最传统的两层叠层封装结构进行分析 , 包括描述两层叠层封装的基本结构和细化两层叠层封装技术的 SMT组装工艺流程。最后重点介绍了目前国际上存在并投入使用的六类主要的叠层封装方式范例 , 同时进一步分析了叠层封装中出现的翘曲现象以及温度对翘曲现象的影响。分析结果表明 :由于材料属性不同会引起正负两种翘曲现象;从室温升高到 150 ℃左右的时候易发生正变形的翘曲现象, 在 150 ℃升高至 260 ℃的回流焊温度过程中多发生负变形的翘曲现象。

随着半导体制造技术以及立体封装技术的不断发展 , 电子器件和电子产品对多功能化和微型化的要求越来越高。在这种小型化趋势的推动下 , 要求芯片的封装尺寸不断减小。根据国际半导体技术路线图 (ITRS), 三维叠层封装技术能更好的实现封装的微型化 。三维叠层封装具有如下特点 :封装体积更小 , 封装立体空间更大, 引线距离缩短从而使信号传输更快, 产品开发周期短投放市场速度快等。叠层封装主要应用在移动手机、 手提电脑、数码相机等手持设备和数码产品中。三维叠层封装主要分为三种形式:载体叠层 、 裸芯片叠层和晶圆叠层。3D裸芯片叠层封装技术主要有多芯片封装 (multi-chippackaging, MCP)、内置封装技术(package-in-package,PiP)和 叠 层 封 装 技 术(package-on-package, PoP)。本文主要介绍叠层封装。PoP就是在一个处于底部的封装件上再叠加另一个与其相匹配的封装件 , 组成一个新的封装整体。PoP的各封装件之间相对比较独立 , 同时能对底部和顶部的封装器件进行单独测试, 以保证其满足预先设定的参数和良好的性能, 这样更能满足KGD (knowngooddie)的要求 , 有较高的器件封装良品率。由于 PoP封装的独立性表现在保证各封装体测试过关的前提下可以将不同厂商的封装器件堆叠匹配封装在一起, 所以器件的选择也具有更大的自由灵活性 , 这是 PoP工艺的最大优势。同时在PoP封装中即使出现了问题 , 也可以拆开来单独检修、测试 , 因而堆叠封装技术 PoP成为主要的 3D封装技术 。最简单的 PoP封装包含两个叠层裸芯片, 具体实例有日本的堆叠式内存 , 这种堆叠式内存结构由含有一个闪存和一个 SRAMM内存的双裸片组 成的;目前, 叠层 密 度最 高 的实 例 是Samsung公司应用于 3G手机的 6层叠层存储芯片;同时作为引线键和叠层方式的扩展 , ASE公司在叠层封装中使用了引线键合和倒装键合相结合的混合键合的封装方式。

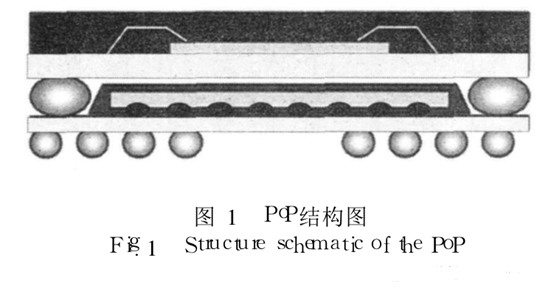

叠层封装技术经过近十年的时间, 已经发展得十分成熟。叠层封装器件分为两类 :一类是存储器与存储器堆叠在一起;另一类是底层为逻辑器件而顶层为存储器件。最典型的叠层封装技术 PoP的封装模型由图 1所示。

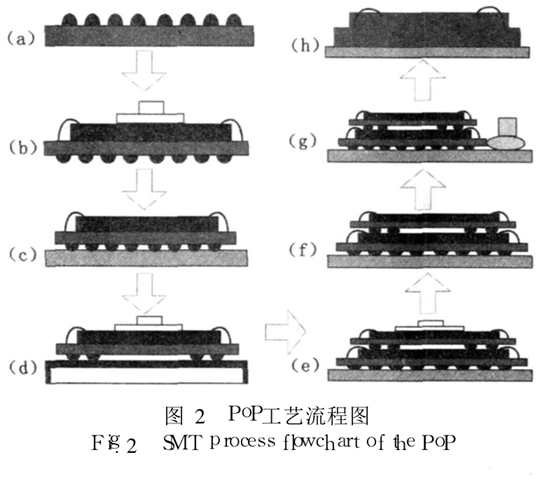

最简单的 PoP模型是两层堆叠模型 , 除此之外还有多层堆叠模型。一般简单的两层堆叠模型组成结构是分为上下两部分 , 即底部和顶部 , 而且底部和顶部的封装器件功能是不同的。通常情况下底部的封装件是一个高集成度的逻辑器件, 顶部的封装件是一大容量的存储器或存储器件组合。多层堆叠封装体的结构与简单叠层封装体结构相比, 不同之处在于其顶部可以是多个具有存储功能的存储器封装器件。由综上所述可以看出叠层封装技术 PoP的出现已经模糊了封装与组装的界线。本文以最简单的两层叠层封装技术为例介绍其 SMT封装流程 ,其封装流程图如图 2所示 。在进行 PoP的 SMT封装之前首先要对非 PoP面元件进行组装, 其中的工艺流程包括传统的丝网印刷、 贴片、回流和检测 。然后再进行 PoP面元件的组装。叠层封装技术 PoP的 SMT工艺流程如图 2所示。

图 2中 : (a)图为首先利用表面贴装技术在封装基板上贴装元件如电阻、电容等; (b)图为然后拾取 PoP底部封装器件; (c)图为将底部封装器件放置在基板上, 进行贴装 ; (d)图为在顶部基板上涂覆助焊剂; (e)图为将顶部封装器件放置在底部封装器件上;(f)图为对整体封装器件进行回流焊接; (g)图为对 PoP封装体进行底部填充; (h)图为对 PoP封装体的底部填充进行固化 , 从而完成 PoP的 SMT封装。

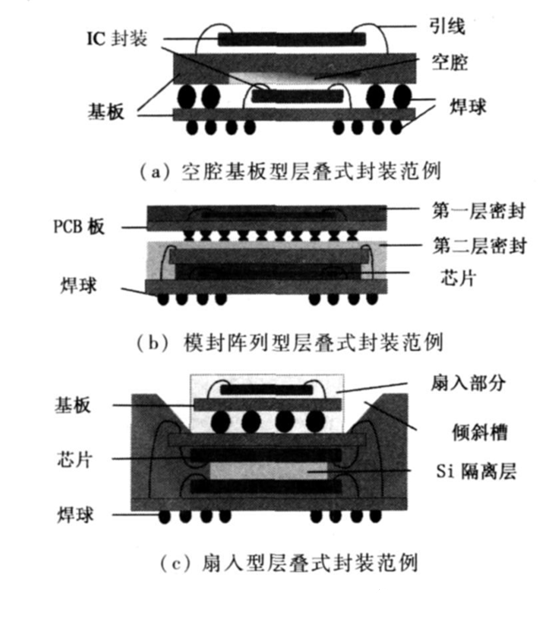

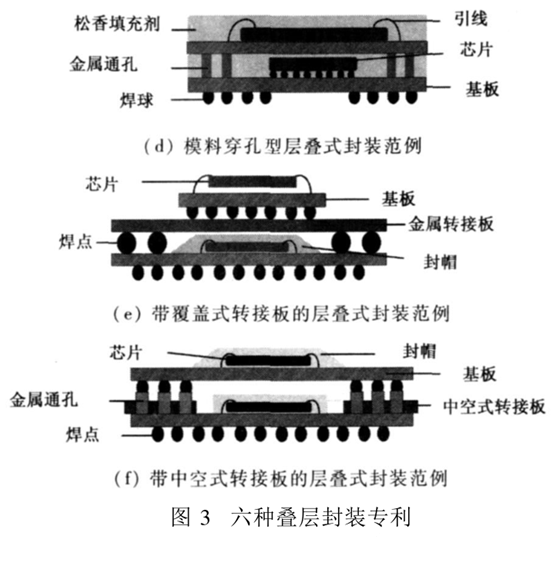

由于 PoP封装技术能更好地实现封装的微型化 , 并且具有如下特点:封装体积更小, 封装立体空间更大, 引线距离缩短从而使信号传输更快 , 产品开发周期短投放市场速度快等, 所以被广泛地应用在移动手机、手提电脑 、数码相机等手持设备和数码产品中 。国际上关于 PoP封装技术的专利有几十种, 主要分为以下七类 :常规叠层式封装、带中空式转接板的层叠式封装 、带覆盖式转接板的层叠式封装 、空腔基板型层叠式封装、 模封阵列型层叠式封装、 模料穿孔型层叠式封装和扇入型层叠式封装。各类封装范例如图 3所示。

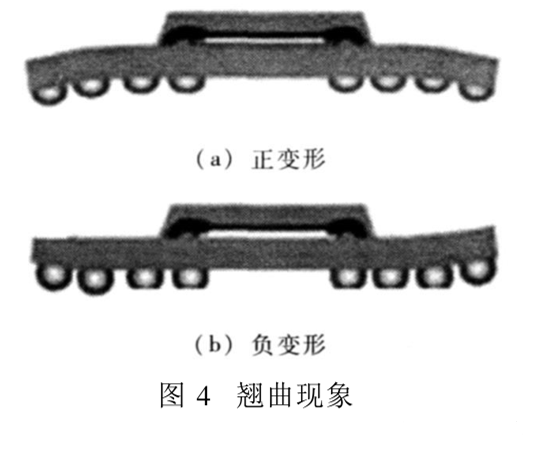

PoP封装面临的最严重的可靠性问题是翘曲现象。习惯上将翘曲现象根据形状定义如下:若翘曲形状为向上凸则称之为正变形, 若翘曲形状为向下凹就称之为负变形 , 如图 4所示。

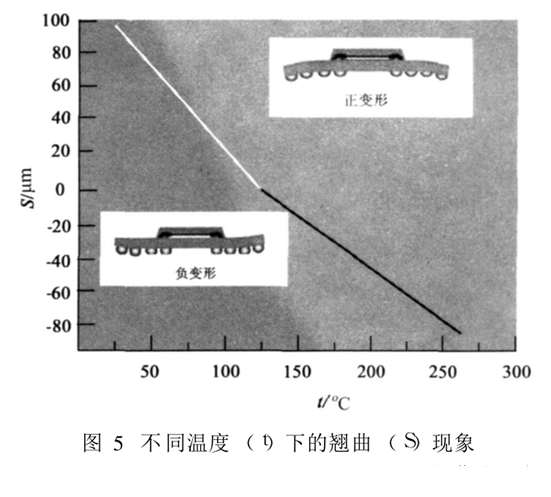

影响翘曲因素主要是封装基板和芯片的材料属性 , 包括热膨胀系数 CTE和弹性模量。在室温和回流焊温度下材料属性对叠层封装翘曲现象的影响是不同的, 如图 5所示。

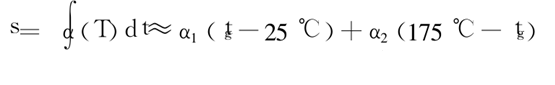

由图 5可以看到在室温下条件下随着弹性模量和热膨胀系数的变化 , 翘曲数值都基本为正, 表现为向上凸的正变形;而在回流焊高温条件下随着弹性模量和热膨胀系数的变化, 翘曲数值都为负数 ,表现为向下凹的负变形。目前改善叠层封装PoP翘曲现象的研究主要包括结构优化、材料选择和工艺优化三个方面。封装结构一般包括硅芯片 、 塑封材料和基板三部分, 其中硅芯片和基板之间的热膨胀系数不匹配是引起翘曲现象的主要原因。在由室温升高到回流焊温度又由高温逐渐冷却到室温的温度变化过程中 , 会产生化学收缩和热收缩现象 , 由此而导致翘曲现象。塑封料作为中间介质可以起到补偿作用 。塑封料中一般都含有超过80%的填充材料, 填充材料比例越大化学收缩值就会越小。而热收缩值由下面的等式决定。

式中:α表示热膨胀系数 ;tg 表示玻璃转换温度。由公式 (1)可知 , 减小α可以减小热收缩值 。所以在封装工艺中经常采用减小热膨胀系数的方法来降低翘曲现象。

另外还可以通过减小芯片尺寸大小和减薄芯片厚度来增大塑封料的比例 , 进而降低翘曲现象。常采用的芯片减薄方法有研磨、 深反应离子刻蚀法(DRIE)和化学机械抛光法 (CMP)等工艺, 通常减薄至 50 μm左右 , 目前减薄技术可将圆片减薄 10至 15 μm, 为确保电路的性能和芯片的可靠性, 圆片减薄的极限为 20 μm左右, 否则会影响存储器的性能。直接减薄芯片厚度, 产生的残余应力会影响存储器的性能。此时可以利用晶圆抛光技术来释放应力, 增强芯片的健壮性。

在满足电子产品更快数字信号处理、 更大存储容量、成本更低 、体积更小的要求, 尤其在堆叠复杂逻辑器件和存储器器件方面, PoP是一种上市时间短、 成本低的叠层封装解决方案。除了综上所述的可靠性问题, 叠层封装方案还存在着一些缺陷, 例如由于芯片尺寸不匹配而导致的线键合过程中的引线过长 , 就会增加引线键合工艺的难度和成本, 还可能会由于后道塑封工序的工艺问题出现金线冲弯、短路 、脱球等现象 , 从而导致封装产品的失效 ;由于引线键合过程中的布线密度比较高, 极易出现引线短路, 导致引线键合工艺失败;若相邻芯片的间距过小而无法进行引线键合, 则可能导致封装失败。这些工艺缺陷都是叠层封装面临的挑战 , 亟待解决。