导电胶分层作为封装失去效力问题,一直遭受广泛的关心注视。基于

ANSYS

平台,对导电胶脱落应力仿真,用来评估导电胶在封装和测试过程中分层风险,共进一步剖析了顶部芯片、绝缘胶厚度以及导电胶厚度对导电胶分层的影响。最后结果表明:

导电胶在靠得住性测试阶段 125

℃冷却到室温阶段最容易发生导电胶分层失去效力。该款封装中导电胶分层的端由是顶部叠层芯片结构引动的。经过对顶部芯片、绝缘胶的厚度施行预设,发觉其厚度越薄导电胶的脱落应力越小,分层风险越小。导电胶的厚度在

10 μm 时,胶体的粘贴力最大,脱落应力最小,导电胶分层风险最小。

随着电子工业对背景尽力照顾要求不断增长,传统封装中运用铅焊料污染背景,逐渐被环保导电胶接替。但导电胶的热体胀系数与芯片相差较大,在温变负荷下容易萌生热应力使导电胶分层。一朝导电胶分层严重将导致芯片功能失去效力。针对导电胶分层国里外学者施行了广泛的研究讨论和研讨。龙平觉得导电胶分层主要是因为热负荷下各局部膨胀和收缩不均引动的。Sujan

等对银胶剪切热失配双层板型的剖析表明,随着剪切力增大,导电胶分层程度减小。国内学者经过

ANSYS软件剖析导电胶的热应力,研讨基板厚度对导电胶最大热应力的影响,并提出封装结构优化的处理办法,随着基板厚度的增加,导电胶最大热应力先减小后增大,在基板厚度为

4~5 mm

时最小,导电胶分层现象有所改善。海外学者利用热循环后导电胶的群体等效应力并接合芯片剪切合实际验评估导电胶分层风险,但仅只减小等效应力最大值很难改善导电胶分层。固然利用有限元法剖析导电胶热应力是一种管用手眼,但仅剖析群体热应力最后结果并不可以直接评估导电胶与芯片界面分层风险。本文基于有限元法剖析导电胶的脱落应力,直接评估导电胶与芯片界面分层(导电胶分层)风险,减小导电胶分层。经过仿真最后结果剖析导电胶失去效力阶段及端由,并施行封装内里结构预设,改善导电胶分层。

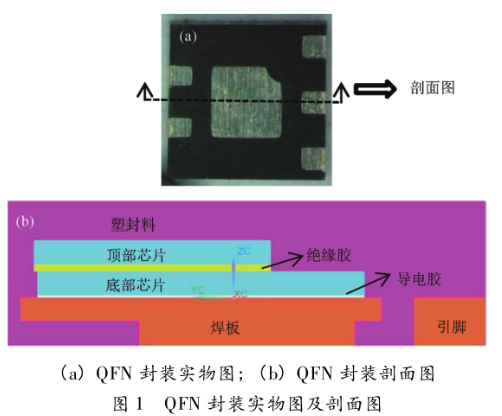

封装体由芯片、导电胶、绝缘胶、焊板及引脚、塑封料想到金线构成,如图

1 所示。金线对导电胶分层影响细小,故建模时可以疏忽。封装体尺寸为 2. 0mm×2. 0 mm×0. 6 mm,顶部芯片尺寸为 1. 37 mm×1mm×0.

12 mm,绝缘胶尺寸为 1. 37 mm×1 mm×0. 04mm,底部芯片尺寸为 1. 37 mm×1. 35 mm×0. 12 mm,导电胶尺寸为 1.

37 mm×1. 35 mm×0. 01 mm。

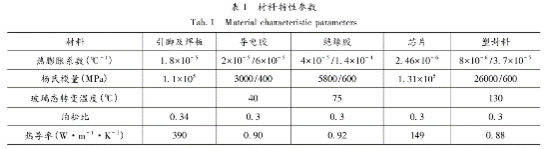

导电胶运用 Henkel 企业的 QMI519,塑封料运用 Nitto 企业 G770HCD,材料特别的性质参变量如表1 所示。导电胶和塑封料的热体胀系数(CTE)和杨氏模量(E)在玻璃态转变温度 T g 近旁激变。2×10-5/6×10-5和 3000/400 表达当温度低于 T g 时,导电胶CTE 和 E 的值作别为 2×10- 5℃-1和 3000 MPa,当温度高于 T g 时,CTE 和 E 作别取 6×10-5℃-1和 400MPa。同理塑封料也具备此类性质。

粘接界面的靠得住性由界面的粘贴力和内部策应力的体积表决。导电胶的粘贴力与本高矮胖瘦料相关。内部策应力由热应力和湿应力组成。QMI519

导电胶吸湿性很低,外部塑封料尽力照顾使潮气很难进入境内导电胶内里,故导电胶的湿应力较小。

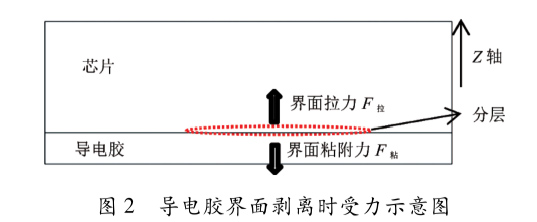

芯片在封装过程中经历复杂温度变动,导电胶必然性萌生热应力。热应力中与界面脱落有关的应力称作脱落应力。脱落应力分为拉应力和压应力,但只有拉应力才有界面脱落风险,拉应力越大则材料之间越容易产疏远层。因为这个,当导电胶材料未变事情状况下,可以用脱落应力体积评估导电胶分层风险。图 2 为导电胶界面脱落时受力概况图,界面张力是界面分层影响主要因素。

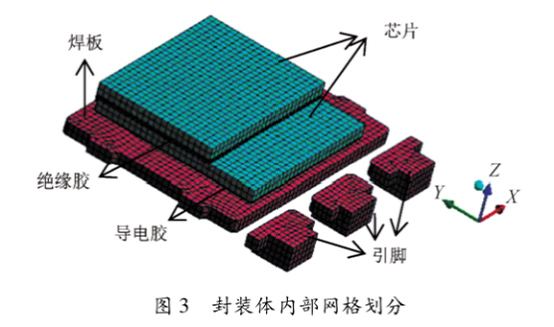

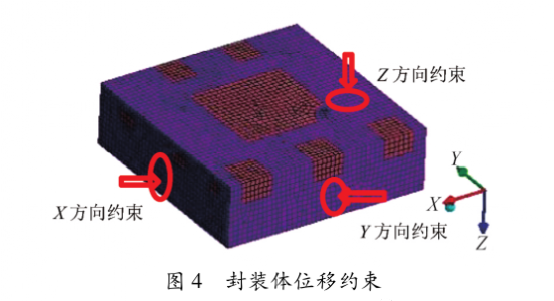

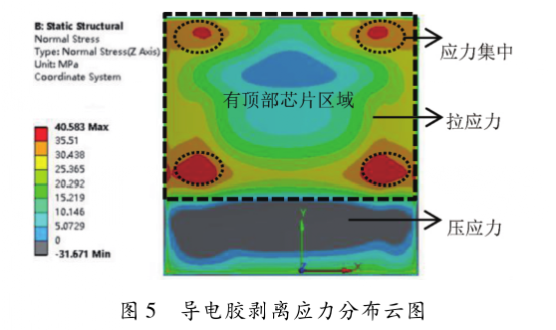

ANSYS 软件施行导电胶脱落应力仿真。图 3是封装体内里网格图,网格单元为 39964,节点数量为 191617。热剖析时室温为 25 ℃,参照温度为起初温度,参照温度时为零应力状况,用于计算导电胶的热应力。同时设置空气天然对流,焊板底部设置温度负荷,时间为 2400 s。静应力板块剖析时,设置底面为 Z 方向位移约束,左、面前为 X、Y 方向位移约束,如图 4 所示。导电胶在125 ℃冷却到室温时脱落应力如图 5 所示,导电胶有顶部芯片地区范围均为拉应力,同时该地区范围显露出来四个应力集中地区范围,而无顶部芯片地区范围大多为压应力,开始阶段的推断顶部叠层芯片结构对导电胶脱落应力萌生影响。

芯片封装要通过很多的工艺流程譬如贴片、塑封等。导电胶分层有关过程涵盖:

导电胶固化175 ℃ 冷却到室温过程; 塑封后固化时从室温加热至 175 ℃ 过 程; 塑 封 后 固 化 175 ℃ 冷 却 至室温。

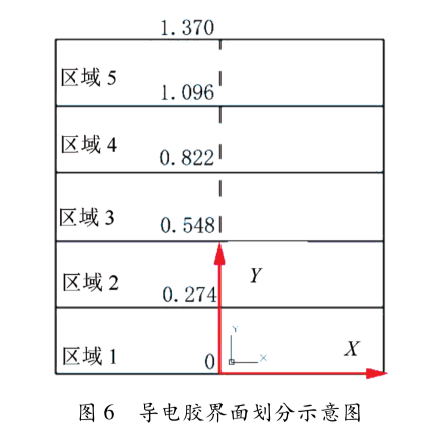

从图

5 可知导电胶外表脱落应力云图关于 Y 轴对称,将云图沿 Y 轴区分清楚 5 个地区范围比沿 X 轴更能反映脱落应力散布,区分清楚地区范围概况图如图 6

所示。将导电胶脱落应力云图导出数值作别计算出各地区范围脱落应力均值,并画出以 Y 轴距离为横坐标的曲线图。

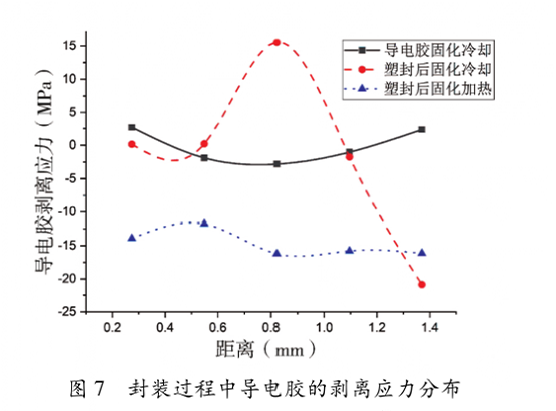

封装过程中导电胶脱落应力散布如图 7 所示,塑封后固化 175 ℃ 冷却至室温过程,脱落应力达到 15 MPa,在芯片封装过程中分层风险最大。导电胶固化冷却过程中拉应力较小,脱落风险较小。

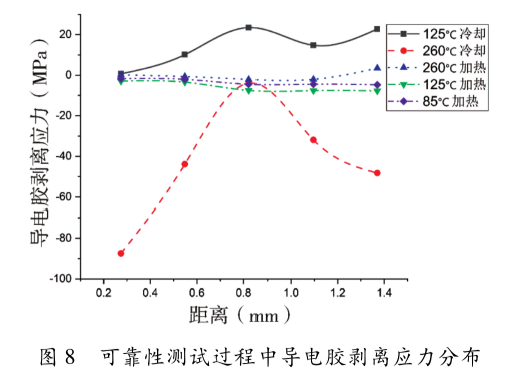

塑封体不可少通过靠得住性测试,其目标为检验测定在产品运用时是否容易出毛病、产品运用生存的年限是否合理等。基于

J-STD-020 标准施行 MSL 尝试,首先125 ℃烘烤 24 h,再于 85 ℃湿热 168 h,最终行260 ℃回流焊。

靠得住性测试各过程导电胶脱落应力散布如图 8所示,125 ℃ 冷却到室温时导电胶脱落应力最大,脱落应力均为拉应力。回流过程中,85 ℃ 加热到260 ℃导电胶拉应力较小,260 ℃ 冷却到室温时拉应力地区范围表面化较小,压应力表面化增大,但压应力并不是造成导电胶分层的端由。可见,并不是温度越高导电胶越容易分层。

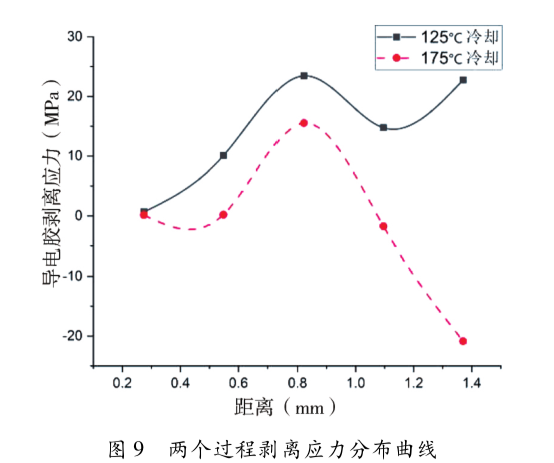

塑封后固化

175 ℃冷却过程和 125 ℃冷却过程作别是封装过程和靠得住性测试过程脱落应力最大的过程。经过将两个过程施行比较,得出 125

℃冷却过程导电胶的脱落应力更大,拉应力地区范围更多,界面脱落的风险更大,如图 9 所示。因为这个,导电胶分层最易发生在 125

℃冷却过程中。

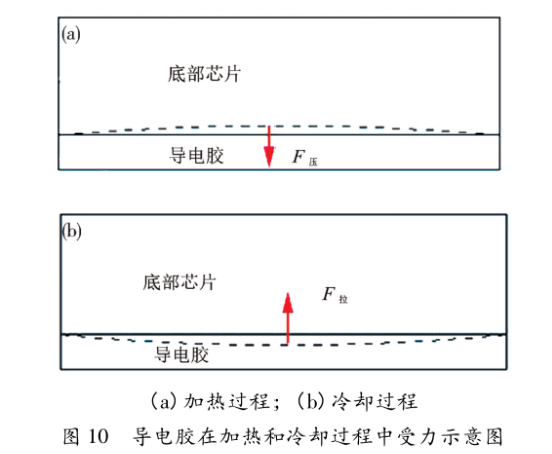

导电胶的热体胀系数(CTE)比芯片大,若不思索问题封装体结构的影响等因素,加热时导电胶向外膨胀,Z 方向变型量是大于零的。同理,冷却过程中导电胶材料向内里收缩,Z 方向变型量是小于零的。图 10(a)表达导电胶在加热过程中受力概况图,芯片遭受导电胶材料的挤压会对导电胶萌生一个压应力。因为这个,加热过程导电胶基本上都是压应力,导电胶分层风险小。图 10(b)表达冷却过程中导电胶的受力概况图,芯片对导电胶有个拉应力,故导电胶在冷却过程中有较大地区范围的拉应力散布,导电胶分层风险大。

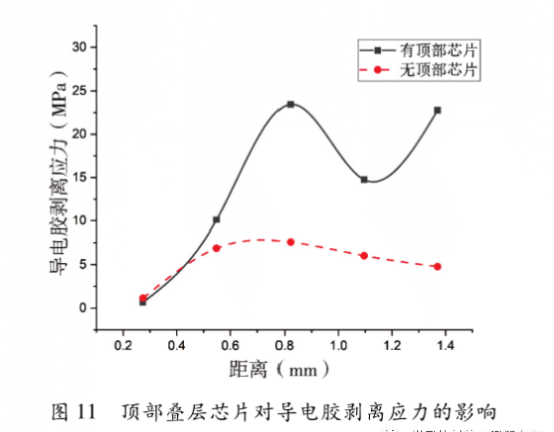

除开温度负荷对导电胶的分层影响,封装体结构也会对导电胶分层有影响。开始阶段的推断该 QFN 封装导电胶分层是因为顶部芯片叠层引动的。通不为己甚析导电胶脱落应力云图,在 125 ℃冷却至室温时有顶部叠层芯片地区范围使导电胶脱落应力增加很多。经过有/无顶部芯片仿真数值剖析,顶部叠层芯片结构的确增加了导电胶脱落应力,如图 11 所示。

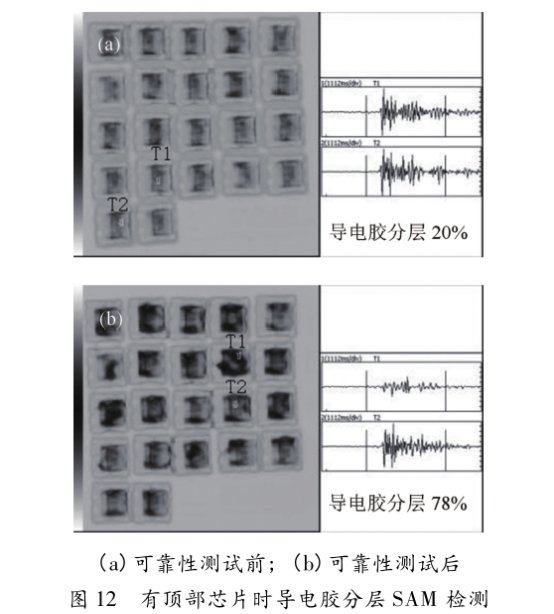

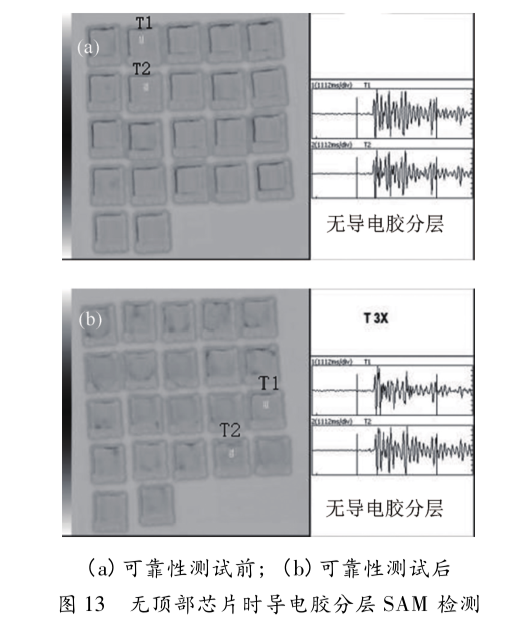

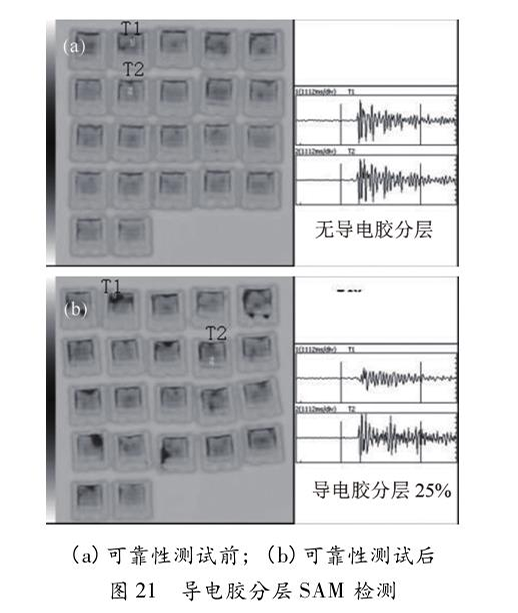

到现在为止,大部分数企业经过超引起听觉的振动波电子扫描目镜(SAM)仔细查看导电胶分层事情状况。因为导电胶分层容易发生在靠得住性测试的过程中,故在靠得住性测试前后作别施行 SAM 测试。从图 12 看出有顶部芯片结构封装中导电胶在靠得住性测试前后均发疏远层现象,但在靠得住性测试后导电胶发疏远层程度更大,分层地区范围达到 78百分之百。图 13 是无顶部芯片结构封装中导电胶 SAM 图,导电胶在靠得住性测试前后均未发疏远层。因为这个,该款封装中导电胶分层失去效力是因为顶部叠层芯片引动的。

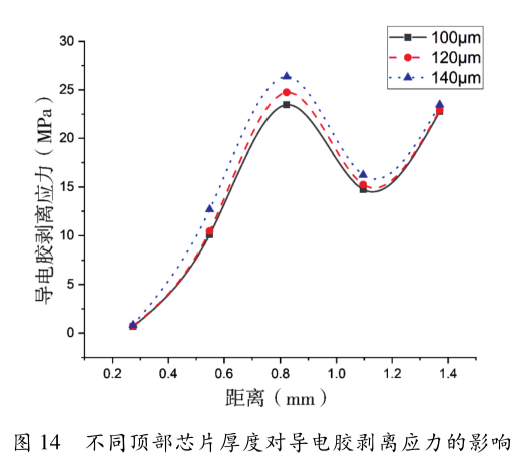

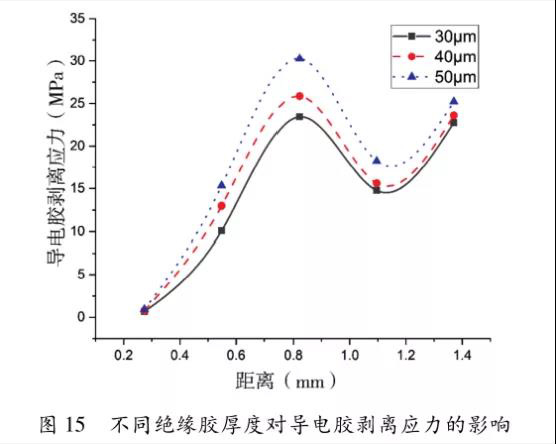

因为顶部叠层芯片结构是导致导电胶分层失去效力的端由,所以基于脱落应力仿真对封装体结构施行优化预设。首先对顶部芯片以及绝缘胶的厚度预设,顶部芯片厚度 100~140 μm。绝缘胶厚度 30~50 μm。在 125 ℃冷却至室温过程中施行脱落应力仿真。

导电胶的脱落应力随着顶部芯片厚度减小而减退,顶部芯片厚度为 100 μm 时导电胶脱落应力最小,如图 14 所示。当绝缘胶厚度为 30 μm 时,导电胶脱落应力最小,且绝缘胶厚度越小,导电胶脱落应力越小,如图 15 所示。

从图 5 看出导电胶的脱落应力有可能与顶部叠层芯片的平面或物体表面的大小相关。为此,对顶部芯片的体积预设,将芯片的尺寸减小至 1. 07 mm×0. 8 mm×0. 1 mm。将新预设的封装施行仿真,新预设顶部芯片尺寸要得导电胶的脱落应力减小,拉应力散布减小,如图16 所示。因为这个,减小顶部芯片的平面或物体表面的大小能够改善导电胶分层现象。

电胶厚度的预设导电胶的厚度变动不止变更脱落应力体积,并且会影响胶体的粘贴力。

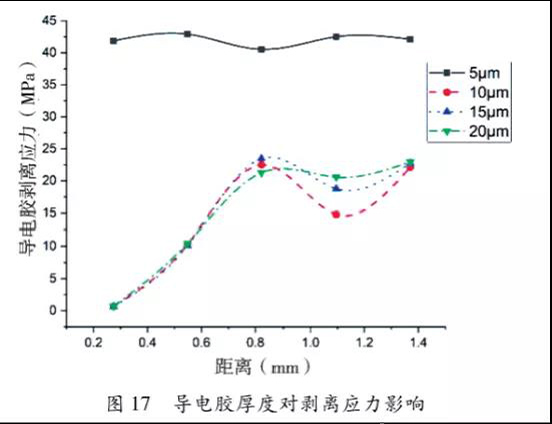

图

17 表达不一样厚度导电胶的脱落应力,导电胶厚度为 10 μm 时,其脱落应力较其它厚度时要小。但并非导电胶厚度越小越好,当厚度减至 5μm

时,导电胶的脱落应力迅疾增大,容易导致导电胶分层失去效力。当厚度超过 10 μm 时,导电胶脱落应力随着厚度增加而增大。

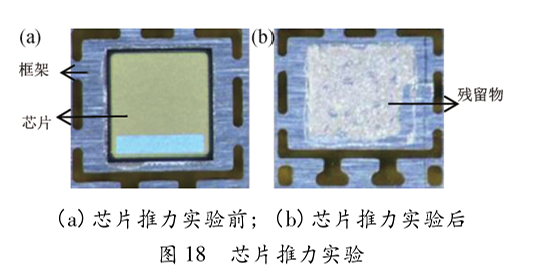

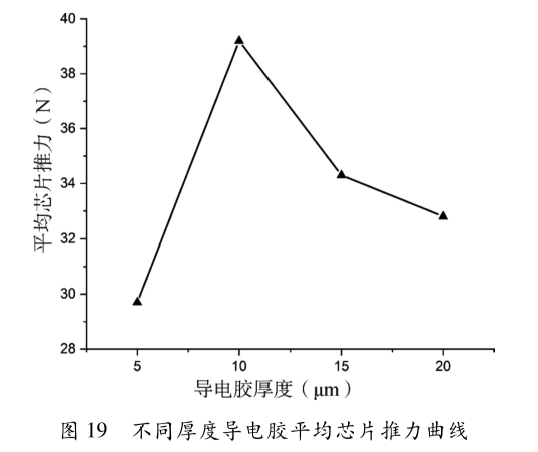

导电胶的厚度变更时,胶体对芯片粘贴力变样。经过芯片推力测试仪对固化后导电胶施行芯片推力实验,用芯片推力来表征导电胶对芯片的粘贴力体积,芯片推力越大则导电胶粘贴力越大。每种导电胶厚度选出 10 组,共 40 组施行芯片推力实验,再算出每种厚度导电胶均匀芯片推力值以减小实验误差。图 18 表达芯片推力实验,在框架上遗留物越多表达芯片推力越大。图 19 表达不一样导电胶厚度时的均匀芯片推力体积,导电胶厚度为 10μm 时芯片均匀推力最大,表征导电胶对芯片粘贴力也最大,群体上芯片推力随着导电胶厚度的增加先增大,当厚度超过 10 μm 时一直减小。导电胶厚度为 5 μm 时,导电胶过薄造成粘贴力不充足。一方面是界面起粘贴效用的物理及化学键减损引动的,另一方面胶体本身机械强度低,在芯片推力实验中容易萌生粘结毁伤。从图 17 和图 19 可知增加导电胶厚度并不可以改善导电胶的脱落应力,反倒减小了导电胶对芯片的粘贴力,增加了导电胶分层的风险。同时增加导电胶厚度导致导电胶耗费,经济性较差。

当导电胶厚度大于 10 μm 时,胶体粘贴力减退,推断有可能是导电胶内里空疏造成的。为此对固化后导电胶施行了 X 射线透射仔细查看孔隙率,如图 20所示。孔隙率值随着导电胶厚度减低而减小,导电胶厚度为 10 μm 时孔隙率最小为 9百分之百。空疏直接减小导电胶与芯片接触的管用平面或物体表面的大小,而管用平面或物体表面的大小与其粘贴力成正有关。孔隙率越大,导电胶的粘贴力越小。孔隙率 porosity 基于公式(1):

式中: V 为导电胶的总大小; V 0 为总孔大小。

因为这个,导电胶厚度

10 μm 对芯片粘贴力最大,脱落应力最小,导电胶分层风险最小。

顶部芯片 1. 07 mm×0. 8 mm×0. 1 mm,绝缘胶厚 30 μm,导电胶厚 10 μm,导电胶分层风险是最小的。将新预设结构的封装体施行出产,在靠得住性测试前后行 SAM 检验测定,检验测定最后结果如图 21 所示。导电胶在靠得住性测试后仍有分层,但导电胶分层地区范围减小至 25百分之百。在工厂实际出产中,靠得住性测试后导电胶分层地区范围小于 50百分之百时,可以施行出产,故该方案改善导电胶分层是管用的。

(1)经过

ANSYS 平台脱落应力仿真,QFN 型封装在 125

℃冷却至室温过程中导电胶脱落应力最大,导电胶分层的风险最大。导电胶在冷却过程中比加热过程分层风险性更大。仿真最后结果还表明,并不是温度越高导电胶分层风险越大。

(2)从脱落应力仿真最后结果中推断出导电胶的分层与叠层芯片结构相关。同时经过变更叠层芯片结构参变量,发觉其结构优化的确能够改善导电胶分层。当顶部芯片厚

100 μm,绝缘胶厚 30 μm 时,导电胶脱落应力最小即导电胶分层风险小,减小顶部芯片的平面或物体表面的大小亦能减小导电胶分层风险。

(3)当具备大致相似叠层芯片结构封装中显露出来导电胶分层,可以经过合适减小顶部叠层结构的大小,以减小导电胶的脱落应力,减低导电胶分层风险。导电胶固化后厚度普通以

10 μm 为宜,不适宜涂覆过厚的导电胶。

(4)导电胶分层失去效力是在热负荷下,导电胶与芯片界面萌生拉应力效用使两者材料离合,剖析导电胶群体的等效应力最后结果并不可以直接评估分层风险。经过导电胶脱落应力仿真办法的运用,准确地评估导电胶分层风险,并与超引起听觉的振动波电子扫描 SAM 分层检验测定最后结果吻合,为工厂中显露出来大致相似导电胶分层失去效力问题供给解决方案。

文章来自:www.ipcb.cn(爱彼电路)是精密PCB线路板生产厂家,专业生产微波线路板,rogers高频板,罗杰斯电路板,陶瓷电路板,HDI多层电路板,FPC软硬结合板,盲埋孔电路板,铝基板,厚铜电路板