众所周知,随着5G的商业化演进,射频前端模块的设计越来越复杂,越来越多的不同工艺的裸片将集成到一个封装模块中,集成化小型化的需求导致设计的流程越来越复杂,并且需要满足的指标越来越多,要求越来越高。而激烈的竞争环境导致设计工程师需要加速每一个设计环节从而实现产品的快速迭代与上市。这就导致了无论从电路仿真还是物理设计上,都对EDA工具提出了更高的要求。

就RF前端模块封装物理设计来讲,目前国内流行的设计流程已经不能满足这样的需求。而作为一名射频前端模块设计工程师,需要应付不同的工艺设计标准,采用不同的供应商作为不同工艺以及不同封装基板的生产加工。但由于现有EDA工具某些功能的不完备以及缺失,尤其是关于封装基板的设计,不同于IC的设计标准,封装厂或者基板厂不会提供相应的与EDA工具对标的DRC文件作为设计工程师检验的标准。设计工程师需要根据封装厂或者基板厂商提供的相关规则自己通过写一些脚本甚至肉眼检查是否合规。这就大大加大了出错的概率,从而需要与基板厂商尤其是封装厂商进行来来回回的沟通反复修改迭代,极大的延后了投板时间,延长了设计周期,降低了设计效率。

同时,对于传统的RF封装设计工具来讲,一些关于封装、裸片、SMD的footprint及相关的边框文字等,以及一些用户定义的VIA尺寸与形式,大多数需要工程师通过脚本以及手动去描画。这也极大地降低了工程师的设计效率,延迟了投板时间。

综上所述,我将为大家带来RF设计攻略第一期内容——“如何提高RF前端模块封装设计的迭代效率”线上培训。从射频前端模块的物理设计出发,结合应用实例分享,希望给大家带来不一样的设计体验,也希望各位有经验的设计同仁提出你们的宝贵意见。

为了能使更多的设计同仁参与到培训内容,本系列培训将采用线上直播的形式,通过手机端和电脑端的方式与大家进行交流互动。

讲到这里可能有的工程师会问到,如果只有射频前端封装的物理设计而没有仿真,我们也无法检验设计是否能满足我们的要求。因此,我们将在下一期培训中着重介绍整个RF设计流程,从物理设计到合规检查,从电磁场热场仿真到电路仿真。同时还可以实现从芯片、封装到PCB电路板的协同设计与仿真。具体内容请见日后通知。

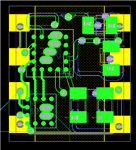

“RF设计攻略第一期:如何提高RF前端模块封装设计的迭代效率”线上培训中的实例演示部分将采用Cadence Allegro® SiP工具。作为Allegro在封装设计端的产品,SiP工具延续了Allegro本身的设计布局风格,包括各种自动化footprint生成、自动化布局布线以及规则检查的功能。这些功能在满足封装用户本身对设计全面化、自动化等需求的基础上,更加入了各种定制化的RF器件布局与设计,从各个方面满足了RF前端模块设计工程师的多重物理设计需求。