当前电子设备正朝着高频化(毫米波、太赫兹)、微型化、高可靠三大方向突破 ——5G 基站需要低损耗的毫米波模块,航空航天雷达需要抗恶劣环境的高频电路,这些需求都对封装工艺提出了严苛要求。

而 LTCC(低温共烧陶瓷)与 HTCC(高温共烧陶瓷)作为两种主流多层陶瓷封装技术,始终是高频领域的 “核心备选方案”:前者以低损耗、高集成度适配高频信号传输,后者以高热导、耐高温支撑极端场景。但如何根据具体需求选择?两者在工艺、性能、成本上的差异究竟如何?

本文将从技术原理、工艺流程切入,通过多维度对比明确两者核心差异,再结合高频领域实际应用场景,给出清晰的工艺选型逻辑,助力解决封装方案的 “选择难题”。

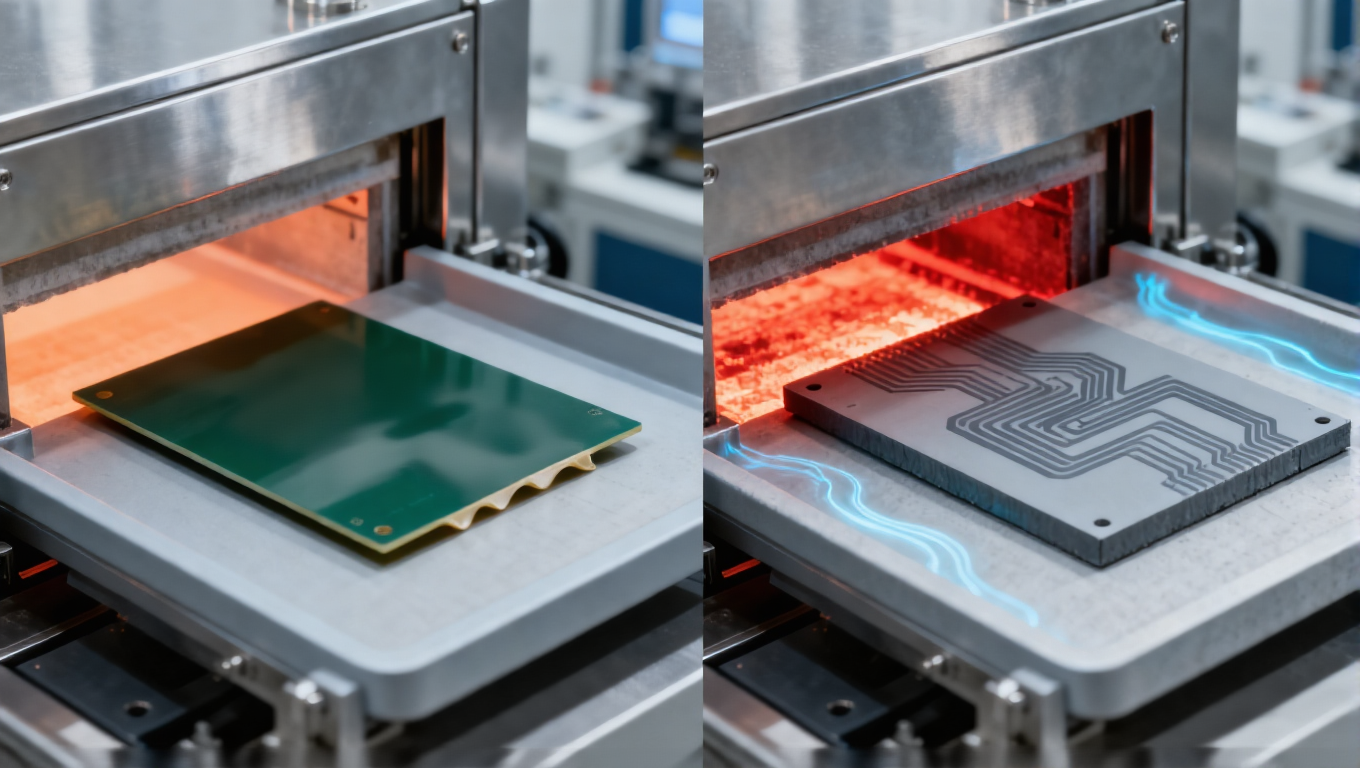

要理解两者的差异,需先明确其技术本质 —— 同为多层陶瓷封装,但 “烧结温度” 的不同,决定了材料选择、工艺路线与性能偏向的根本区别。

LTCC 技术通过在陶瓷材料中添加玻璃质助熔剂,将烧结温度降至 850°C~900°C(远低于陶瓷本身的烧结温度),实现 “陶瓷基板 + 高电导率金属(银、金、铜)” 的一次性共烧,最终形成多层三维电路结构。

其关键优势源于 “低温特性”:无需使用耐高温但低导电的金属(如钨、钼),可直接搭配银、金等高频损耗极低的导体,同时支持埋置电阻、电容、电感等无源元件,大幅提升高频电路集成度。

1. 生瓷带制备:将陶瓷粉末(如氧化铝、氮化铝)、玻璃助熔剂与有机粘结剂混合,通过流延工艺制成厚度 50~200μm 的柔性薄片,作为电路基底;

2. 微通孔加工:用激光或机械钻孔技术,在生瓷带上钻出直径 50~100μm 的微通孔(Via),用于层间电路互连;

3. 填孔与导体印刷:通过丝网印刷将银 / 金导电浆料填入通孔,同时在生瓷带表面印刷电路走线、电极图形(线宽 / 线距可做到 50μm 以下);

4. 叠层与压合:按电路设计顺序将印刷好的生瓷带对齐叠放,在 10~30MPa 压力、60~80°C 温度下热压,使各层紧密结合成整体坯体;

5. 低温共烧:将坯体放入烧结炉,按 “排胶(去除有机粘结剂)→烧结(850~900°C 致密化)→降温” 曲线处理,最终形成坚硬的多层陶瓷基板;

6. 后处理与组装:对基板表面电镀镍金(增强可焊性与抗氧化性),再通过 SMT(表面贴装技术)组装芯片、SMD 器件,完成高频模块制造。

HTCC 技术无需添加玻璃助熔剂,依赖陶瓷材料(如高纯氧化铝、氮化硅)本身的高温烧结特性,在 1600°C~1800°C 下完成烧结。由于烧结温度极高,仅能搭配高熔点金属(钨、钼、锰) 作为导体 —— 这类金属虽能耐受高温,但电导率仅为银的 1/5~1/3,高频信号损耗相对较大。

其核心价值在于 “高热导与高稳定性”:陶瓷基板纯度高(氧化铝含量常达 95% 以上),热导率可达 15~20W/mK(是 LTCC 的 2~3 倍),同时耐高温、抗辐射,适合承载大功率高频器件的散热需求。

HTCC 流程与 LTCC 类似,但因 “高温烧结” 特性,存在 3 处核心差异:

1. 生瓷带成分:无玻璃助熔剂,以高纯陶瓷粉末(如 99% 氧化铝)为主,坯体硬度更高、脆性更大;

2. 导体材料:使用钨、钼等金属浆料,印刷后需在惰性气体(如氮气)保护下烧结,避免金属氧化;

3. 烧结温度:核心烧结阶段温度达 1600~1800°C,烧结时间更长(通常 10~15 小时),能耗与工艺控制难度更高。

高频领域选择封装工艺时,介电损耗、布线精度、高频适配性是核心考量因素。以下从 8 个维度展开对比,重点标注高频相关特性:

— — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — —

| 对比维度 | LTCC(低温共烧陶瓷) | HTCC(高温共烧陶瓷) |

— — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — —

| 烧结温度 | 850°C~900°C,能耗低、工艺易控制 | 1600°C~1800°C,能耗高、需专业高温炉 |

| 导体材料 | 银、金、铜(电导率高,σ 银≈6.3×10⁷S/m) | 钨、钼、锰(电导率低,σ 钨≈1.8×10⁷S/m) |

| 介电损耗(高频)| 极低(10GHz 下 tanδ≈0.002),高频信号衰减小 | 较高(10GHz 下 tanδ≈0.008~0.01),高频损耗明显 |

| 布线精度 | 高(线宽 / 线距≥50μm),支持精细高频电路 | 较低(线宽 / 线距≥100μm),精细布线难度大 |

| 热导率 | 中(2~7W/mK),适合中低功率高频器件 | 高(15~20W/mK),适合大功率高频器件散热 |

| 高频适配性 | 优秀(适配毫米波、太赫兹,支持 AiP、FEM 等高频模块) | 一般(仅适配微波中低频段,高频损耗限制应用) |

| 成本 | 中等(材料成本高,但能耗、工艺成本低) | 较高(高温能耗 + 钨钼材料贵,整体成本比 LTCC 高 30%~50%) |

| 可靠性 | 高(耐温 - 55°C~125°C,抗振动) | 极高(耐温 - 65°C~250°C,抗辐射、抗冲击,适合极端环境) |

— — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — — —

结合上述对比,不同高频应用场景的 “工艺偏好” 清晰可见 —— 核心是平衡 “高频性能需求” 与 “环境 / 功率约束”,以下为 3 大典型场景的选择建议:

5G 基站的Massive MIMO 天线(大规模多输入多输出) 、毫米波前端模块(FEM)、天线内置封装(AiP),以及 6G 的太赫兹通信组件,核心需求是 “低损耗 + 高集成”:

• 毫米波信号(24~77GHz)对损耗极敏感,LTCC 的低介电损耗(tanδ≈0.002)可将信号衰减控制在 5% 以内,远优于 HTCC;

• 基站与终端设备要求小型化,LTCC 支持埋置无源元件(如电感、滤波器),可将模块体积缩小 30%~50%,而 HTCC 布线精度低,难以满足微型化需求。

典型应用:华为 5G 基站毫米波模块、苹果 iPhone 毫米波天线封装均采用 LTCC 工艺。

航空航天领域的高频需求分两类,需针对性选择:

1. 机载雷达(如相控阵雷达):工作频率多为 X 波段(8~12GHz),同时需耐受 - 55°C~85°C 温度循环,LTCC 的低损耗 + 轻量化特性更适配,可减少雷达模块重量(航空设备对重量敏感);

2. 卫星通信 / 导弹制导:需在太空辐射、高温(150°C 以上)环境下工作,且部分大功率雷达需散热支持,此时 HTCC 的 “抗辐射 + 高热导” 优势凸显 —— 例如北斗卫星的高频信号处理模块,就采用 HTCC 封装以确保极端环境下的可靠性。

部分高频场景同时伴随大功率(如射频功率放大器、高频加热设备),需兼顾 “高频传输” 与 “散热”:

• 若功率密度≤5W/cm²(如小型射频模块),LTCC 的热导率(2~7W/mK)可满足散热,优先选 LTCC 以降低损耗;

• 若功率密度>5W/cm²(如大功率雷达发射模块),HTCC 的高热导(15~20W/mK)能快速导出热量,避免器件过热失效 —— 此时需接受 HTCC 的高频损耗,通过电路设计(如缩短传输路径)弥补,或采用 “HTCC 基板 + LTCC 表层电路” 的混合方案。

为更好适配高频领域需求,两者均在针对性优化,未来技术突破将聚焦 3 个方向:

• 材料创新:开发无玻璃相的 LTCC 陶瓷(如氮化铝基 LTCC),将热导率提升至 15W/mK 以上,同时保持介电损耗≤0.0015,兼顾高频与散热;

• 工艺精细化:推动布线精度向 20μm 以下突破,支持更复杂的高频电路集成,适配 6G 太赫兹场景。

• 导体材料改良:研发 “钨 - 银复合浆料”,在保持耐高温特性的同时,将电导率提升 20%~30%,降低高频损耗;

• 低温化尝试:通过添加少量纳米级助熔剂,将 HTCC 烧结温度降至 1200°C~1300°C,可兼容铜导体(电导率高于钨),改善高频性能。

未来高频封装将不再是 “二选一”,而是 “优势结合”—— 例如用 HTCC 做底层基板(承担散热与结构支撑),LTCC 做表层电路(实现低损耗高频传输),形成 “高热导 + 低损耗” 的混合封装,适配大功率高频器件(如航空航天大功率雷达)。

LTCC 与 HTCC 并非 “替代关系”,而是 “互补关系”:在高频领域,LTCC 是 “常规场景的最优解”—— 以低损耗、高集成满足 5G/6G、常规雷达的需求;HTCC 是 “极端场景的必要解”—— 以高可靠、高热导支撑太空、导弹等特殊环境。

对于电子封装从业者而言,选择工艺时无需纠结 “技术优劣”,关键是明确 3 个核心问题:工作频率是否超过 10GHz?是否需要耐受极端环境?功率密度是否高于 5W/cm²? 理清这三点,就能快速锁定最适配的封装方案 —— 这也是本文对比两种技术的核心价值所在。