在芯片封装的核心战场,IC封装载板如同微观世界的摩天大楼地基,承载着万亿晶体管的互联使命。 这项融合精密机械、材料化学与光电技术的工艺,正推动着芯片集成度的极限突破。本文将揭示从硅片到系统级封装的微米级建造艺术。

一、载板工艺的本质挑战

IC封装载板的核心使命是解决三大矛盾:

1. 空间矛盾:在指甲盖面积内容纳数万信号通道

2. 物理矛盾:匹配芯片(CTE=2.6ppm/℃)与PCB(CTE=16ppm/℃)的热膨胀系数

3. 电气矛盾:在40GHz高频下保持信号损耗<0.2dB/cm

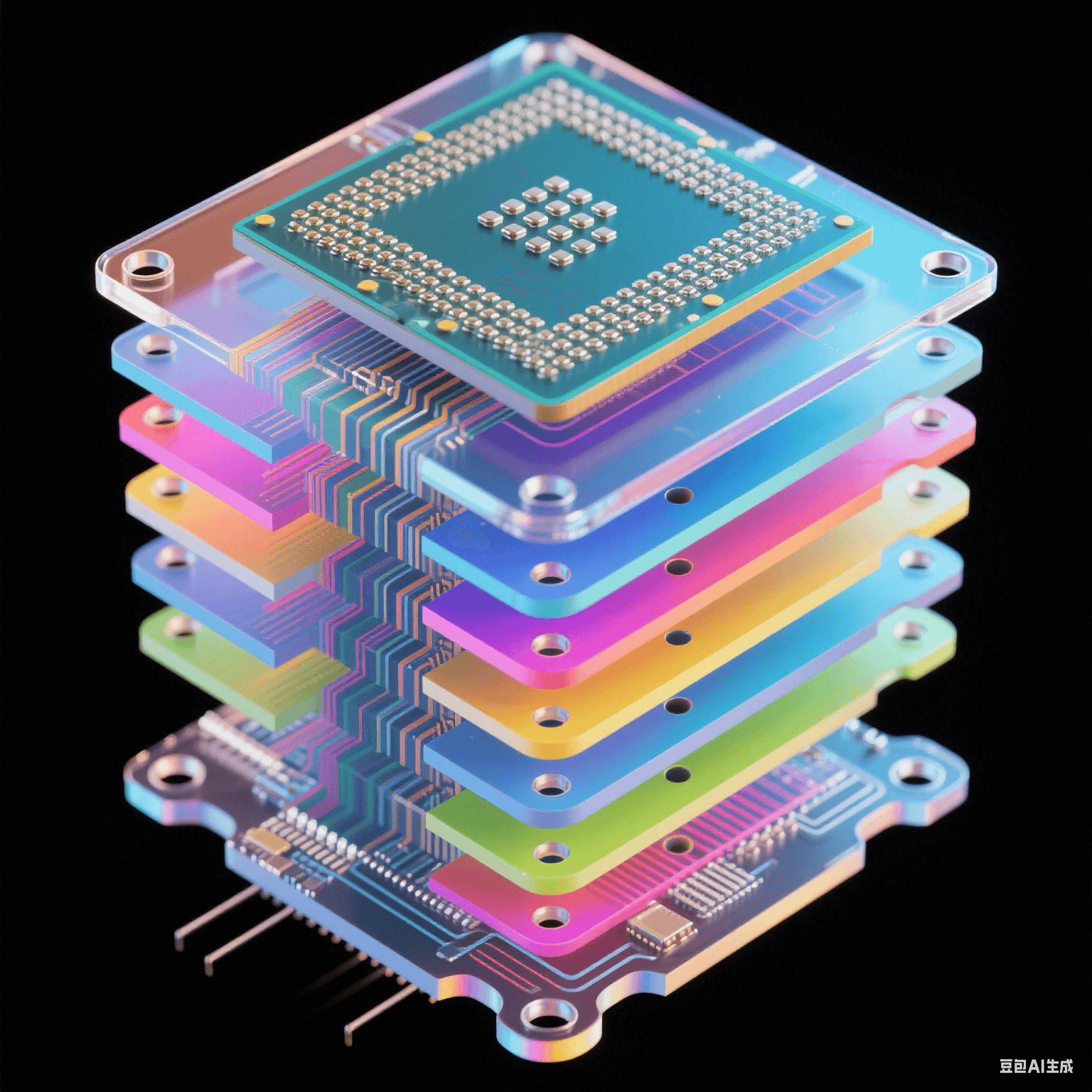

最新载板结构已演进为十层微互联体系:

芯片焊盘 → 再布线层 → 微凸块 → 核心层 → 高密度积层 → 球栅阵列

微孔金属化技术成为贯穿各层的生命线

二、十层微互联建造全流程

阶段1:芯板精密切削(精度±3μm)

- 超薄铜箔处理:压延铜减薄至3μm,表面粗糙度≤0.3μm

- 激光钻孔:紫外/CO₂复合钻头实现12μm孔径(深径比1:15)

- 关键控制:孔壁锥度<2°,防止电镀空洞

阶段2:纳米级孔金属化

流程始于等离子清洗,经纳米钯催化剂沉积后,进行化学镀铜(0.5μm)及脉冲电镀加厚至15μm。电镀液控制需保持铜离子浓度±5ppm,温度波动<0.5℃。电镀液控制需保持铜离子浓度±5ppm,温度波动<0.5℃

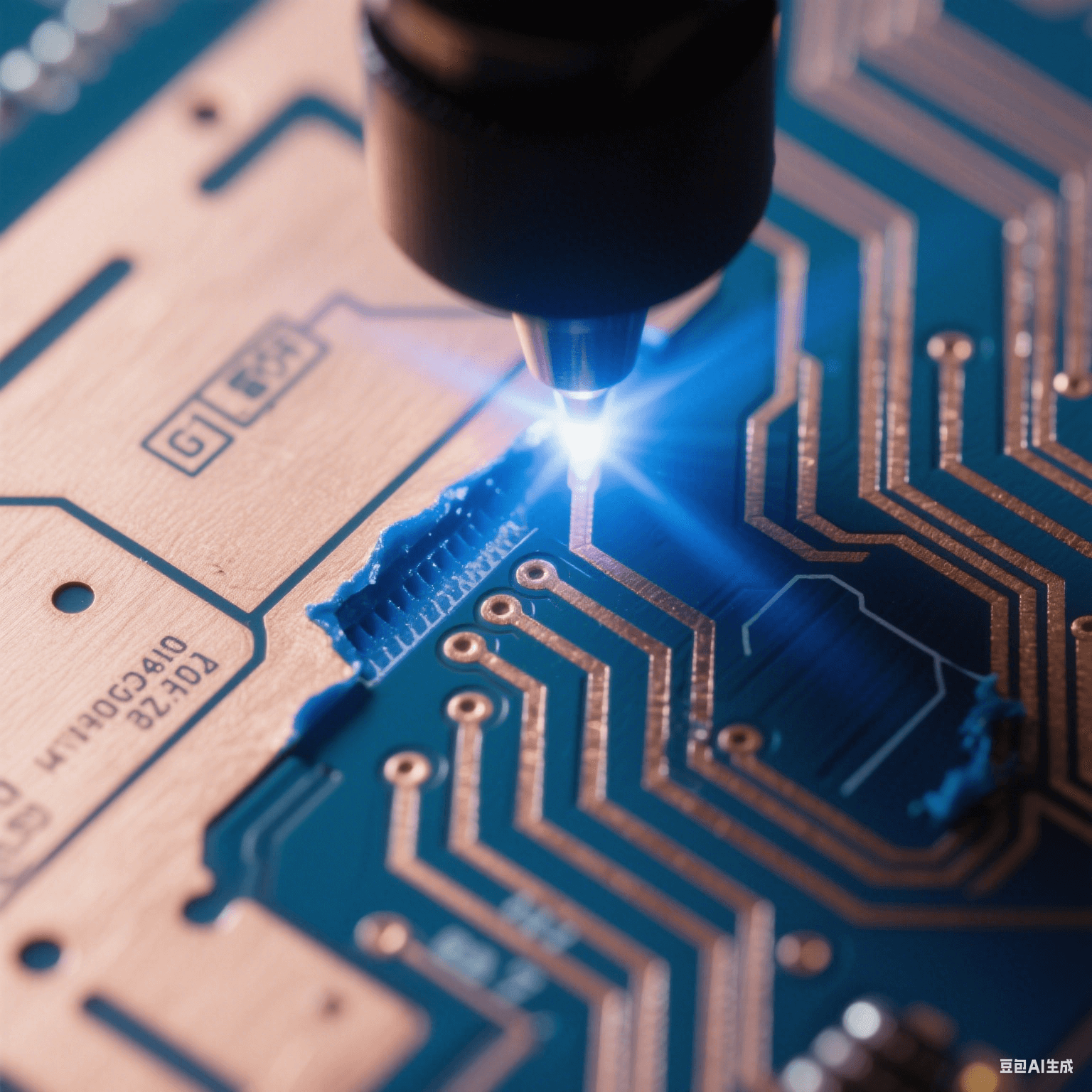

阶段3:mSAP极限图形化

1. LDI激光直写:355nm紫外激光雕刻8μm线宽

2. 微蚀刻控制:氨磺酸体系蚀刻速率2μm/min

3. 梯形结构优化:侧壁角度60°±2°保障结合力

> 对比传统工艺:

工艺 | 线宽极限 | 位置精度 |

减成法 | 30μm | ±10μm |

mSAP | 8μm | ±2μm |

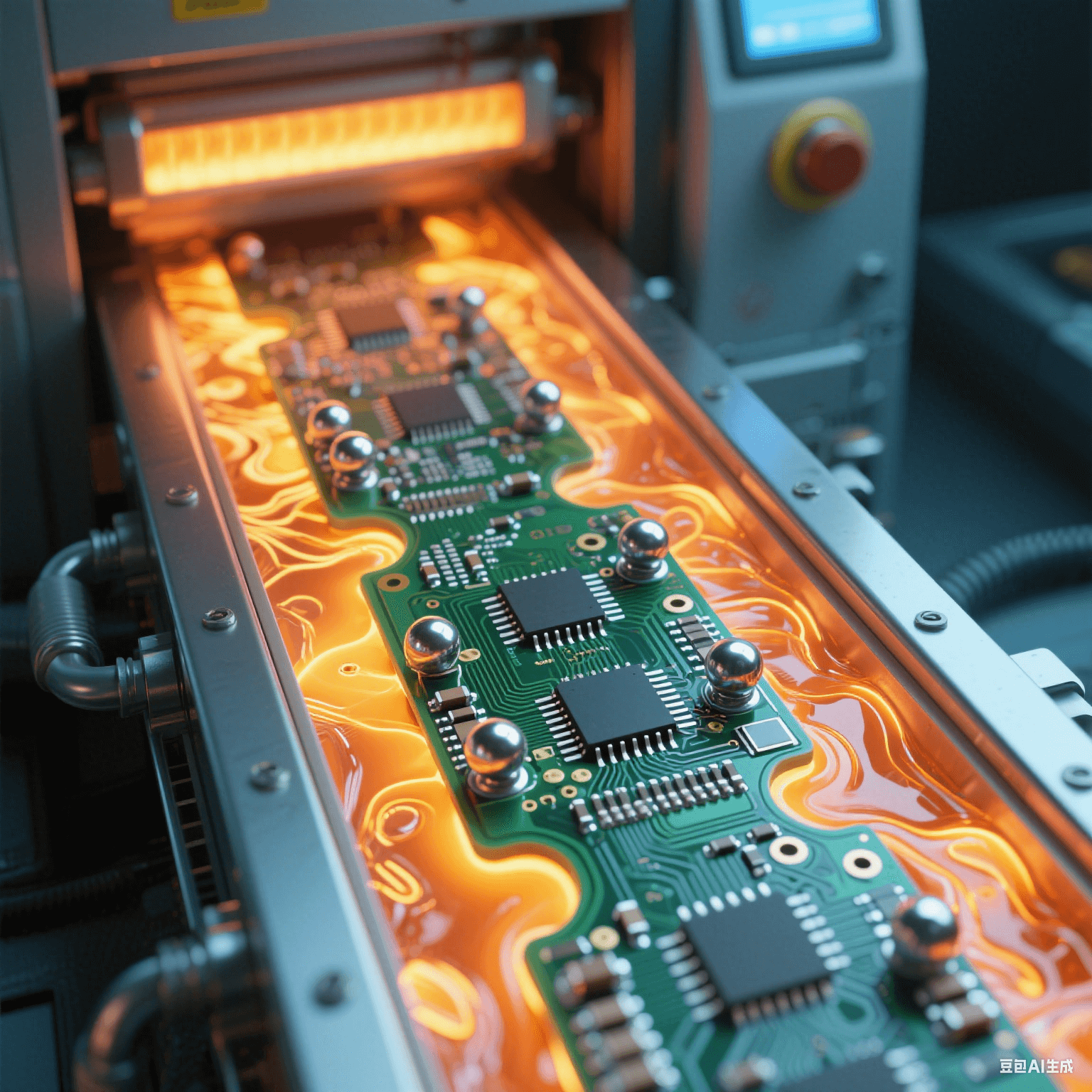

阶段4:介质层精密堆叠

ABF材料(Ajinomoto Build-up Film)压合:

真空贴膜 → 阶梯升温(80→200℃) → 高压固化(50kg/cm²)

厚度控制:每层18±1.5μm,十层堆叠平整度<15μm

阶段5:表面终极防护

ENEPIG处理(化学镍钯金):

Ni层5μm / Pd层0.05μm / Au层0.03μm

盐雾测试>96小时

三、材料科学的隐形战场

介质材料演进

世代 | 材料体系 | 介电常数 | 热膨胀系数 |

第一代 | FR-4+玻纤 | 4.5 | 16ppm/℃ |

第二代 | BT树脂 | 3.8 | 12ppm/℃ |

第三代 | ABF复合材料 | 3.2 | 8ppm/℃ |

铜柱技术突破

- 纳米孪晶铜:导电率提升15%,抗电迁移能力×3

- 梯度铜柱设计:顶部高弹性/底部高强度

四、未来工厂的智造革命

2025技术拐点

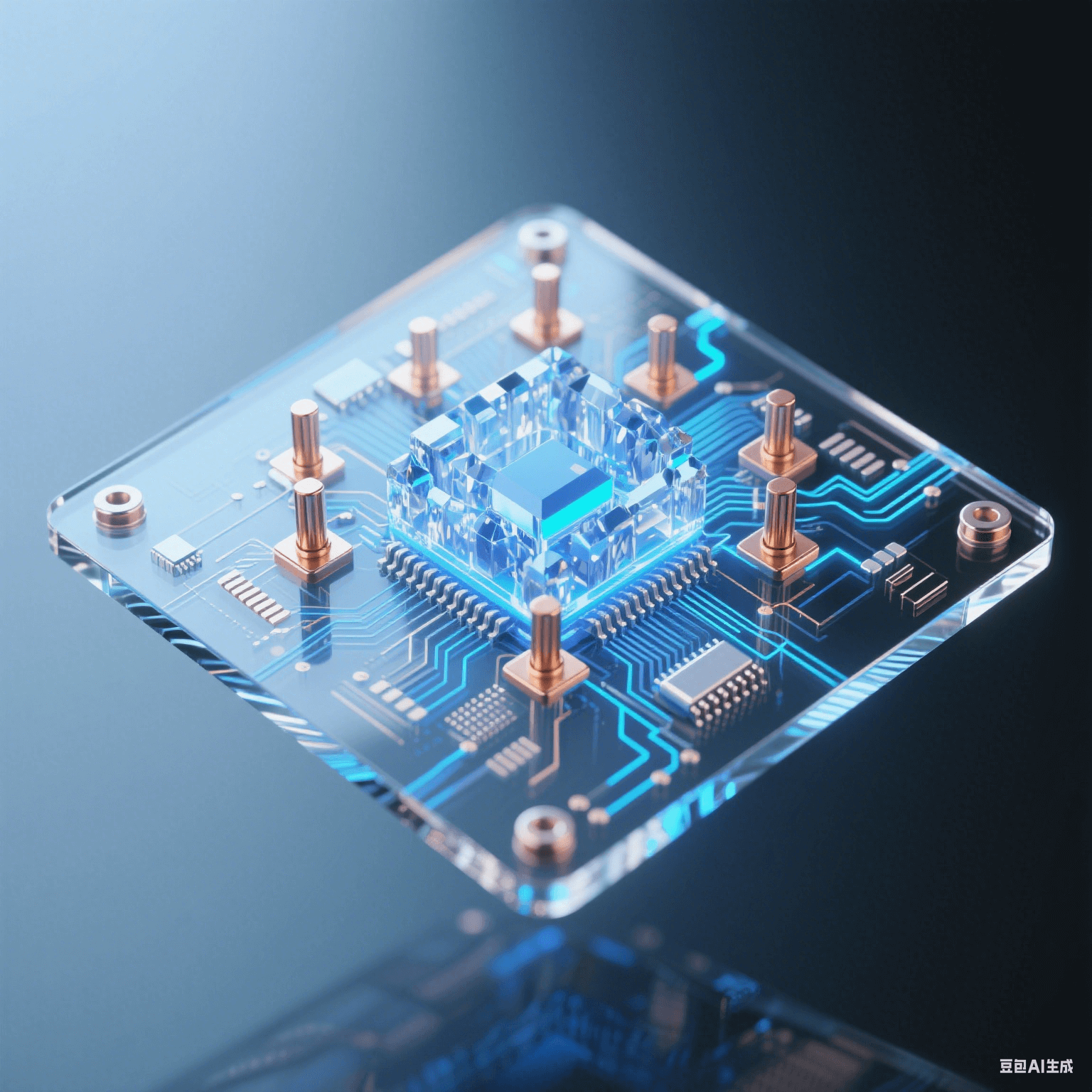

1. 玻璃基板应用

超低热膨胀(CTE=3.2ppm/℃)

实现20μm厚度十层堆叠

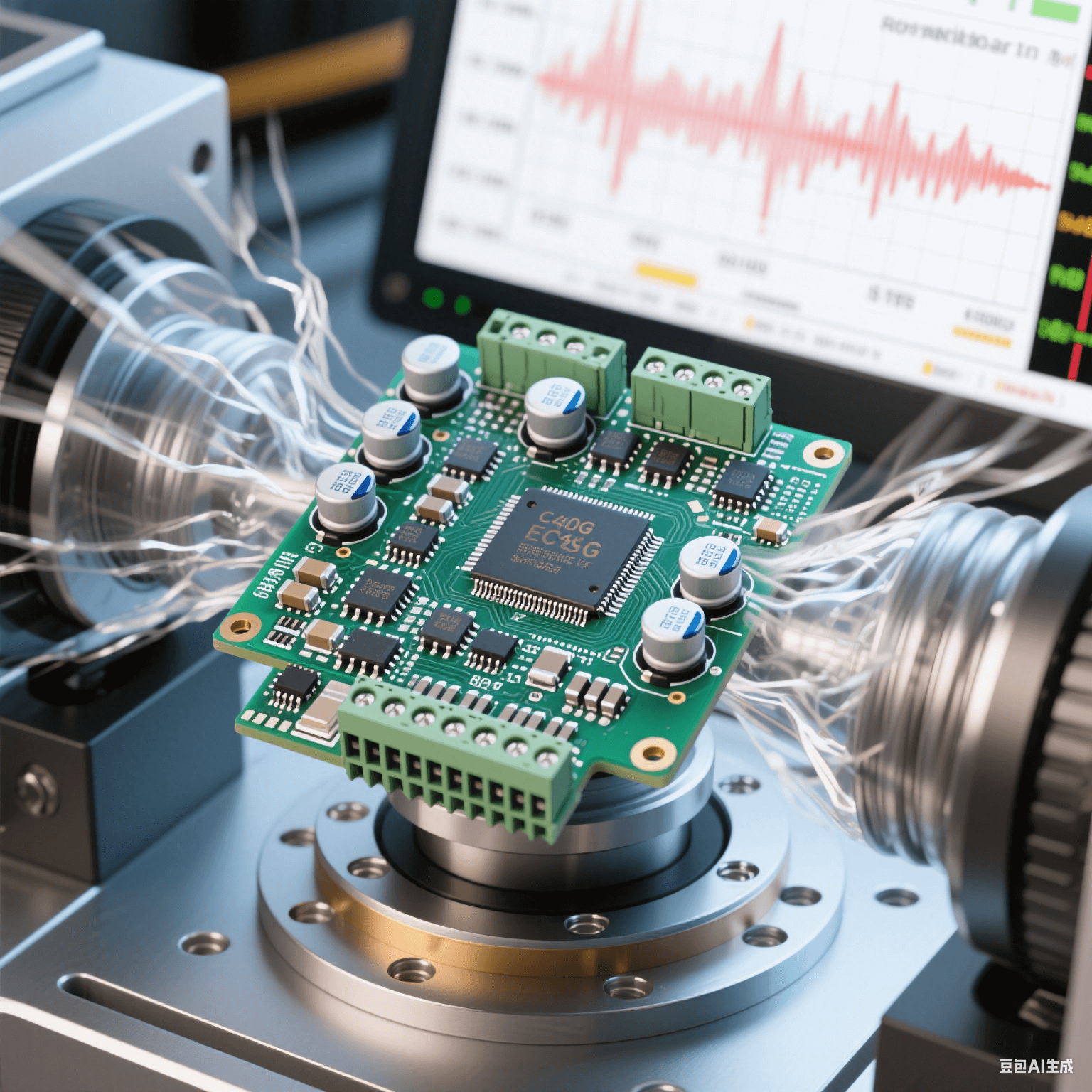

2. AI实时控制系统

电镀液离子浓度监测 → 神经网络预测沉积速率 → 自动补液系统

良率提升至99.3%(当前基准98.1%)

3. 3D打印导电结构

银纳米粒子喷射成型

异形载板制造周期缩短70%

IC封装载板制作流程是芯片效能释放的最后一道关卡。随着线宽逼近物理极限,材料创新与智能制造的融合将重构微互联技术体系。掌握十层微互联工艺不仅意味着技术领先,更代表着在算力时代的基础设施话语权。