随着ADC和DAC的性能规格、形状参数和新的传感器技术(Rx和Tx)的不断发展,RF数据转换系统正在发生快速变化。在这期间,一个系统级的设计问题一直存在,即如何平衡模拟和数字电路的设计,以实现最大的软件/系统灵活性(从传感器到数字处理单元的输入/输出)。这个基本问题需要系统设计师划分(或组合)数据转换电路器件,并结合模拟和数字信号的布线,实现多种服务的软件最大化。现在,随着高级的SiP(系统级封装)组装技术的发展,数据转换器系统的设计正逐步从硬件中心向软件中心转变。Teledyne e2v的SiP设计、发展和组装的专业技术革新了系统级设计,可实现最大的灵活性并支持多任务的应用。利用最先进的技术(倒装芯片、有机封装等)开发的RF混合信号数字处理应用可用于工业、医疗、航空电子、仪器、电信、军事和宇航等应用。Teledyne e2v在高级SiP设计和组装技术方面拥有超过40年的经验,可帮助系统设计师实现高级数据转换系统平台的最高性能和最大价值。

高频数据转换器系统需要高性能(和可靠的)半导体器件来处理整个信号链的关键功能。选择可以满足整个系统性能要求的合适的半导体器件对SiP的实现至关重要。Teledyne e2v为SiP的实现提供了高速数据转换器、微处理器、存储器以及各种模拟和逻辑功能器件。

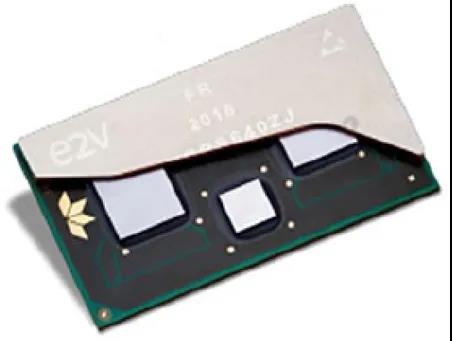

显然,数据转换接收(Rx)系统的核心器件是ADC。Teledyne e2v在过去的20多年里一直致力于数据转换器技术的创新,并提供了多通道、低噪声、低失真的微波频率ADC(如上图的EV12AQ600)。这种数据转换器使系统设计师能(通过直接RF转换)消除传统架构中下变频所需的模拟环节。利用Teledyne e2v的高端ADC减少模拟环节,并使用高级的SiP设计技术配合无需许可证的标准和定制解决方案,设计师可以研发许多标准产品和定制产品,以满足特定的性能和/或环境需求。

未来高速SiP直接RF数据转换接收(Rx)方案的核心是EV12AQ600。结合RTH120跟踪保持放大器(THA),PS620实验SiP RF前端接收板(如下图所示)的性能非常优秀(见第2页上器件的核心参数)。EV12AQ600是一款四核ADC,包含交叉点开关(CPS)前端,允许四个ADC核心同时、独立或成对地工作,支持四通道1.6Gsps,两通道3.2Gsps或单通道6.4Gsps的采样率。典型的四通道模式的SFDR(不考虑H2和H3谐波)优于70dBFS(-1dBFS输出,频率高达5980MHz)。

这款器件可提供多种级别,包括商业级、工业级、军级,最高支持耐辐射宇航级。EV12AQ600可用于多种应用,如高速数据采集、高速测试仪器、自动测试设备、地球观测SAR雷达载荷、电信MIMO卫星载荷、超宽带卫星数字接收机、C波段直接RF转换、微波软件定义无线电、点对点微波接收端、机器状态监测系统、飞行时间质谱分析、LiDAR、高能物理等。

器件核心参数 EV12AQ600 ADC: • 四个12-bit 1.6 GSps ADC核心,支持1、2或4通道时域交织• 全交织模式采样率高达6.4 GSps • 6.5 GHz输入带宽(-3dB) • 集成的宽带交叉点开关 • 支持多通道同步的同步链 RTH120 THA: • 24GHz 输入带宽• 双THA使输出保持时间超过半个采样时钟周期 • 全差分设计 |

在实现高速、最先进的SiP数据转换发射端(Tx)解决方案方面,关键的技术是EV12DD700(如图所示)。

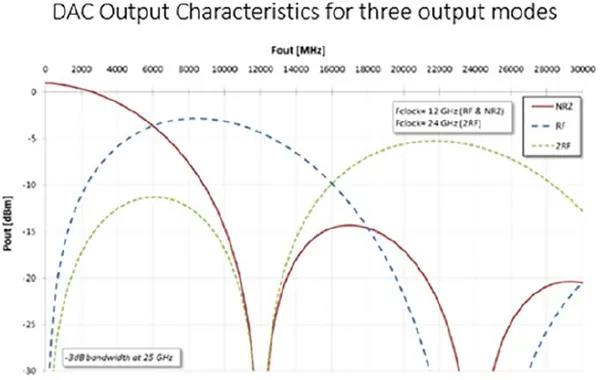

该双路12位DAC支持高达12Gsps的采样率,可直接产生高达21GHz的输出信号,满刻度阶跃响应时间低至15ps,在微波频率的噪声很低,性能优秀。EV12DD700双通道DAC也支持Ka波段工作,支持波束形成的应用。这款DAC有25GHz的3dB输出带宽,即使超过25GHz也仅有略大于3dB的衰减(见下图)。

每个DAC都集成了一系列复杂的信号处理功能,包括一个用于直接数字合成(DDS)功能的可编程anti-sinc滤波器,一个可编程的复杂混频器,以及一个包含四个插值环节的数字上变频器。数字处理功能包括:插值(4x, 8x和16x)、带有数字控制振荡器(32位NCO)的数字上变频(DUC)、直接数字合成(DDS)、数字波束形成和波束跳变。DAC的主要功能包括:可编程输出模式(NRZ, RF, 2RF)、增益调节、可编程SINC补偿功能和多器件同步。

当然,所有的高速数据转换系统也需要先进的数字处理能力。例如,Teledyne e2v已经认证并发布了一款从NXP最新的Layerscape® 系列筛选出的微处理器LS1046A,可工作在-55℃到125℃(宇航级LS1046-Spacce也很快会发布)。LS1046A是NXP的64位ARM® Layerscape产品系列的一款器件,使用四核ARM® Cortex® A72设计。

这种设计在尽可能小的封装里实现了无与伦比的性能。用户可以使用与ARM® 技术兼容的庞大的软件、应用、工具的生态系统。LS1046A是一款1.8GHz的处理器,集成了包处理加速和高速外设,使用了高性能的架构,有业内领先的计算密度。其超过45,000CoreMarks® 的计算性能(即30K DMIPS@1.8GHz),搭配双路10Gb以太网、3路PCIe Gen3和1路SATAGen3,适用于一系列高可靠性的军用、航空和航天的应用。LS1046A也集成到了Teledyne e2v最新的Qormino® 计算模块中,这个模块还包含了一个4GB的DDR4存储器(见左侧的照片)。此外,作为Teledyne e2v的半导体生命周期管理计划SLiM™的一部分,这款器件的生命周期可达15年以上,避免了常见的昂贵的器件过时问题。

在工业、医疗、飞行电子、仪器、电信、军事和宇航领域,数据转换系统正在经历快速的变化。对于所有的细分市场,首要的系统级设计问题是,如何在模拟和数字电路之间取得平衡,实现最大的软件/系统灵活性(从传感器到计算机输入或从计算机输出到传感器)。这个基本的问题要求系统设计师划分(或组合)数据转换电路器件,并结合模拟和数字信号的布线,以实现多种服务的软件最大化。

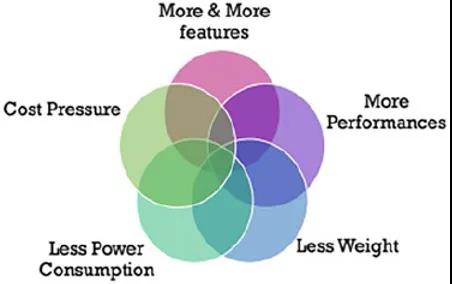

系统工程师了解他们的市场、应用和电路性能的规范需求,但设计参数,例如风险、技术选择、形状参数、开发时间表(包括时间表同步)、可靠性,以及与高性能数据转换系统相关的成本,都是高度可变的。这些设计参数,加上不断变化的系统性能规格需求,最终导致更窄的设计实现“交集”(图2)。

图2 - 不断增加的设计参数和系统级性能需求,产生了更窄的“交集”。

当然,在任何设计参数上犯错误,都会付出巨大的代价。因此,任何可以嵌入到设计开发中的灵活性,只要能为项目增加整体价值而不是降低价值,都是值得投资的。

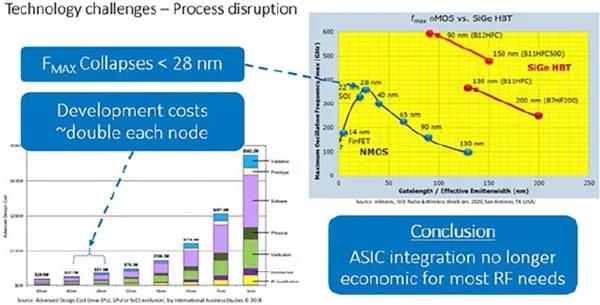

有一个设计参数可以提高设计阶段的灵活性,并最终满足必要的性能需求,特别是对于数据转换系统。它是利用SiP(系统级封装)技术实现所需的功能。过去,半导体工艺技术的不断进步使系统级设计师能够在SoC(片上系统)上实现完整的电路功能。随着门电路长度缩短至10nm甚至更小,需要大量数字计算的SoC应用已可以通过半导体技术实现。不幸的是,随着半导体特征尺寸的减小,芯片的开发成本呈指数级增长(见图3)。

图3也显示了最小几何门尺寸和最大器件振荡频率之间的相关性。如图所示,Fmax的拐点在门长度<28nm的位置。相应的,随着门长度的减小,开发成本呈指数增长(G=28nm(平均开发成本5130万美元),G=16nm(平均开发成本1.063亿美元),G=7nm(成本2.97亿美元),G=5nm(成本超过5亿美元) )。

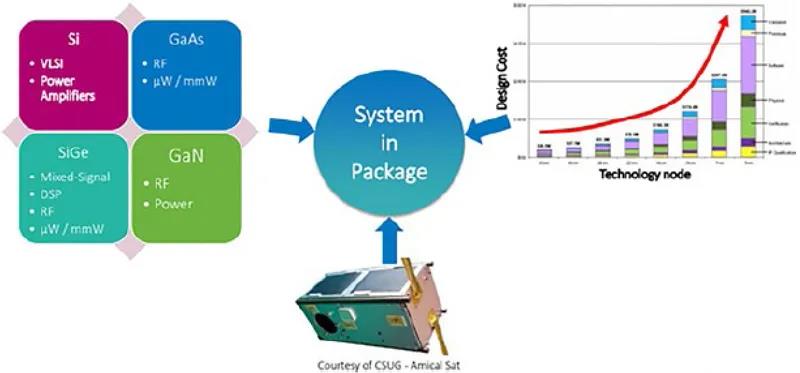

随着SoC包含更多的功能,需要使用更小的门长度,其开发的成本变得令人望而却步。例如,SoC一直是移动电话行业的驱动技术,但对模拟技术(如MEMS传感器)的需求不断增加,导致从SoC到SiP方案的变革。图4说明了当前推进从SoC到SiP的变革的三个共存的设计参数:1)技术:为最优系统性能选择最合适的工艺技术(即Si、GaAs、GaN、SiGe等),2)小型化,3)成本。

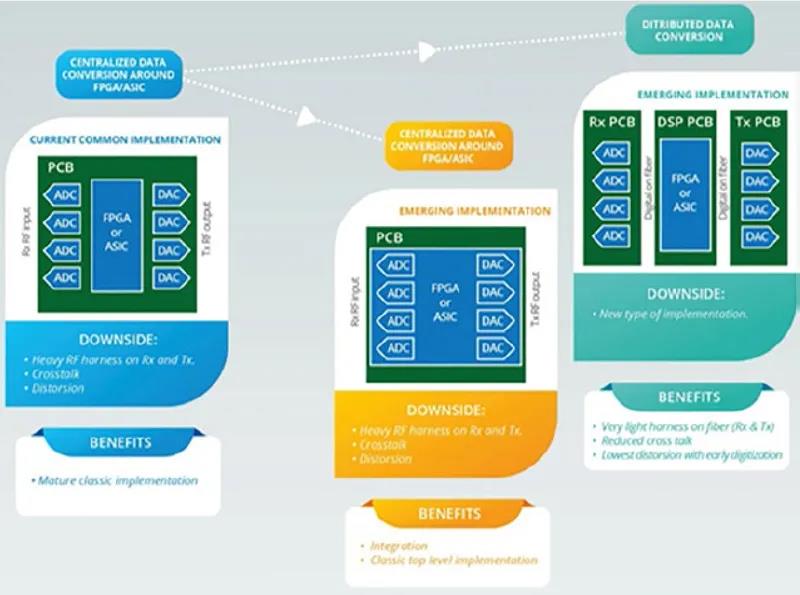

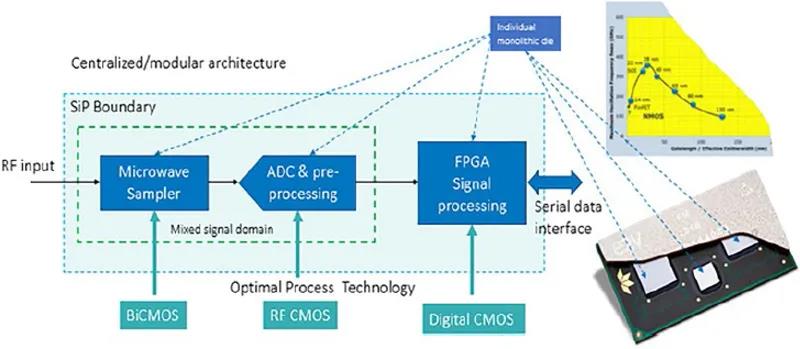

推动数据转换系统从SoC向SiP发展的另一个因素是对数据转换电路器件的划分(或组合)以及模拟和数字信号的布线,这将允许对多种服务进行最大程度的软件化。简单来说,数据转换系统可以设计为“集中式”或“分布式”系统(见图5)。集中式数据转换系统需要大量的模拟信号布线,因此会有额外的串扰和失真。相比之下,分布式数据转换系统可以将ADC放在Rx传感器上,将DAC放在Tx传感器上。数字信号可以通过轻便、紧凑的高速光纤传递。

因此,Teledyne e2v的高级的SiP设计、开发和组装的专业技术使数据转换系统的开发发生了巨大的变革,实现了多任务应用设计参数的最大灵活度(即组合和划分)。通过使用最先进的技术(焊线、倒装芯片等),组合(或划分)RF、混合信号和数字处理半导体,高级的SiP设计和组装技术能为系统设计师带来最高性能、最低成本的高频数据转换系统平台。

例如,图6的PS640是一款SiP实现的RF数据转换系统产品,目前正在研发,用于未来的L波段到Ka波段的频率接收机(1GHz至40GHz)。

PS640使用Teledyne e2v基于STMicro BiCMOS055工艺设计的新型THA和两片互相交织的EV12AQ600ADC,是一款“集中式”的高速SiP数据转换接收器(Rx)。图6也描述了其性能指标。图7描述了一种相同的数据转换系统的未来概念,这是一种“分布式”数据转换接收器的实现方式,使用光引擎(包含在SiP中)驱动数字处理器(FPGA),实现最大软件化(软件中心)。

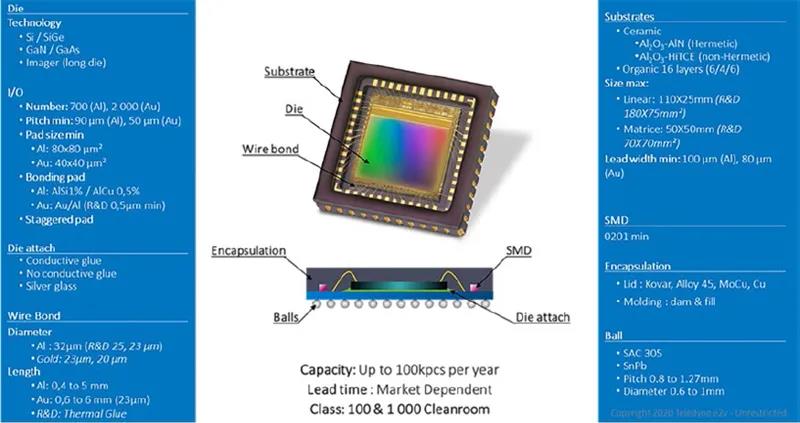

SiP是将多个器件(主动器件或被动器件)封装在一起的单个设备。SiP用于在电子系统层面执行多项功能。嵌入在SiP中的半导体器件(包括被动器件)可以水平和/或垂直堆叠在基材上,然后进行封装。半导体可以通过焊线或焊接凸点的方式与基材连接(也可以用于将裸片堆叠成垂直的结构)。

如前所述,数据转换SiP可能包含多个裸片,如前置放大器、混频器、ADC、DAC,专用处理器、存储集成电路和被动器件(如电阻和电容)。这些裸片是使用不同的安装技术固定在同一个基材上。SiP的组装技术促进了细分市场的发展,特别是与超高RF(地面和非地面)、需要MEMs电路的物联网(IOT)、移动和可穿戴设备等应用相关的领域。凭借一系列的使用SiP技术的产品和封装解决方案,Te2v为工业、医疗、航空、军事、科学和空间等应用的细分市场提供设计和组装服务。此外,Teledyne e2v的许多产品都是通过与NXP、Everspin、Micron等公司的战略合作开发的。

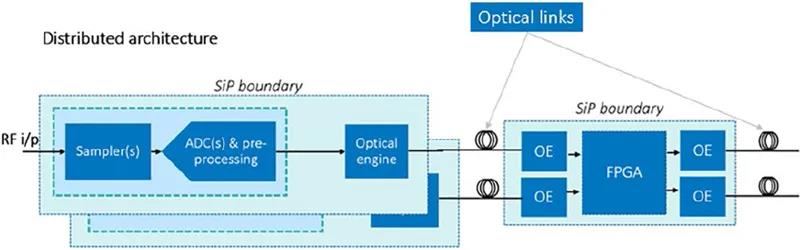

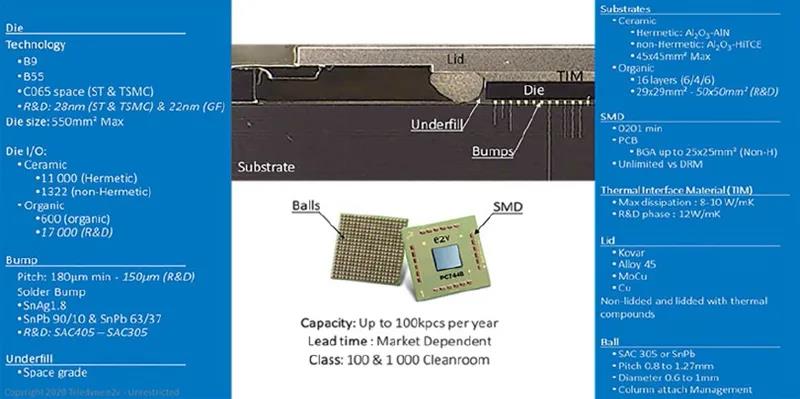

Te2v可提供一系列SiP设计开发的供应链管理服务,包括:裸片设计、封装设计、高可靠组装、高性能速度测试、质量服务和半导体生命周期管理(SLiMTM,见图8)。Te2v拥有超过40年的宇航设计经验,包括ADC、DAC、微处理器、存储器以及内部测试和质量服务,能为所有细分市场提供满足任何质量等级需求的高级SiP的产品和服务。Te2v的高级的SiP组装技术包括:焊线、倒装芯片、有机和陶瓷封装(密封和非密封)以及混合组装。

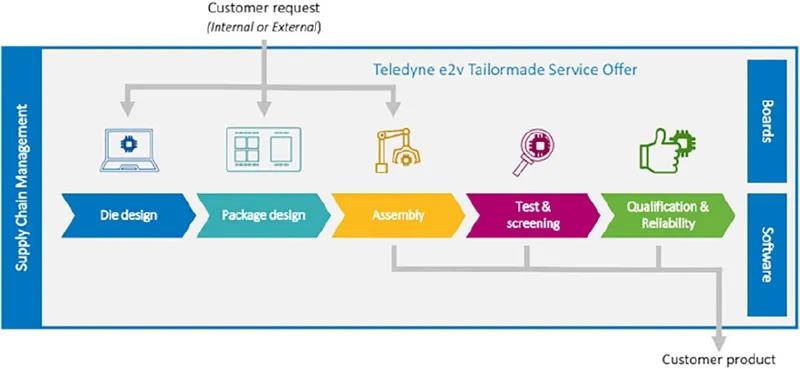

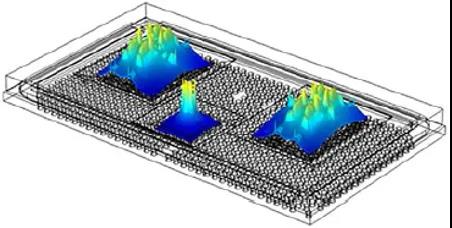

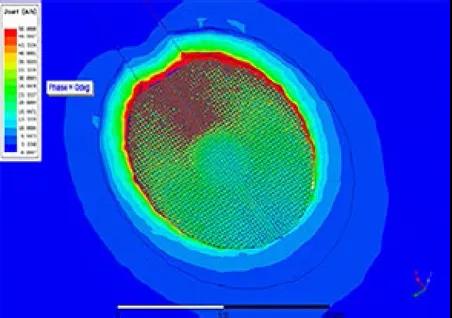

当然,在组装之前,高级高速SiP开发需要封装仿真和封装参数的测试,以评估散热和可靠性。例如,图9介绍了上文提到的PS640的热仿真。对于散热设计,将多个裸片紧密地放置在一起是一个挑战。为了准确预测器件最关键区域的结温,需要进行仔细的热仿真。Te2v使用与设计师和客户讨论商定的边界条件,使仿真的性能匹配最终的测试结果(这对于SiP集成的关键器件是必需的)。此外,Te2v使用高频3D场解算器(Ansys HFSS)对RF SiP的开发进行仿真和设计。

图9 - PS640 SiP的热仿真

HFSS是一款用于电磁结构的商业有限元方法解算器,适用于SiP封装包含的复杂RF电子电路/半导体器件、滤波器、传输线的封装设计(见图10)。

图10 - 对PS640 进行40GHz 模拟输入的3D 场解算器仿真(Ansys HFSS) 显示封装到THA 的裸片之间的连接状况,并分析了硅金属填充里的信号传递。

在这个例子里,Te2v的封装团队和负责Te2v的SiP开发流程的半导体团队共同设计了这个RF模拟前端。

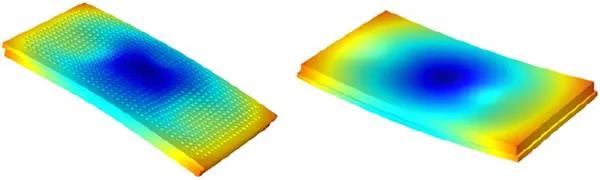

由于嵌入在单个有机基材里的硅技术有所不同,以及C4(受控塌陷芯片连接- 倒装芯片凸点)和C5(焊球)机电接口中的RoHS焊点,SiP设计的可靠性是一个重大的工程挑战。Te2v不断开发新技术,通过热机械分析,并考虑诸如焊料蠕变和粘塑性等的非线性行为,快速并准确地预测产品的翘曲和板级的可靠性(见图11)。

图11 - PS640 在室温组装后发生的封装翘曲的50 倍放大图

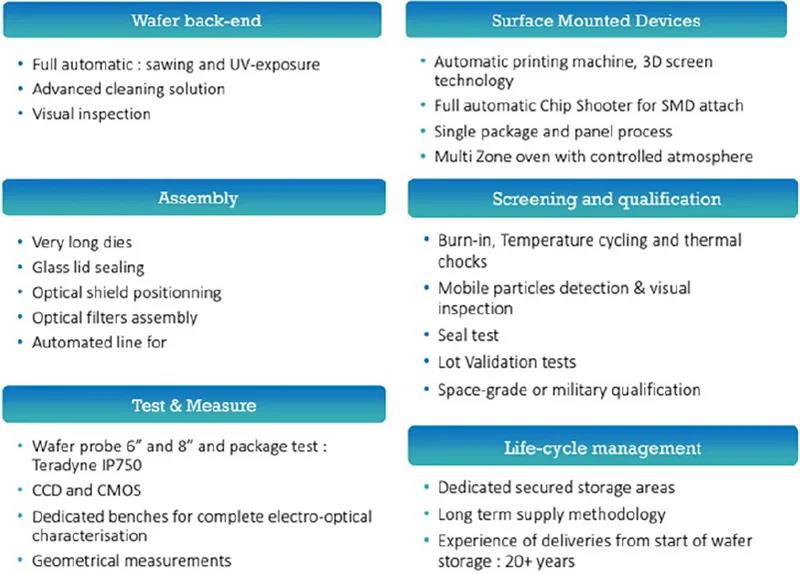

具体的设计和组装服务还包括:定制产品、中/低用量产品、高可靠/高端产品、QML-V/QML-Y认证以及宇航认证(参考图12中的技术总结):

图12 - Te2v 的高级组装技术,可用于SIP 的组装

图13说明了Te2v的高级SiP焊线和倒装芯片组装技术。对于焊线,图13(上图)说明了满足不同半导体类型(Si、GaN、GaAs等)和封装类型的最新发展所需的众多组装技术。随着新一代的半导体和封装的发布,必须开发新的焊线技术,以满足性能的要求。焊线大约占所有电子封装组装(包含flash存储器和传感器等)的三分之二。对于一些硅节点,如MEMS传感器,无法使用先进的倒装芯片互联技术。在这些情况下,焊线依然具有成本和可靠性方面的优势。

图13 - Te2v 的高级焊线(上)和倒装芯片(下)技术,可用于SIP 的组装

倒装芯片技术(也如图13所示)基于半导体顶部形成的一系列凸起或铜柱。倒装芯片的流程和传统IC的制造类似,只需要增加几个步骤。在制造过程接近尾声时,对焊盘进行金属化或焊料预处理,使其更容易焊接。在最后的晶圆流程中,焊接凸起会在晶圆顶部的芯片焊盘上形成,然后像往常一样从晶圆上切下芯片。为了将芯片安装在外部电路(SiP电路板和/或另一个芯片或裸片)上,需要翻转芯片使其顶部朝下,并使它的焊盘与外部电路的焊盘对齐,然后进行回流焊(通常使用热超声焊接或回流焊接),以使它们互相连接。这会在芯片电路和底部之间留下了一个很小的空间。在很多情况下,需填充电气绝缘的粘合剂,以保证更强的机械连接,并产生热桥,确保焊点不会由于芯片和系统的其他部分的热量不同而受到应力。这些填充物减少了芯片和板子之间的热膨胀系数的不匹配带来的影响,防止应力集中于焊点,防止器件过早失效。倒装芯片技术与焊线技术不同,在焊线技术中,芯片被简单地安装,然后用线将芯片的焊盘和外部电路连接起来。

在性能生命周期内,SiP可降低特定产品和系统的总体成本,特别是与其他设计选项(如SoC等)相比时。SiP可在产品生命周期的各个阶段减少总体的系统开发成本,如:

1. 降低工程成本:在工程开发时间、材料和上市时间方面显著降低设计的难度。

2. 降低PCB成本:简化特定器件的开发和使用(利用COTS或定制半导体)。

3. 降低组装成本:将多个器件集成到一个封装里,可在系统整体制造流程中显著降低成本。

4. 降低供应链成本:简化供应链。来自不同制造商的多个器件可被单个SiP取代,这样只需管理较少的供应商和器件,可大大简化供应链。

5. 验证:子系统和系统级的测试和认证。

Te2v的高级SiP设计和组装服务成为所有细分市场和产品类型的“一站式商店”(参见图14)。简单来说,Te2v不但为宇航级的应用提供设计、组装和认证服务,也面向其他所有的细分市场、应用和质量等级。

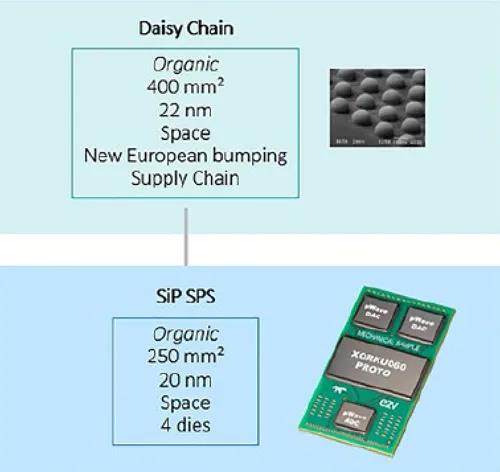

最后,随着高级系统的发展进入下一个十年,SiP技术已成为减少门长度、减小半导体尺寸的关键要素。随着越来越大的SoC逐渐成为SiP包含的众多器件之一,使用有机基材和封装材料进行可靠组装(焊线或倒装芯片)的技术需要大量的技术投资。当前,Te2v正准备在未来几年内实现这类技术的进步,所有的技术研发都由ESA赞助。

当前,数据转换系统的设计师正在经历半导体工艺选择(和几何尺寸)、电路小型化需求以及不断增加的开发成本等关键设计参数的挑战。此外,高级系统的开发可以使用越来越先进的ADC、DAC、微处理器和存储器件。在工业、医疗、航空电子、仪器仪表、通信、军事和宇航应用领域,一个系统设计的问题一直存在,即如何在模拟电路和数字电路之间取得平衡,以实现最大的软件/系统灵活性(从传感器到计算机输入/输出)。现在,高级SiP(系统级封装)技术的发展在所有的细分市场和应用中推动了数据转换系统的设计从硬件中心到软件中心的变革。Teledyne e2v的SiP设计、开发和组装的专业技术革新了系统级设计,实现了最大的灵活性和多任务的能力。Teledyne e2v拥有超过40年的RF、混合信号和数字处理应用的封装设计经验,其最先进的SiP设计和组装技术(焊线、倒装芯片、有机封装等)将帮助系统设计师实现高频直接RF数据转换系统平台的最高性能和最大价值。