长期以来,多芯片封装(MCP)满足了在越来越小的空间里加入更多性能和特性的需求。很自然地就会希望存储器的MCP能够扩展到包含如基带或多媒体处理器等ASIC。但这实现起来会遇到困难,即高昂的开发成本以及拥有/减小成本。如何解决这些问题呢?层叠封装(PoP)的概念逐渐被业界广泛接受。

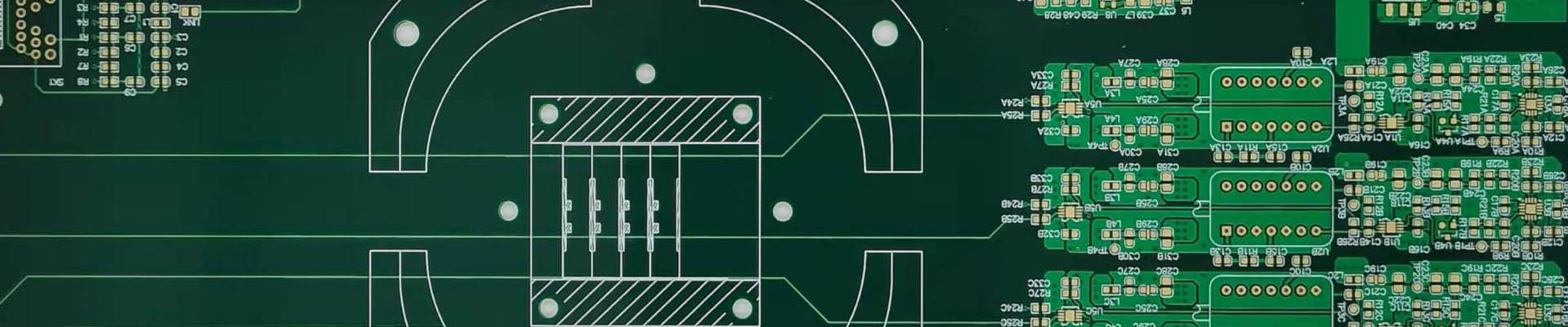

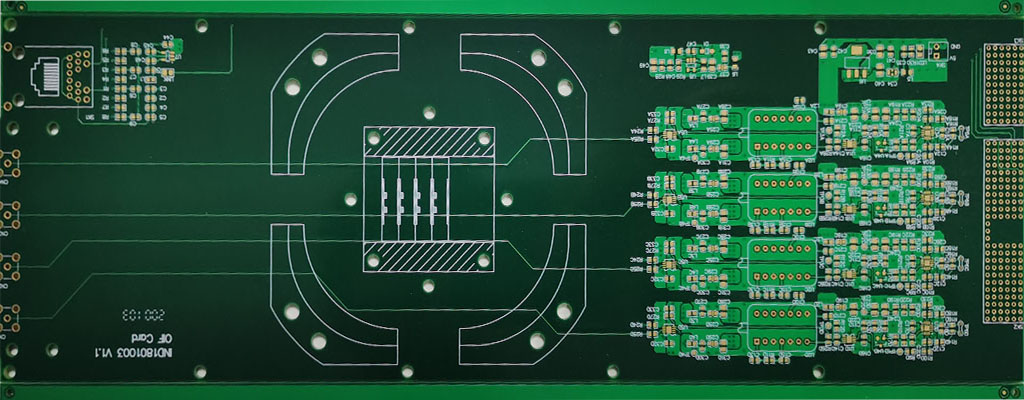

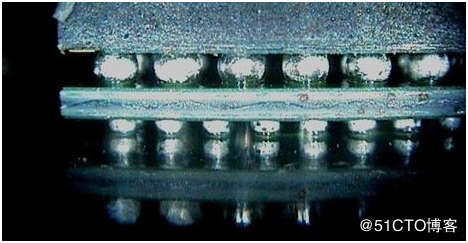

PoP(Packaging on Packaging),即堆叠组装,又称为叠层封装。POP采用两个或两个以上的BGA(球栅阵列封装)堆叠而成的一种封装方式。一般POP叠层封装结构采用了BGA焊球结构,将高密度的数字或或混合信号逻辑器件集成在POP封装的底部,满足了逻辑器件多引脚的特点。PoP作为一种新型的高集成的封装形式,主要应用在现代的智能手机、数码相机等便携式电子产品中,作用非常广泛。

MCP是在一个塑料封装外壳内,垂直堆叠大小不同的各类存储器或非存储器芯片,是一种一级单封装的混合技术,用此方法节约小巧印刷电路板PCB空间。

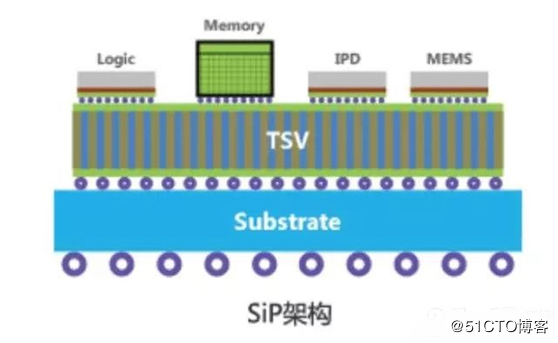

SIP从架构上来讲, SiP 是将多种功能芯片,包括处理器、存储器等功能芯片集成在一个封装内,从而实现一个基本完整的功能。SiP从终端电子产品角度出发,不是一味关注芯片本身的性能/功耗,而是实现整个终端电子产品的轻薄短小、多功能、低功耗,在行动装臵与穿戴装臵等轻巧型产品兴起后, SiP需求日益显现。

SoC的基本概念是在同一片裸片上集成更多的器件,以达到减少体积、增强性能和降低成本的目的。但在项目生命周期非常短、成本要求非常苛刻的移动电话市场,SoC解决方案有很大的局限性。从存储器配置的角度看,不同类型的存储器需要大量逻辑,掌握不同的设计规则和技术是非常大的挑战,会影响开发时间和应用所要求的灵活性。

SOC和SIP

SoC 与 SIP 是极为相似,两者均将一个包含逻辑组件、内存组件,甚至包含被动组件的系统,整合在一个单位中。 SoC 是从设计的角度出发,是将系统所需的组件高度集成到一块芯片上。 SiP 是从封装的立场出发,对不同芯片进行并排或叠加的封装方式,将多个具有不同功能的有源电子元件与可选无源器件,以及诸如 MEMS 或者光学器件等其他器件优先组装到一起,实现一定功能的单个标准封装件。

从集成度而言,一般情况下, SoC 只集成 AP 之类的逻辑系统,而 SiP 集成了AP+mobileDDR,某种程度上说 SIP=SoC+DDR,随着将来集成度越来越高, emmc也很有可能会集成到 SiP 中。从封装发展的角度来看,因电子产品在体积、处理速度或电性特性各方面的需求考量下, SoC 曾经被确立为未来电子产品设计的关键与发展方向。但随着近年来 SoC生产成本越来越高,频频遭遇技术障碍,造成 SoC 的发展面临瓶颈,进而使 SiP 的发展越来越被业界重视。

从MCP到PoP的发展道路

在单个封装内整合了多个Flash NOR、NAND和RAM的Combo(Flash+RAM)存储器产品被广泛用于移动电话应用。这些单封装解决方案包括多芯片封装(MCP)、系统级封装(SiP)和多芯片模块(MCM)。

在体积越来越小的移动电话中提供更多功能的需求是MCP发展的主要驱动力,然而,开发既能增强性能又要保持小型尺寸的解决方案面临着艰巨的挑战。不仅尺寸是个问题,性能也存在问题,如当要与移动电话中的基带芯片组或多媒体协处理器配合工作时,要使用具有SDRAM接口和DDR接口的MCP存储器。

PoP堆叠封装是一种以较高集成度实现微型化的良好方式,在堆叠封装中,封装外封装(PoP)对封装行业越来越重要,特别是手机方面的应用,因为这种技术可堆叠高密度的逻辑单元。

POP封装的优点:

1、存储器件和逻辑器件可以单独地进行测试或替换,保障了良品率;

2、双层POP封装节省了基板面积, 更大的纵向空间允许更多层的封装;

3、可以沿PCB的纵向将Dram,DdramSram,Flash,和 微处理器进行混合装联;

4、对于不同厂家的芯片, 提供了设计灵活性,可以简单地混合装联在一起以满足客户的需求,降低了设计的复杂性和成本;

5、目前该技术可以取得在垂直方向进行层芯片外部叠加装联;

6、顶底层器件叠层组装的电器连接,实现了更快的数据传输速率,可以应对逻辑器件和存储器件之间的高速互联