当前,3D封装技术正席卷半导体行业,引起整个行业的广泛关注。如今摩尔定律趋缓,而3D封装技术将会取而代之成为新的发展方向。因此各家公司一直在大力投资3D封装技术,以便占据良好的竞争优势。

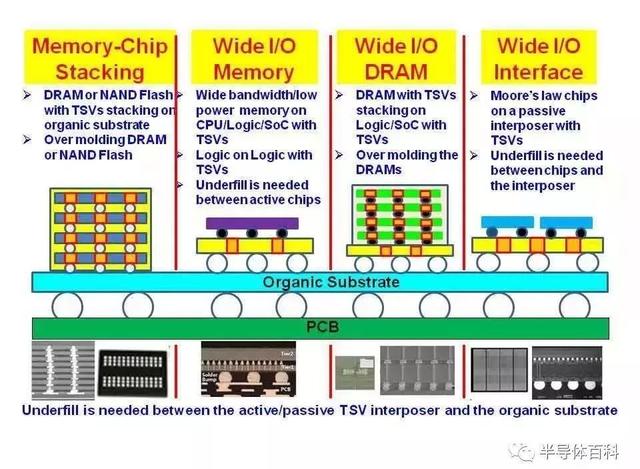

图1展示了3D封装技术的潜在应用和大批量制造(HVM)。基本上它可以分为4类:存储芯片堆叠,宽 I / O储存芯片(或逻辑芯片堆叠),宽I / O DRAM和宽 I / O接口(或2.5D集成电路)。

图1:Potential application and high-volume manufacturing of 3D IC integration

存储芯片堆叠

图1最左端图示是Samsung公司在2006年发布的最简单的存储芯片堆叠示意图。这些芯片可能是DRAM(动态随机存取存储器)或I/O数量少于100的NAND闪存(确切地说是78个)。很重要的一点是,这种存储芯片附在有机基板上,即使采用八个芯片堆叠,它们的总厚度(560μm)仍小于普通芯片的厚度。遗憾的是,由于成本问题和引线键合技术的竞争,使用TSV(Through Silicon Via,硅通孔技术)的存储器芯片堆叠目前尚未针对消费产品进行批量生产。目前,Samsung正在开发的下一代服务器产品,很可能考虑采用DDR4(双信道四次同步动态随机存取内存)SDRAM(同步动态存储器)。

宽I / O存储或逻辑堆叠

图1左侧第二个图示显示了一个宽I / O存储器,它由低功耗和宽带存储器组成,通常具有数千个接口引脚。该I / O存储器被称为有源转接板,能够被具有TSV结构的CPU /logic或SoC支持,连接在有机基板上。由于智能手机等移动产品的需求,诸如Samsung公司等已经制造发布该样品。不幸的是,设计公司的基础设施(包括制定行业标准,商业模式和提出有竞争力的价格)都需要时间准备,还未完善。逻辑堆叠便属于这一类。

宽I / O DRAM(HMC)

图1右侧的第三列图示显示了一个宽I / O DRAM。Samsung已经至少三年发表了有关此主题的论文,最后一次,在2011旧金山召开的IEEEISSCC会议上,Samsung展示了一个带有TSV结构的主控制器逻辑芯片(或SoC)上有两个DRAM的样品,该芯片被称为有源转接板。对于这种DRAM,硅通孔和接口引脚的数量略多于1000个。JEDEC标准将此结构定义为在四个通道中具有1200个I/ O引脚(http://www.jedec.org/)。该宽I / O DRAM模块附在有机基板上。近日,由Micron,Samsung,Altera,ARM,Hewlett-Packard,IBM,Microsoft,Open-Silicon,SKHynix和Xilinx等公司组成的HybridMemory Cube(HMC)联盟宣布,将在今年年底前向公众发布一个行业规范。该规范主要针对高性能网络、工业、测试和测量应用。IBM还建议将此用于高端服务器。

无源转接板的宽I / O接口(2.5DIC封装)

图1最右侧图示显示了用于路由/通信/下一代服务器/高性能应用的宽I / O接口。摩尔定律芯片如memory/ ASIC / CPU / ...... 的I/ O数量在几百到几千之间,他们由一片具有TSV和再分配层(RDL)的硅片相连。图1最右侧示例从Xilinx[3-6]的论文中截取,其中FPGA(现场可编程逻辑门阵列)由TSMC的28nm工艺技术制造,转接板为65nm工艺制程。顶部有四个RDL,可让这四个FPGA在很短的距离内相互通信。

下面将对这四组潜在应用的技术流程和3D IC集成技术的HVM进行讨论。HMC中存储芯片堆叠和DRAM的厚度≤50μm。此外,有源和无源转接板厚度≤200μm。本文仅仅考虑芯片-晶圆(C2W)键合(不探讨材料和设备等)。尽管EDA(electronicdesign automation,电子设计自动化)非常重要,本文也不对其进行讨论。同样,像Samsung和TSMC这样想要成为技术的纵向一体化公司(即做到这一切),也不在本文讨论范围。

TSV时代之前的技术流程

在TSV时代之前的技术流程已经被很好地定义和理解。TSV时代之前技术流程描述如下:

FEOL(前段)。这是IC制造的第一部分,其中对各个器件(例如晶体管或电阻器)进行了图形化。该过程是从裸晶片到(但不包括)金属层的沉积。FEOL通常在fab中进行。

BEOL(后段)。这是有源器件在晶片上布线连接的制造过程。该过程从第一层金属开始到具有钝化的PAD。它还包括绝缘体和金属接触,称为MOL(中段)。术语“MOL”很少使用,此工艺常包含在BEOL中。同样,BEOL通常在fab中完成。

OSAT(外包半导体组装和测试)。当钝化后的晶片从fab接收后,将进行电路测试/凸点/减薄/划片/引线键合/倒装芯片/注塑成型/植球/成品测试。

TSV时代的技术流程

TSV时代技术流程主要分三部分讨论:

A)谁制造TSV?

B)谁负责MEOL?

C)谁执行关键步骤(包括FEOL,MOL,BEOL,TSV,MEOL,组装和测试)以及谁将负责完成图1所示的四种3D封装制程。

A) 谁制造TSV

以下TSV制造工序将会对多种因素产生影响,因此必须予以区分。

Via-First工艺制备TSVs:TSVs在FEOL工艺之前制造,并且只能由fab完成。因为器件的制备(例如晶体管)比TSV重要得多,因此很难在fab中完成TSV工艺。

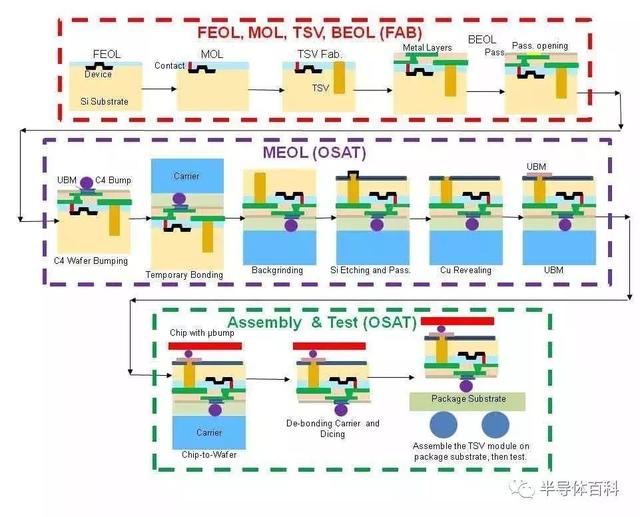

Via-Middle工艺制备TSVs:TSVs在FEOL(例如晶体管)和MOL(例如金属接触)之后,在BEOL(例如金属层)之前制备。在这种工艺下,由于TSV制造过程介于它们之间,因此BEOL工艺不再包含MOL(图2和图3)。由于工艺流程和设备的兼容性,通过Via-Middle工艺制备的TSV通常也由fab完成。

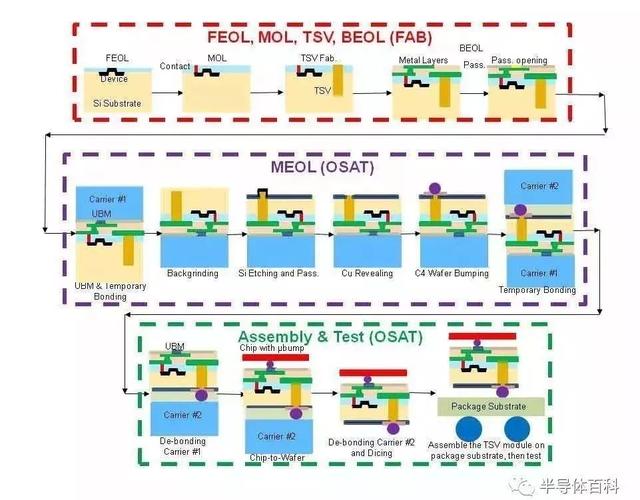

图2:Critical steps and ownerships for (face-to-back) wide I/O memory using the TSVvia-middle fabrication process.

Via-Last工艺制造的TSVs(从晶圆正面):在FEOL,MOL和BEOL工艺之后制造TSV。迄今为止,没有一篇论文发表过相关报道。

Via-Last工艺制造TSVs(从晶圆背面):在FEOL,MOL和BEOL工艺之后制造TSV。CMOS图像传感器就是一个例子。但严格来说,CMOS图像传感器不是3D IC集成工艺的示例。对于CMOS器件,Leti等人发表的论文提供了唯一可信的证据。但是,由于工艺和技术问题,应避免使用Via-Last工艺制造TSV(从晶圆背面)直到这些问题得到解决。

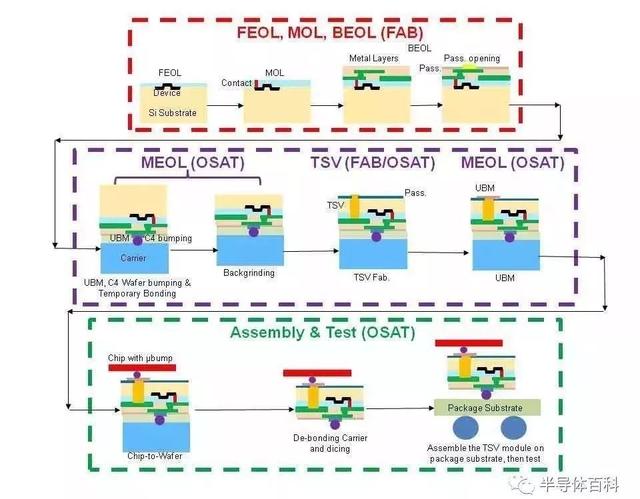

图3:Critical steps and ownerships for (face-to-face) wide I/O memory using the TSVvia-middle fabrication process.

基于上述讨论,似乎对应用于3D IC封装技术有源器件晶片,使用via-middle工艺制造TSV更为理想。此外,由于fab已经拥有相关设备,具备相关专业知识技能,TSV应由fab厂制造,并且制造TSV的成本不到制造(≤32nm)器件晶片的成本的5%!

对于无源TSV转接板又如何呢:当业界定义用于3D IC封装的TSV流程时,还没有无源转接板。此外,由于无源转接板中没有有源器件,因此它们不适用上述提到的的任意工艺!

谁想要生产无源转接板TSV:fab和OSAT都希望生产!它取决于版图,设计和制造能力,尤其是RDL的线宽和间距。通常,OSAT可以实现几微米的线宽和间距。否则,它就应该由fab生产。

B)谁负责MEOL工艺

对于HMC中DRAMs和存储.芯片堆叠的厚度,以及考虑到有源和无源转接板的厚度,所有制造的TSV都是盲孔。盲孔TSV工艺之后是焊料凸点/临时粘合/减薄/ TSV露点/薄晶圆支撑转移/剥离/清洁,这些过程统称为MEOL(生产线的中端)。对于这项工作,除了纵向一体化公司公司(例如,TSMC和Samsung集团),最好由OSAT完成MEOL流程。

C)量产3D封装的关键步骤分工

C.1)TSV Via-Middle工艺制造宽I / O存储器(面对背):图2显示了该工艺的关键步骤和制备工厂。在FEOL(用于对器件进行图案化)和MOL(用于形成金属接触)之后,通过五个关键步骤制造TSVs,即通孔制造。通孔是由深反应等离子蚀刻形成的(DRIE),电介质是通过等离子体增强化学气相沉积的(PECVD),阻挡层和种子层通过物理气相沉积(PVD),使用电镀铜填充和化学机械抛光(CMP)去除覆盖的铜。这些步骤之后是金属层的堆积,最后是钝化/开口(BEOL)。所有这些步骤都应在fab中完成。

MEOL首先通过凸点下金属化(UBM)以及使用C4(普通晶圆凸点)焊接到整个晶片上。然后用粘合剂将TSV晶片临时粘合到载体晶片上。再将TSV晶片反向研磨至铜填充TSV顶部几微米。接着进行硅干法蚀刻,直到铜填充TSV顶部以下几微米。之后,在整个晶片上进行低温隔离SiN / SiO2沉积。然后使用CMP去除SiN / SiO2和Cu以及Cu填充TSV(Cu显露)的晶种层。最后,在铜填充TSV的顶部制备UBM。所有这些步骤应由OSAT完成。

分别用微小的焊料凸点或带有焊帽的Cu柱对存储器晶片进行微凸点处理。然后将晶片切成带有微凸点/Cu柱的单个芯片。这些步骤也应由OSAT完成。

接下来是芯片到晶圆(C2W)的键合,如微凸点存储芯片(通过自然回流或热压缩)与TSV晶片键合。在C2W面对背键合之后,载体晶片从TSV晶片上剥离下来。随后将TSV晶片切成单独的TSV模块。将该TSV模块(自然)回流焊接到封装基板上,进行测试。所有这些C2W键合,切割,组装和测试步骤均应由OSAT完成。

C.2)TSV Via-Middle工艺制造宽I / O存储器(面对面):FEOL,MOL,TSV和BEOL过程与TSV via-middle(面对背)工艺流程完全相同。但是,接下来的工艺流程是不同的。TSV晶片不是在UBM后使用C4技术焊接到载体晶片上,而是临时连接到载体#1。然后,对TSV晶片进行背面研磨,并完成Cu显露和UBM。这些步骤之后进行C4工艺,并临时粘合到第二个载体#2。然后,将载体#1从TSV晶片上剥离下来,并进行C2W(面对面)键合。在C2W键合之后,将载体#2从TSV晶片上剥离。随后将TSV晶片切成单独的TSV模块。将该TSV模块回流焊接到封装基板上,然后进行测试。关键步骤如图3所示。

C.3)TSV Via-Last工艺(从背面)制造宽I / O存储器(面对背):图4显示了该工艺的关键步骤和制备工厂。在FEOL(对器件进行图案化),MOL(形成金属接触)和BEOL(构建金属层以及钝化/开口)之后进行UBM制备和C4工艺。然后,将该结构临时和载体晶片键合。再进行背面研磨,TSV制造和钝化/开口以及UBM。

接下来是C2W面对背键合,将载体晶片从TSV晶片上剥离,然后将TSV晶片切成单独的TSV模块。再将该TSV模块回流焊接到封装基板上进行测试。

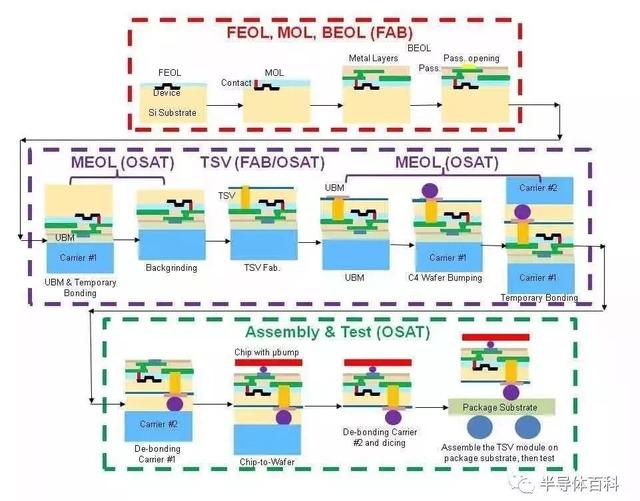

图4: Critical steps andownerships for (face-to-back) wide I/O memory using the TSV via-last from thebackside fabrication process.

C.4)TSV Via-Last工艺(从背面)制造宽I / O存储器(面对面):FEOL,MOL和BEOL工艺与和面对背TSV via-last(从背面)过程完全相同。但是,对于面对面情况而言,在UBM步骤之后,器件晶片临时粘合到载体#1如图5所示。然后,对背面进行背面研磨,TSV加工和钝化/开口处理。在这些过程之后,制备UBM,进行C4工艺,并临时粘合至载体#2。然后完成与载体#1的剥离。

图5:Critical steps and ownerships for (face-to-face) wide I/O memory using the TSVvia-last from the backside fabrication process.

完成上述过程后,接下来进行C2W面对面粘合。在C2W键合之后,载体#2晶片从TSV晶片上剥离并切割成单独的TSV模块。TSV模块将焊接在封装基板上,然后进行测试。

从图4和图5可以看出,TSV既可以由fab制造也可以由OSAT制造。然而,由于工艺流程的关系,fab实现这一目标的机会非常渺茫。(一旦晶片离开fab由OSAT接收处理,晶片几乎不可能再回到fab进行进一步处理。)同样,由于技术问题,例如击中晶片中各种嵌入式对准目标, x,y和z方向(要使晶片顶侧上的金属层对齐以及从背面形成的TSV定位),这对于OSAT来说也是非常具有挑战性的。因此,在解决这些问题之前,应避免使用TSV via-last(从背面)制造工艺

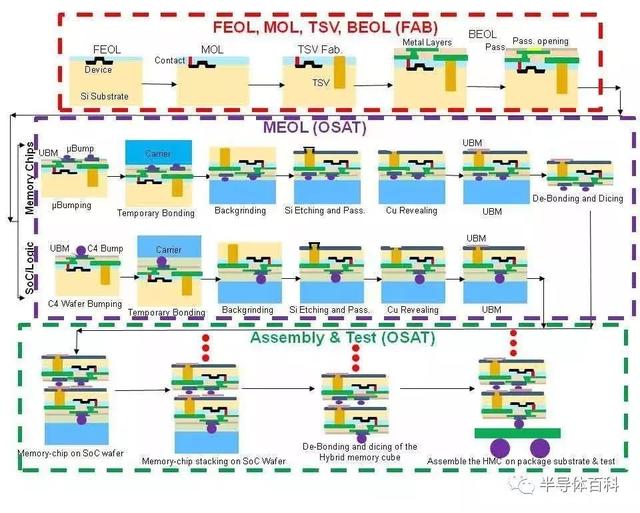

C.5)TSV Via-Middle工艺制造宽I / O DRAM:在DRAM和SoC/logic晶片的FEOL,MOL,TSV和BEOL之后,SoC /logic晶圆将按照图2(C.1)所示的面对背,或图3 (C.2)面对面工艺步骤进行操作。对于DRAM,首先要进行UBM,然后是整个晶圆的微凸点工艺。在这些过程之后,将临时粘合到载体晶片,进行背面研磨减薄,铜暴露和UBM。再依次进行载体晶圆剥离和将TSV DRAM晶圆切成单个TSV DRAM芯片,如图6所示。

图6:Critical steps and ownerships for wide I/O DRAM using the TSV via-middlefabrication process.

下一个过程是C2W(DRAM芯片到SoC/Logic晶片)键合(例如,2堆叠,4堆叠,6堆叠或8堆叠)。在C2W键合之后,载体晶片从SoC /Logic晶圆剥离并切割成单独的混合封装体(DRAM堆叠+SoC /Logic)。这些步骤之后,将二次成型的混合存储立方体组装在封装基板上,然后进行测试。

C.6)TSV Via-Middle工艺制造宽储存器芯片堆叠:存储器芯片(DRAM或NAND闪存)堆叠的关键步骤和制备工厂与宽I / O DRAM情况完全相同,如图6(C.5)所示。然而,不同于宽I / O DRAM情况下采用C2W键合,内存芯片堆叠是通过首先堆叠各个TSV芯片然后将它们连接到封装基板上并且采用灌胶成型来实现的。在这些步骤之后,将TSV存储器芯片堆叠模块连接到印刷电路板上,例如双列直插式存储器模块(RDIMM)。

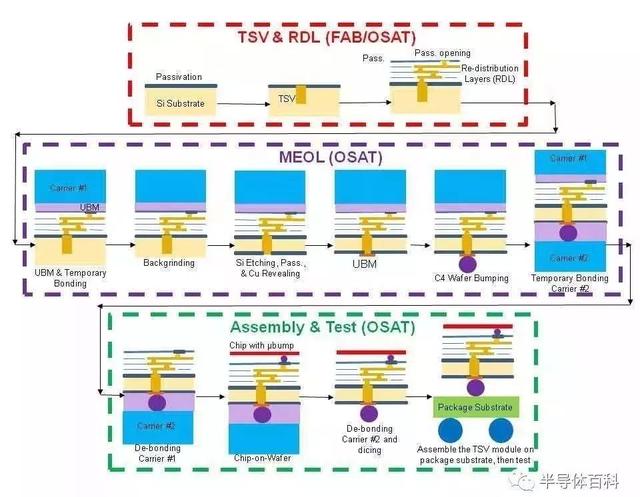

C.7)2.5D IC封装技术制备TSV / RDL无源转接板:图7显示了关键步骤和制备工厂。在一块dummy硅(无有源器件)上沉积钝化层之后,制作TSV,构建RDL并进行钝化/开口。在UBM之后,将TSV晶片临时粘合到载体#1。然后进行背面研磨,硅蚀刻,低温钝化和铜暴露。其后,完成UBM,C4工艺以及与载体#2的临时粘合。不带TSV的器件晶圆分别用微焊料凸点或带有焊帽的Cu柱对存储器晶片进行微凸点处理。再将器件晶片切成有微凸点/Cu柱的单个芯片。

图7:Critical steps and ownerships for 2.5D IC integration with a TSV/RDL passiveinterposer.

接下来要完成的工作是剥离载体#1,进行C2W键合(器件芯片与TSV晶片的键合)。C2W键合之后,载体#2被剥离并且TSV晶片被切割成单独的TSV模块。最后,TSV模块可以组装在封装基板上进行测试。图7中可以看出TSV和RDL既可以由fab制造也可由OSAT制造。它取决于布局,设计和制造能力,尤其是RDL的线宽和间距。通常,OSAT可以完成几微米的线宽和间距。否则,它应该由fab完成。除了像TSMC这样的纵向一体化公司希望完全在内部进行晶圆级封装工艺(CoWoS)之外,大多数设计公司更偏向由fab(例如,UMC和GlobalFoundries)来制造盲孔TSV以及无源转接板的RDL。然后,fab将未完成的“ TSV转接板”移交给OSAT进行MEOL(焊料凸点/临时键合/薄晶圆支撑转移/背面研磨/ TSV显露/剥离/清洁),组装和测试。对于未完成的TSV器件晶片也是如此。